随着芯片技术的不断发展,特别是芯片工艺水平的提升,芯片规模越来越大,这也为芯片逻辑功能验证带来了很大的挑战。如何保证产品上市时间(TimetoMarket),快速完成功能验证和达成较高的覆盖率,已成为验证进程管理的棘手问题。本文主要跟小伙伴们聊一聊智能跟踪SoC验证进度的方法。

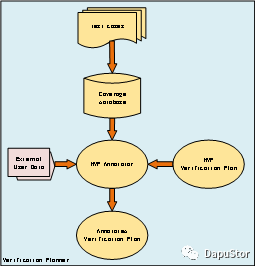

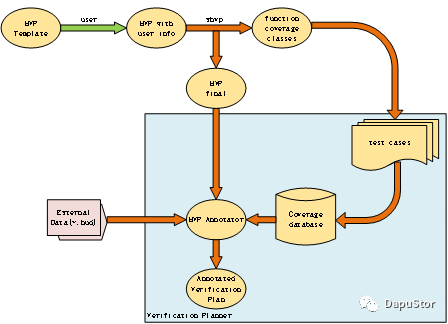

EDA工具两大巨头Synopsys和Cadence都有自己的验证计划工具,分别是Synopsys公司的VerificationPlanner和Cadence的vmanager,两者各有千秋。今天我们主要针对的是Synopsys的层次化验证计划工具。该工具采用自定义的描述语言HVP(Hierarchical Verification Plan),层次化地描述验证计划,并在验证计划的实施过程中,通过测试数据结果,反标回验证计划,根据产生相应的状态报告,可以有效地追踪验证的整个进程。其基本流程如图1所示。

图1:HVP基本流程

该流程需要验证人员首先编写验证计划,验证计划通常需要Synopsys提供的另一种工具Verdi或DVE编辑HVP文件,或者直接采用office工具Excel编辑XML格式文件。在项目验证计划中会包含测试计划、功能覆盖率计划、断言覆盖计划、代码覆盖率计划等等。下面将介绍HVP是如何编写来映射我们上述提到的各种计划的。

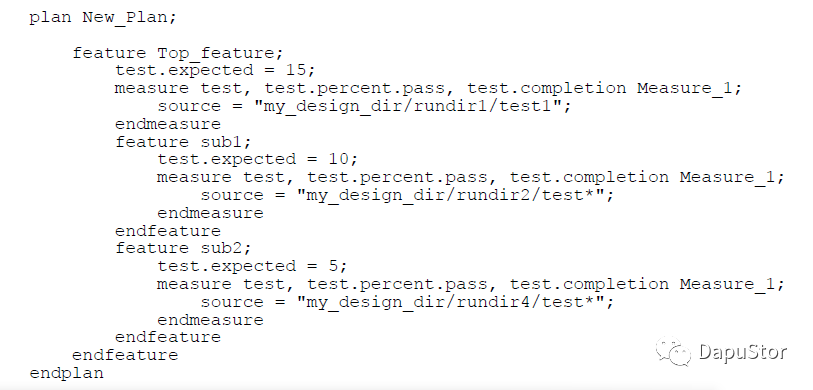

验证计划有自己的.hvp格式,如图2 HVP描述示例。该文件可以比较容易的通过Verdi生成模板。

图2:HVP描述示例

当然,如果你比较钟爱Excel,那么可以用命令将hvp计划文件转换成XML格式:

hvpgenxls–planmy_plan.hvp –lca

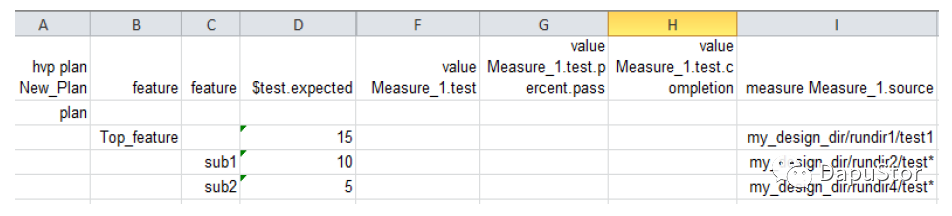

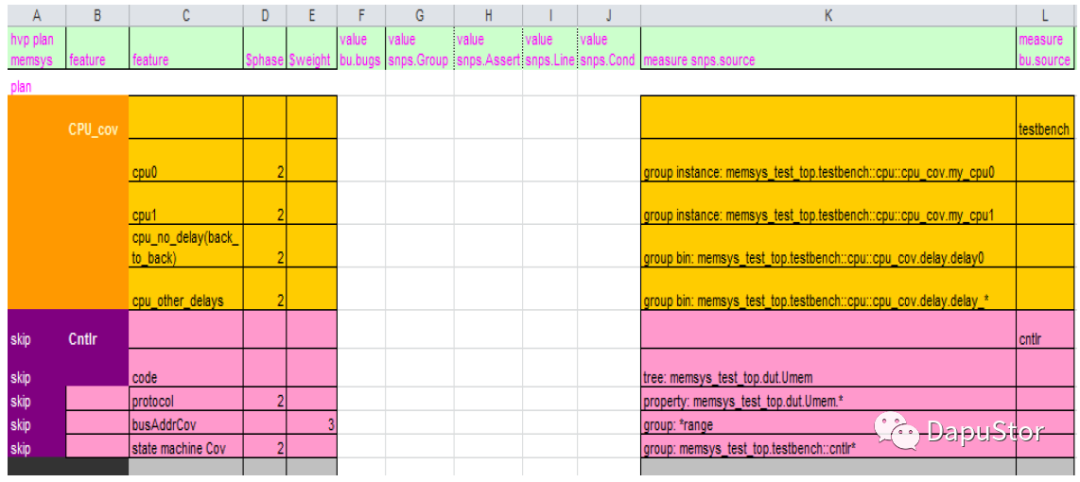

这样就可以用Excel打开生成的如my_plan.hvp.xml文件了,如图3所示。

图3:ExcelXML格式验证计划

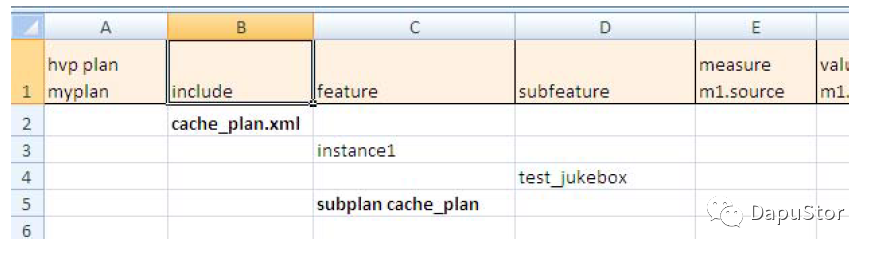

从图3中可以看出,测试项填在feature列,分层计划一方面就体现在feature是分级的,C列feature为B列的子feature。另一方面体现在plan可以include子plan,如图4中include列即为myplan包含了cache_plan。带有value关键字列表示测试项完成度情况,而带有measure关键字列则表示对应测试项如何衡量,也即我们所提的如代码覆盖率,功能覆盖率,断言覆盖率了。如图5中“measure snps.source”列中,group关键字表征功能覆盖率,property关键字表征断言覆盖率,tree关键字则表征代码覆盖率。

图4:包含子plan示例

图5:包含代码代码覆盖率、功能覆盖率和断言覆盖率的plan示例

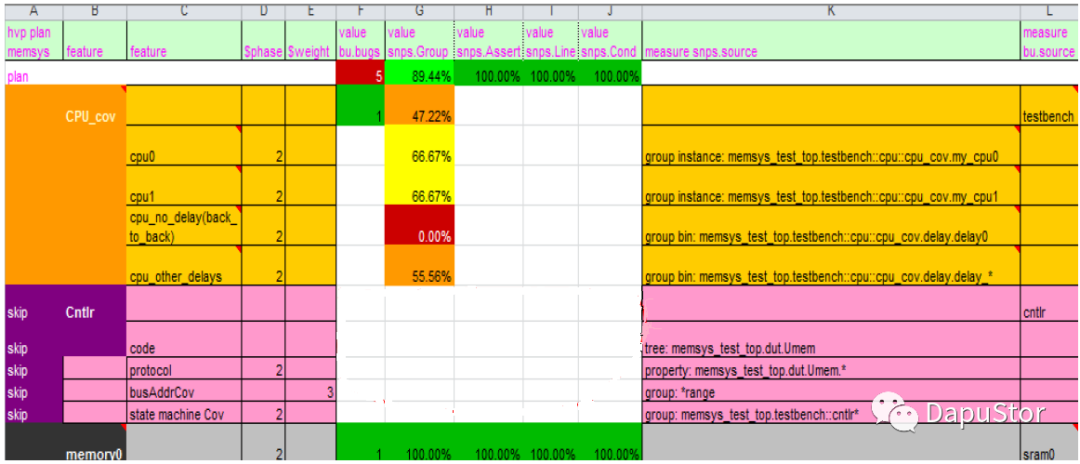

好了,我们的验证计划完成了,下一步就要开发测试用例并作回归测试。所有测试用例运行完成后,仿真工具VCS会收集这些覆盖率并输出数据库。此外,当然我们也希望会收集测试用例是pass还是fail的信息,作为反标信息的用户自定义输入信息。有了这些数据,通过反标工具就可以看到验证报告了,运行如下命令:

hvpannotate –plan my_plan.hvp.xml –dir *.vdb –userdata *.hud

可以得到my_plan.hvp.ann.xml文件,类似如图6所有的形式。

图6:反标后的hvp计划示例

写到这里,我们的验证工程师们确实被这种可视化的、自动化的验证计划管理惊艳到了。整个验证跟踪过程被自动化,既保证了跟踪的准确性,也避免了工程繁琐的管理和手工劳动。重要的一点是,老大再问起验得咋样了,我们就可以以数据说话:“老大,就一个功能覆盖点没覆盖到了,你看。”领导满意的点点头:“嗯,小伙子不错,年轻有为!”

但是,我们的工程师们也注意到了,填写功能覆盖率计划的时候,要从我们测试平台中找出covergroup或coverpoint的层次路径,如图5中的group instance和group bin。这个可麻烦了,有没有好的方法不去写层次路径,只写coveragegroup和coverpoint名呢?这个难不倒我们的技术牛们,他们创造了一个新的HVP流程,如图7所示。一个新的HVP模板如图8所示,让验证人员只需要填写class.covergroup[.coverpoint[.bin]]这样格式的命名来表征当前feature或子feature由哪个covergroup和coverpoint覆盖测试,然后运行我们开发的工具xhvp,可以输出最终的hvp文件和用Systemverilog语言描述的function coverage类声明文件了。通过上述的步骤,我们的技术牛把function coverage的代码都生成好了,对验证人员真是无比的体贴,大大减轻验证人员的负担。当然也大大提高验证评审的效率,从而加快项目验证进度。

图7:新的HVP流程

图8:HVP模板计划页示例

至此,这套大杀器介绍完了,它在我们的DPU600芯片验证中已经被完美地使用。作为DapuStor业内首创的智能存储SoC芯片,基于最新的12nm FinFET工艺,即有业内领先性能的SSD主控功能,还集成了可计算存储,机器学习等高大上的特性,同时还拥有强大的功耗管理,晶体管数接近亿级,这么多强大的功能,其验证复杂度可想而知,得益于我们的HVP流程, DPU600芯片的逻辑验证顺利完成,而且一次流片量产成功,基于DPU600产品也即将面世,敬请期待哦!

原文标题:芯片验证管理,也能自动跟踪!

文章出处:【微信公众号:大普微】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

芯片

+关注

关注

463文章

54410浏览量

469157 -

eda

+关注

关注

72文章

3143浏览量

183711

原文标题:芯片验证管理,也能自动跟踪!

文章出处:【微信号:dputech,微信公众号:DapuStor】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

沃虎电子:共模电感的参数解读与测试验证方法

Questa One 智能验证:释放人工智能在功能验证中的潜力

广州易显VGA卡设置进度条实验教程

在Linux ubuntu上使用riscv-formal工具验证蜂鸟E203 SoC的正确性

如何在e203 SOC中添加自定义外设

如何验证电能质量在线监测装置的抗干扰能力?

有哪些方法可以验证电能质量在线监测装置的稳定性?

有哪些方法可以验证备用电源续航测试方案的准确性?

利用超微型 Neuton ML 模型解锁 SoC 边缘人工智能

【HarmonyOS 5】鸿蒙中进度条的使用详解

同步电机在位置随动系统中跟踪误差的分析与研究

Veloce Primo补全完整的SoC验证环境

智能跟踪SoC验证进度的方法

智能跟踪SoC验证进度的方法

评论