目前很多应用都需要用到差分信号,包括驱动高速模数转换器(ADC)、通过双绞线电缆传输信号、调理高保真音频信号等。由于差分信号在特定电源电压下可以提供较大信号幅度,提高了对共模噪声的抑制能力,降低了二次谐波失真,因而实现了更高的信噪比。由于这一需求,我们需要将大多数信号链中的单端信号转换为差分信号。

目前的单端转差分电路一般分为3种:

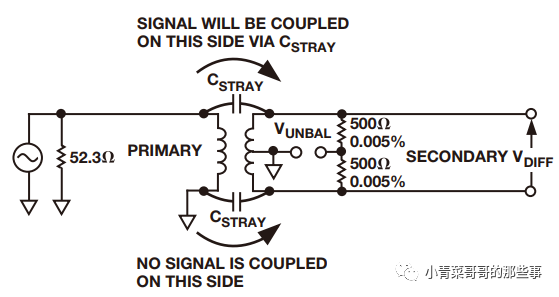

第1种是非平衡变压器电路,主要器件为一个变压器,如图1所示。

图1:非平衡变压器耦合

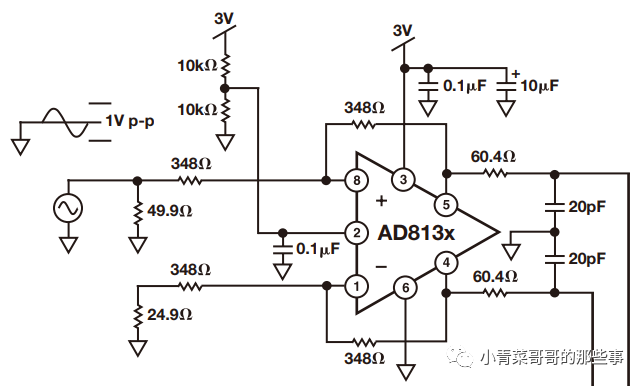

第2种是差分放大器电路,主要器件为一个差分放大器芯片,如图2所示。

图2:差分放大器耦合

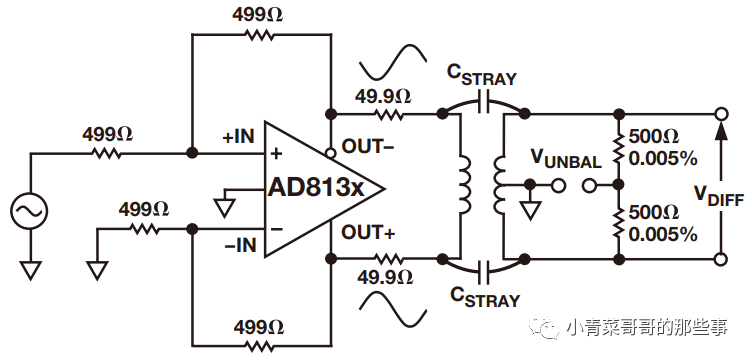

第3种是平衡变压器耦合,主要器件为一个差分放大器芯片和一个变压器,如图3所示。

图3:平衡变压器耦合

这3种单端转差分电路的优缺点暂且不提,有兴趣的朋友可自行去查资料。就小青菜哥哥所从事的脉冲信号采集工作而言,差分放大器电路是使用最适合、最广泛的方案。接下来小青菜哥哥就以ADI公司的单端转差分芯片ADA4927介绍一下差分放大器的设计步骤,这些设计步骤同样适用于其它类型差分芯片。

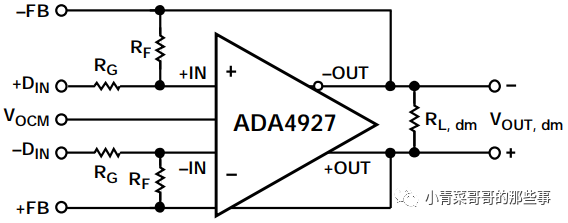

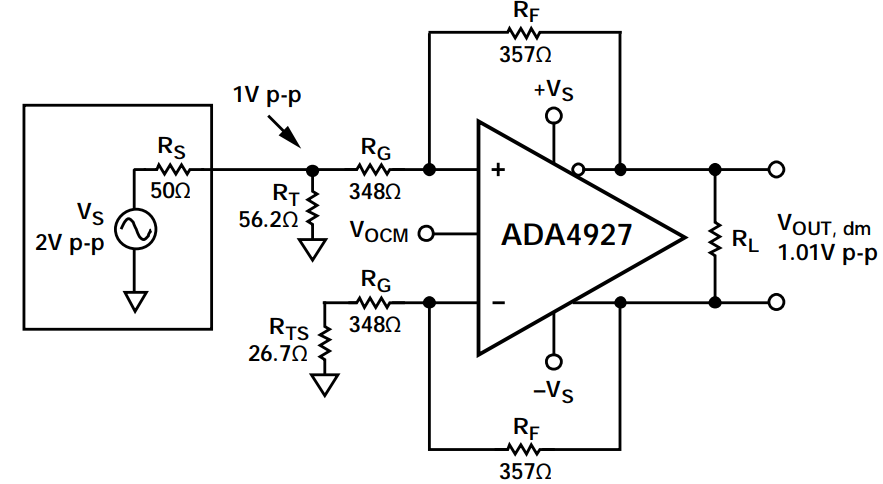

术语定义,如图4所示:

图4:电路术语定义

差分电压

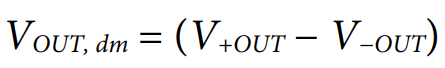

输出差分电压定义为:

输入差分电压定义为:

共模电压

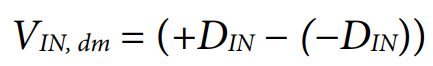

该电压一般由ADC提供即可,其大小可表示为:

差分增益

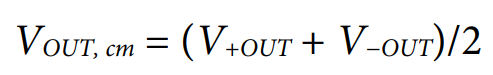

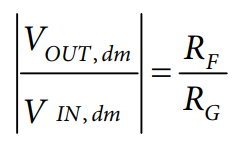

如果同相、反相端的输入电阻RG和反馈电阻RF相等,则有上述电路的差分增益为:

输入阻抗

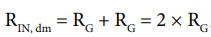

输入阻抗取决于差分放大器是由单端信号源驱动,还是由差分信号源驱动,对于差分输入信号(图5),两个输入端(+DIN和-DIN)之间的输入阻抗(RIN,dm)为:

图5:差分输入阻抗

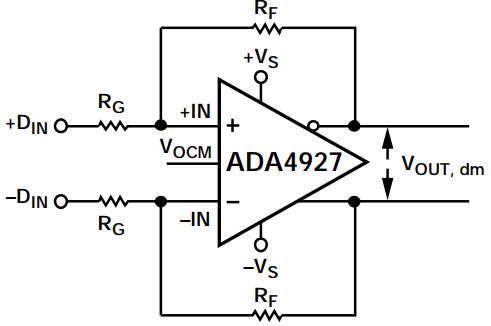

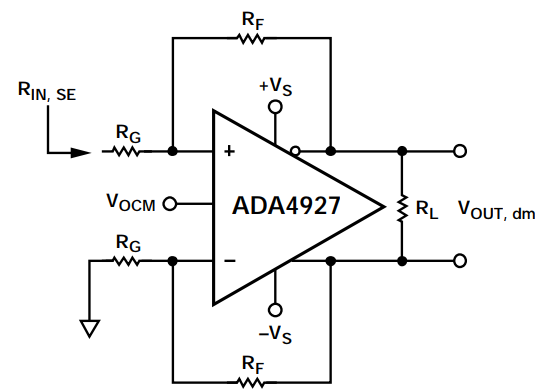

对于本篇的主题,即单端输入信号(图6),输入阻抗(RIN,SE)为:

图6:单端输入阻抗

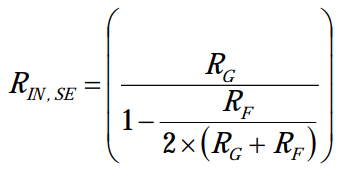

接下来我们看看如何将单端输入信号适当的端接到差分放大芯片ADA4927,设置的增益为1,RF=348Ω,RG=348Ω。通过端接输入电压为1VPP、源电阻为50Ω的输入源为例来说明操作步骤:

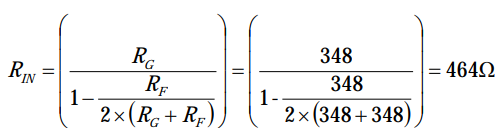

1,输入阻抗根据以下公式计算(图7):

图7:计算单端输入阻抗RIN

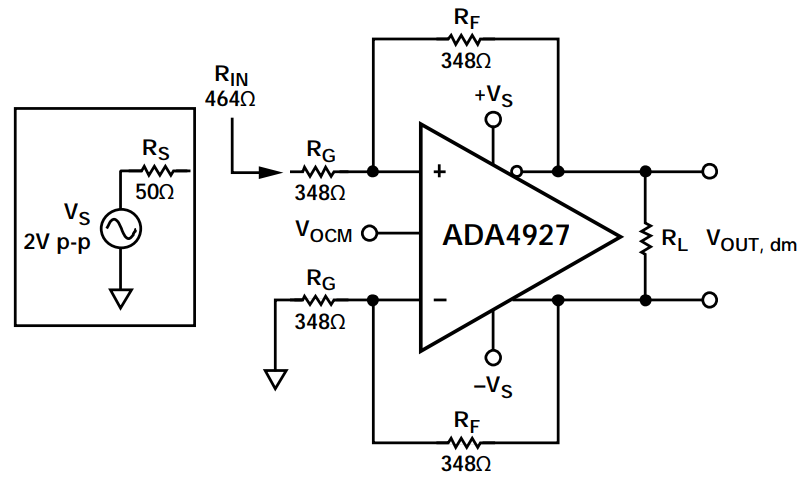

2,为了与50Ω源阻抗匹配(图8),计算端接电阻RT时使用RT||464Ω=50Ω。最接近的RT标准阻值为56.2Ω。

图8:添加端接电阻RT

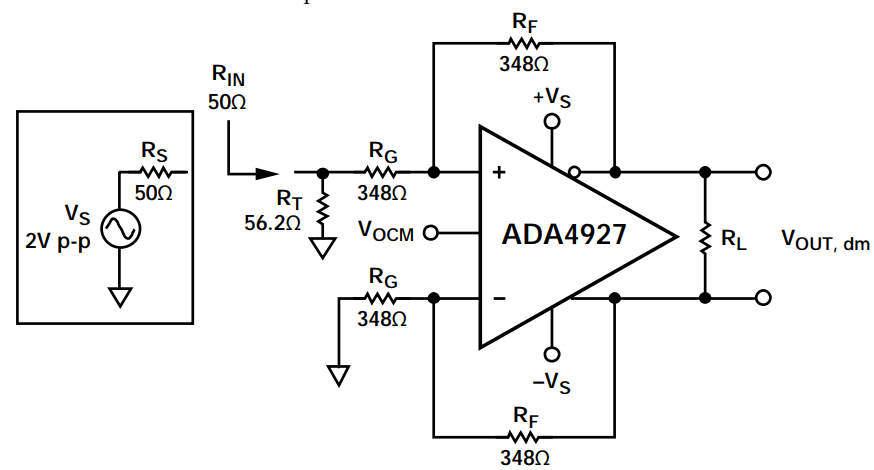

3,图8表明,由于添加了端接电阻RT,现在上反馈环路中的有效RG大于下环路中的RG。为了补偿增益电阻的不平衡性,需要在下环路添加一个校正电阻RTS,并使其与下环路的RG串联。RTS是源电阻RS和端接电阻RT的戴维南等效电路(图9),等于RS||RT。

图9:戴维南等效电路

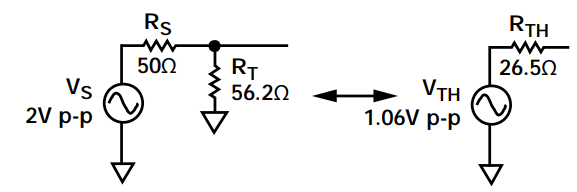

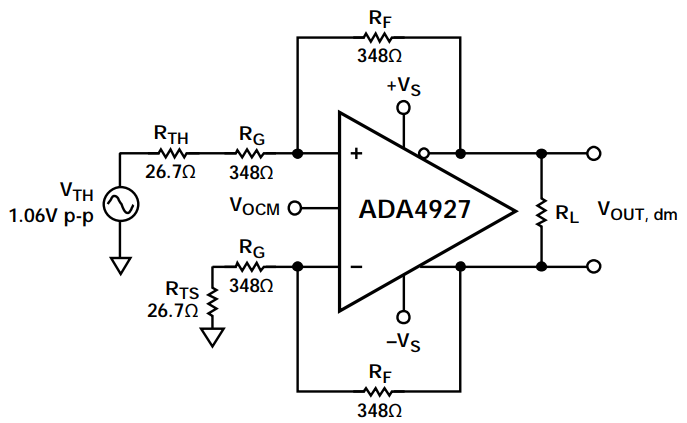

RTS=RTH=RS||RT=26.5Ω(取标准电阻26.7Ω)。这里我们需要注意,从戴维南等效电路可以看出,等效输入电压VTH大于1VPP。经过调整后的电路如下图10所示:

图10:戴维南等效值和匹配增益电阻

到现在为止,电路基本设计完成了。通过上述几个步骤,我们确定了信号等效输入阻抗为50Ω,上下反馈环路也保持平衡。但是还有两个个问题:

1) 两个环路中的等效RG值均变大了(加入了RTS),这导致我们需要的增益略小于1。

2) 由于RT=56.2Ω,而不是50Ω,所以等效输入电压VTH的值要略大约1VPP,而我们设计的输入范围是1VPP。

这两点对输入电压幅度的影响刚好相反,对于反馈环路中的大电阻值(~1kΩ),影响相互抵消。也就是说通过这样的设计后,输入信号幅度变大了,但是增益变小了,所以对输出信号幅度无影响。但是对于小阻值的RF或RG或高增益来说,减小的闭环增益不能通过增加的VTH完全消除,必须通过接下来的第4步来解决:

4,在本例中,期望的差分输出是1VPP,因为端接的输入信号是1VPP,闭环增益是1。然而实际的差分输出电压等于1.06VPP*348/(348+26.7)=0.984VPP。为了获得期望的1VPP输出电压,可以通过增加RF来实现最终的增益调整,而不需要更改任何输入电路。RF计算公式如下:

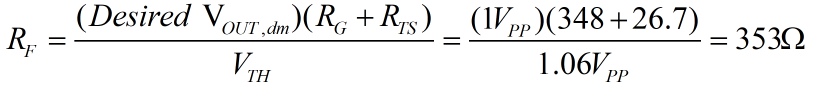

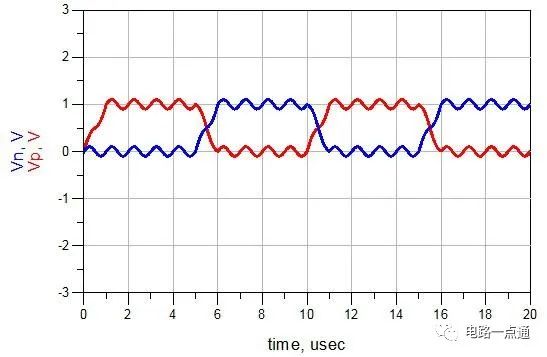

选择RF为标准电阻357Ω可提供1.01VPP的差分输出电压。最终电路如下图11所示:

图11:端接的单端转差分电路,G=1

原文标题:ADC单端转差分电路分析

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

电路

+关注

关注

172文章

5905浏览量

172155 -

adc

+关注

关注

98文章

6496浏览量

544484

原文标题:ADC单端转差分电路分析

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

将大多数信号链中的单端信号转换为差分信号分析

将大多数信号链中的单端信号转换为差分信号分析

评论