数字硬盘录像机,英文名称为Digital Video Recorder,简称DVR,它是视频监控系统中重要的设备,用于替代早期的长延时录像机或者磁带录像机。目前硬盘录像机从硬件架构上分主要分为工控式硬盘录像机(或者工控硬盘录像机或者PC式硬盘录像机)、嵌入式硬盘录像机,从压缩算法来分有小波压缩、MJPEG、MPEG4、H.264等。目前工控式硬盘录像机和嵌入式硬盘录像机所占市场比重差不多,由于嵌入式硬盘录像机的稳定性及易维护性,选择嵌入式硬盘录像机的用户会越来越多,市场前景非常大。基于这种应用背景,本文提出了嵌入式硬盘录像机的设计思路和实现方案。

系统总体方案

1 技术指标

本系统的主要技术指标如下。

● 视频输入:16路复合视频输入PAL/NTSC。

● 视频输出:2路复合视频输出PAL/NTSC(BNC接口,1.0VP-P, 75Ω)。

● 音频输出:16路音频输入20~100mV10kΩ(RCA)。

● 音频输出:2路音频输出,20~100mV,1kΩ(RCA)。

● 系统资源:同时多路录像、同时录像回放、同时网络操作。

● 图像压缩:增强型H.264,视频和音频信号压缩后生成复合的H.264码流,码流回放时视频和音频保持同步。也可设置单一视频流。

● 音频压缩:G.729

2 设计方案

根据系统要求的技术指标,本文设计的16路嵌入式DVR系统硬件部分采用了主从式双CPU架构模式。主CPU选用了ARM9处理器,具体型号为三星半导体的S3C2510A,从CPU选用DSP处理器,具体型号为美国德州仪器(TI)的多媒体处理芯片TMS320DM648。主从CPU之间通过PCI总线进行通信。

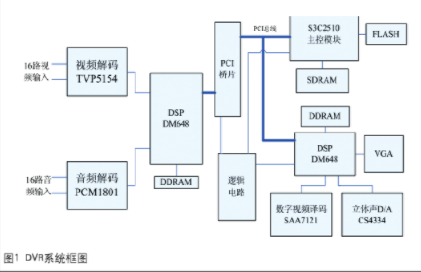

整个系统的工作流程设计为:系统上电或复位后,主CPU S3C2510A从Flash加载程序,完成对芯片的初始化和外围硬件的配置,之后从CPU TMS320DM648便开始进行图像采集。从CPU通过I2C口对系统中的视频解码芯片进行控制,将从摄像头采集到的模拟视频信号转换为数字视频信号,送入DM648的视频通道(VP端口);同步采集到的模拟音频信号经过音频编解码器模/数转换后,送入DM648的音频通道(McASP端口)。DM648将接收到的数字视频信号和数字音频信号数据分别进行压缩,再把压缩视频流和压缩音频流进行同步复合,产生H.264视频复合流,再通过PCI总线上传给主CPU,主CPU将从PCI接口收到的数据以文件的格式存储到本地硬盘,供日后调用;同步将复合数据流传送给图像预览芯片进行显示。整个DVR系统框架图如图1所示。

系统原理设计

1 S3C2510A ARM9处理器简介

S3C2510A是三星半导体生产的16/32位的RISC微控制器,属于ARM9处理器系列,是针对基于以太网系统的低成本、高性能的微控制器解决方案。

2 TMS320DM648数字信号处理器简介

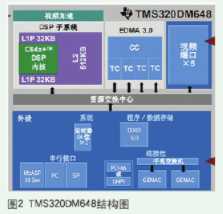

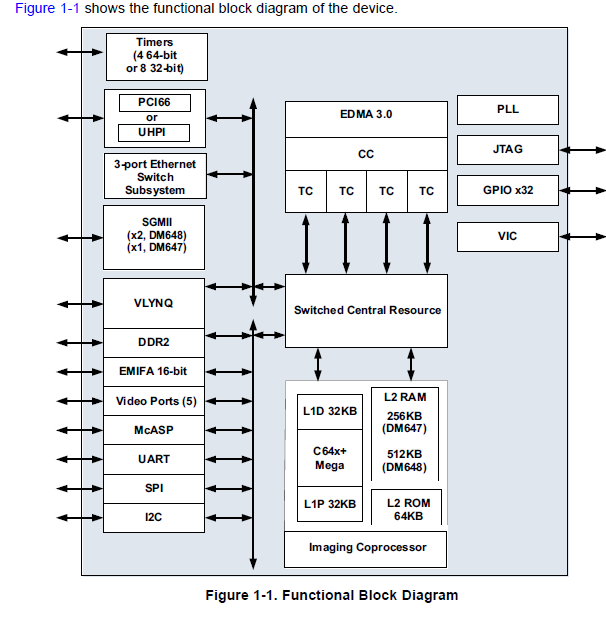

TMS320DM648是TI公司于2007年推出的一款高性能的32位定点DSP,主要面向数字媒体应用,属于C6000系列DSP。

DM648保留了C64X原有的内核结构,工作频率由内部倍频器设置,可以达到720MHz、800MHz或900MHz,相应的时钟周期为1.39ns、1.25ns或1.11ns,每秒可执行指令数5760、6400和7200MIPS。此外DM648片上带有5个双通道(A、B两通道)数字视频口(VP口),可同时处理多路数字视频流,片上带有多通道串行音频接口,可同时处理10路立体声输入/输出音频信号。

核心模块原理设计

整个数字硬盘录像机根据功能可以划分以下几大核心模块:

①主控制模块;

②视音频采集、压缩模块;

③视音频预览、回放模块;

④其他模块(电源、存储器扩展、网络传输、逻辑控制等);

本文详细介绍主控制模块和视频处理模块的设计。

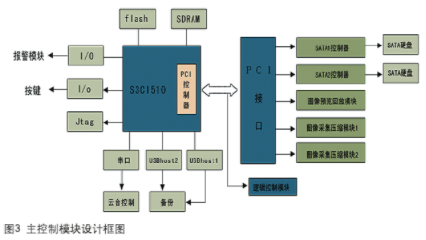

1 主控制模块

本模块主要实现系统的控制,对整个系统任务的运行进行分配与调度。S3C2510A本身内置PCI控制器,5个PCI接口可分别和2个音/视频压缩模块,1个图像预览,回放模块,2个数据存储模块连接;再加上已有的串口,USB接口,网络接口,I/O等组成整个系统的控制模块。设计思路如图3所示。

2 视音频采集/压缩模块

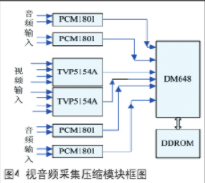

视音频信号处理的流程如下:模拟视频信号先经视频解码器TVP5154A转换成8位YUV数字视频信号Y[7:0],再送至DM648的视频输入接口。模拟音频信号经音频AD转换器PCM1801转换为I2S格式的音频数据,进入多媒体压缩芯片的音频输入接口,DM648将原始的视频和音频数据分别进行压缩,再把压缩视频流和压缩音频流进行同步复合,产生H.264视频复合流。一片DM648可以同时产生8个视/音频通道的H.264复合数据流。DM648把每个视/音频通道的复合视频数据在片外DDRAM的数据缓冲区中排列成固定长度的数据包。当缓冲区内的数据量超过一定的阈值,它就通过PCI中断向主CPU发出请求,当中断被响应时,主CPU从包缓冲区内将数据取走。

DM648具有5个视频端口,支持多种分辨率和标准,如CCIR601、ITU-BT.656、BT.1120等,每个端口为20bit位宽,可以被灵活的配置为一个20/16bit或两个10/8bit通道。同时,每个端口都可配置为视频输入或视频输出。

TVP5154A具有4个通道,每个通道均为具有可编程多态换算器(polymorphic scaler)的独立解码器,可通过嵌入式同步模块将NTSC、PAL或SECAM视频信号转换成8位ITU-R BT.656格式,或使用分立同步模块使输出格式为8位4:2:2。

模拟摄像头进行视频数据采集,TVP5154A将采集到的模拟数据进行数字化,然后送给DM648的视频端口进行压缩处理。4片TI公司生产的TVP5154A,与2个DM648的连接可组成16路的视频采集,压缩模块如图4所示(只给出了8路的连接图)。

图4中,TVP5154A的CH1_OUT,CH2_OUT,CH3_OUT,CH4_OUT口与1片DM648的VP0,VP1口直接连接,组成1个8路的视频采集,压缩模块,用于数据的传输。DM648通过I2C总线对TVP5154A内部寄存器进行读写,达到控制该芯片的目的。

音频输入采集模块由8个PCMl801U型音频采集电路及其外围电路组成,主要功能是对由拾音器采集输入的模拟音频信号进行采样,然后将其转换为DSP可以处理的数字音频数据格式。PCMl801U是采用5V工作电压的双声道16位音频模/数(A/D)转换器,包括1个单端-差分模拟前端、1个5阶△一∑调制器(64倍重复取样)、1个内部高通数字均分滤波器。

DM648有专门的McASP,与4个PCMl801U连接,实现音频的输入采集功能。用PCMl801U的左、右2个16位音频声道获取4路音频通道的数字化数据,音频采集的数据格式为每路单声道、44.1kHz采样率,每个采样数据用8位量化。采集输出的数字音频数据通过McASP传给DSP的输入缓冲区单元,当设定用于存放音频采样数据的缓存器已满时产生DMA中断,并在DMA中断服务程序中根据实际设定情况处理音频数据,经过实时编码压缩后的音频数据存储到外部SDRAM中。

本系统的主频高达166MHz,属于高频系统,所以在进行PCB的设计时,必须进行抗高频干扰的设计与处理。DM648作为高性能数字媒体处理器不仅内部具有很高的运行频率,而且与外部的DDRAM的总线速度也达到266MHz或333MHz,如果外部的DDRAM由于布线原因达不到设计的希望速度,会降低系统的性能。此外由于100MHz以上的信号总线,存在信号完整性问题。为了保证信号的完整,在设计的时候采用了如下方法:

(1)对DDRAM的时钟线,尽量走短线,而且到两个DDRAM的长度尽量做到相等;

(2)FLASH等其他外设不要直接与数据和地址总线连接,而是通过缓冲芯片(如SN74LVT16245B)连接;

(3)高速总线上串入了小阻值电阻,阻值大小通过Protel软件仿真得到,同时对线路进行了阻抗限制。

此外,由于DM648内部有PLL,对PLL外部所接器件,让它们尽可能的靠近芯片,而且只放在了线路板的一面上。对于JTAG的连线长度不超过6英寸,如果超过6英寸长的加了驱动。本系统中既有模拟部分又有数字部分,所以在设计的时候,特别注意了模拟电源和数字电源的设计,尽量减少数字信号对模拟信号的干扰,否则对采集的视频信号会有雪花、条纹,音频信号产生噪声等。对视频、音频芯片采用了单独的电源芯片供电,模拟地和数字地通过单点或采用磁珠相连。

以上的抗高频干扰方法的采用,使得整个系统在调试的过程中能够顺利的进行。

责任编辑:gt

-

处理器

+关注

关注

68文章

20329浏览量

254844 -

嵌入式

+关注

关注

5209文章

20645浏览量

336916 -

录像机

+关注

关注

1文章

96浏览量

28932

发布评论请先 登录

TMS320DM648 pdf datasheet

TMS320DM648 highest-performance fixed-point DSP generation

S3C2510A pdf,S3C2510A datashee

TMS320DM648-900,pdf(Digital Me

TMS320DM648-800,pdf(Digital Me

TMS320DM648-720,pdf(Digital Me

TMS320DM647, TMS320DM648 Digit

TMS320DM648-1100,pdf(Digital M

DSP芯片TMS320DM648数字信号处理器简介

TMS320DM647和TMS320DM648数字媒体处理器英文原版资料详细概述

TMS320DM648 TMS320DM648 Digital Media Processor

TMS320DM647/TMS320DM648数字媒体处理器数据表

从TMS320DM642迁移至TMS320DM648/DM6437

从TMS320DM642/3/1/0迁移到TMS320DM648/7器件

基于TMS320DM648和S3C2510A芯片实现16路嵌入式DVR系统的设计

基于TMS320DM648和S3C2510A芯片实现16路嵌入式DVR系统的设计

评论