有人希望能谈谈在做FPGA设计的时候,如何理解和使用过约束。我就以个人的经验谈谈:

什么是过约束;

为什么会使用过约束;

过约束的优点和缺点是什么;

如何使用过约束使自己的设计更为健壮。

什么是过约束(overconstraint)

所谓过约束,就是给目标时钟一个超过其设定运行频率的约束。比如实际运行的时钟频率是100MHz,我们在给这个时钟添加约束的时候,要求它能运行在120MHz。

为什么会使用过约束

通常在两种情况下,我们可能会使用过约束。

第一种情况,FPGA的时序报告不准确,为了确保逻辑的实际运行频率能满足要求,做过约束来保留设计余量。

FPGA的时序报告是基于FPGA的时序模型计算出来的,时序模型来源于实验室的测试和对生产过程的严格控制,是要充分考虑PVT(Process,Voltage,Temperature)的影响计算出来的。对比较成熟的FPGA厂家来说,研发,生产,测试都有标准流程控制,这一部分的数据还是比较可靠的。如果是新的厂家,大家可能要做好时序模型不准确的心理准备。在工艺不变的情况下,信号的传输,翻转速率随电压,温度的变化而变化。一般来说,温度越低,电压越高,信号的传输,翻转越快,反之越慢。而FPGA的设计软件在做STA的时候,往往是根据最差的工作条件下的(Worst Case)给出的。所以我们会看到这样的现象,时序报告显示的时序是不满足设计要求的,但逻辑运行到FPGA上功能又是正常的。这是因为FPGA的实际运行条件要比Worst Case好,实际的时序也优于报告的结果。如果是这种情况,可以不考虑使用过约束。

第二种情况,对某些关键的时钟域,时序不太容易满足,施加一个更高的时钟约束,以期望软件能跑出一个满意的结果。如果是这种情况,需要注意的是EDA软件在做布局布线的时候,会根据逻辑功能和时钟频率分配布局布线资源。过约束加的不合理,会造成非关键路径占用有限的布局布线资源,反而会使布局布线的结果更差。所以在做过约束的时候,要根据你的设计合理设置,不能简单的把所有时钟都做过约束。

过约束的优点和缺点:

过约束的优点显而易见,会让的设计运行的余量更大。缺点除了我们上面讨论的,如果在你的设计里面有跨时钟域的信号传递,而你没有对跨时钟域的路径做约束,软件在分析跨时钟域的delay的时候,由于变成过约束后,源时钟和目的时钟的频率相关性变化了,这部分的delay约束就变成了无限小,布局布线更困难了。这是我们在做过约束设计的时候要特别注意的。

过约束还有一个问题是,比如你的设计频率是100MHz,添加的约束是120MHz。那么在做STA的时候,软件还是按照120MHz来分析。即使你的布局布线的时序结果是119MHz,已经满足设计要求,但在时序报告上,还会显示时序不满足。这给我们的时序分析带来一些麻烦。

如何使用过约束使自己的设计更为健壮

在使用过约束的时候,一般情况下,以增加20%-30%为宜,太大的余量并没有太大的意义。如果该时钟有跨时钟域的操作,一定要通过专门的约束(Multicycle或max delay)在明确定义这部分的延时要求。

在Lattice的设计软件中,为了配合过约束的使用,增加的一个PAR_ADJ属性:

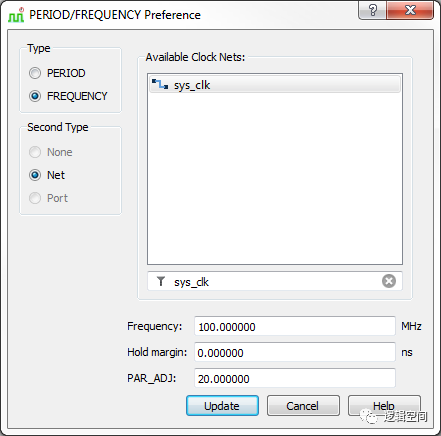

FREQUENCY NET“sys_clk” 100.000000 MHz PAR_ADJ 20.000000 ;

这样的约束会告诉软件,用100+20=120MHz做布局布线的时候,而用100MHz的约束来做STA,这样就不会发生我们前面遇到的困扰了。

GUI的界面是这样的:

原文标题:FPGA的过约束

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

FPGA

+关注

关注

1664文章

22509浏览量

639554

原文标题:FPGA的过约束

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

2026深入拆解:Gemini 3.0 镜像官网如何理解 FPGA 时序约束并自动生成 SDC 文件

基于XILINXPWR - 083的DC/DC转换器电源管理解决方案

XILINXPWR - 082 EVM电源管理解决方案深度解析

变频器过励磁增益及软件过流问题

FPGA时序收敛的痛点与解决之道——从一次高速接口调试谈起

Vivado时序约束中invert参数的作用和应用场景

输入引脚时钟约束_Xilinx FPGA编程技巧-常用时序约束详解

精准计时与低功耗的完美融合

开源RISC-V处理器(蜂鸟E203)学习(二)修改FPGA综合环境(移植到自己的Xilinx FPGA板卡)

时序约束问题的解决办法

蜂鸟e203移植fpga上如何修改约束文件

技术资讯 I 图文详解约束管理器-差分对规则约束

PCB Layout 约束管理,助力优化设计

如何理解和使用做FPGA设计时的过约束?

如何理解和使用做FPGA设计时的过约束?

评论