3月30日,据台湾媒体报道,原定于2021年第四季度试产,2022年量产的N4工艺,有设备供应商传出,量产时间将提前至第四季度。并且首批产能将由苹果完全包下,用于设计具备更高性能的MacBook系列产品。

N4工艺是台积电5nm家族的最新成员,透过完全兼容的设计规则从N5进行直接转移,从而提供更高的效能、功率及密度。台积电希望这可以使得客户能够利用已经充分发展的N5设计基础假设,并从与N5相比极具竞争力的成本与效能优势中进行获益。

有半导体从业者表示,除了4nm工艺以外,苹果在下半年推出的iPhone 13系列新机,其搭载的A15芯片也计划在5月底提前量产,将采用5nm工艺强化版。加上AMD、联发科、高通等5nm新品在下半年集中投片,以及产能爆满的7nm工艺,让台积电全年营收增幅可以达到或者超过15%。

回到台积电的4nm工艺,其正式量产时间被提前至2021年第四季度,这意味着其试产时间或将在今年的第二季度。并且首批产能基本被苹果吃下,按照苹果产品时间表来看,首批搭载的设备将是新一代的MacBook系列产品。

当然除了苹果以外,由于量产时间提前,因此第四季度苹果并非唯一的买家。还有如高通的下一代旗舰SoC“骁龙895”(研发代号为Waipio)以及X65/X62 5G基带,NVIDIA或AMD的最新产品等,都可能采用这一制程。

面对台积电4nm的提前量产,有消息称三星将取消这一中间制程,决定在5nm之后直接进行3nm GAAFET的研发生产。

不过台积电的N3工艺也计划将在明年亮相,按照台积电的计划,N3将在2021年试产,2022年下半年量产,并且N3工艺其逻辑密度将提高70%,效能提升15%,功耗则比N5降低30%。

与三星3nm工艺不同的是,台积电的N3将继续采用FinFET晶体管架构,台积电方面表示这其中有两个重要的考量,一个是研发团队发现有新的方式可以将FinFET性能提升到新的高度,另一个则是可以提供最佳的技术成熟度、效能及成本,拥有完整的平台支持行动与HPC应用,让3nm工艺尽快带给客户使用。

但近期也有消息传出,台积电的3nm进度不如预期,初期月产能仅为预期的一半左右,不过台积电董事长刘德英在此前便公开表示,台积电3nm制程依然按照计划持续的推进当中,毕竟比预期要更超前一些。

当然,由于苹果新机通常会在每年的3季度发布,这意味着台积电3nm工艺想要赶上苹果新机的发布计划,就必须在2022年6月份左右完成量产,这对于台积电而言将是一个挑战。

无独有偶,英特尔CEO Pat Gelsinger也在近期公布了英特尔IDM 2.0的计划,将斥资200亿美元建设新的晶圆厂。目前的主要工艺为10nm,而下一个工艺则是7nm。不过由于各种原因,英特尔的7nm已经跳票到了2023年。

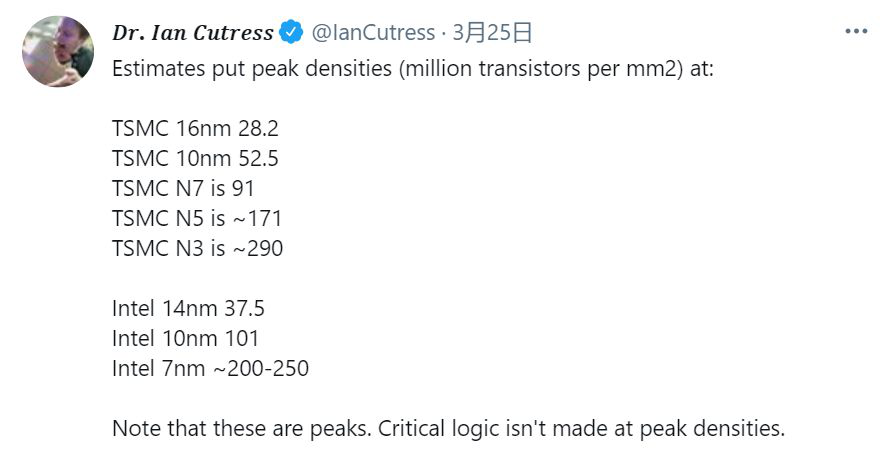

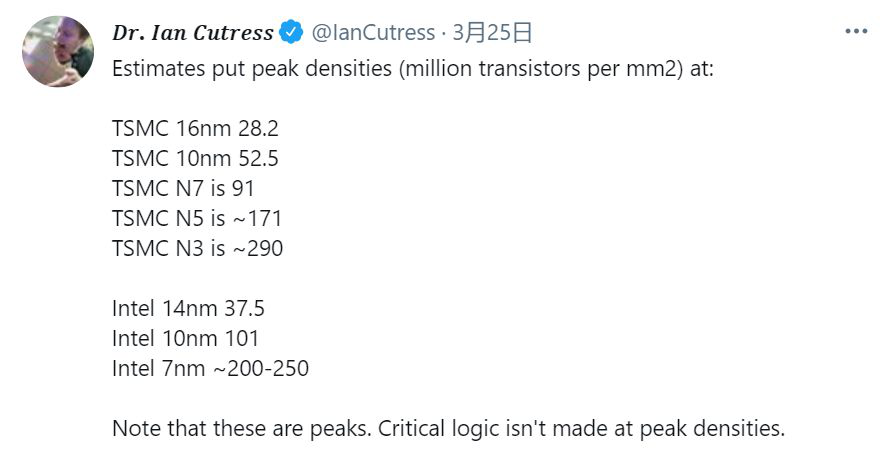

有趣的是,Anandtech的主编Ian Cutress在社交媒体上公布了一组数据,台积电的5nm工艺密度是1.71亿晶体管/mm2,3nm工艺可达2.9亿晶体管/mm2,而英特尔的10nm工艺是1.01亿晶体管/mm2,7nm节点可达2-2.5亿晶体管/mm2。如果按最高水平来看,英特尔的7nm晶体管容量已经接近台积电的3nm,这也意味着性能上可能差距也并不是很大。当然这只是理论上而言,实际表现还需要看产品具体情况而定。

或许这也意味着,各家芯片制程标注的数据可能含有许多的水分,这也就解释了为何三星的先进制程有时候与台积电的落后制程做出来的产品相当。反过来想,或许这几家代工厂的工艺差距并没有想象中的那么大。

N4工艺是台积电5nm家族的最新成员,透过完全兼容的设计规则从N5进行直接转移,从而提供更高的效能、功率及密度。台积电希望这可以使得客户能够利用已经充分发展的N5设计基础假设,并从与N5相比极具竞争力的成本与效能优势中进行获益。

有半导体从业者表示,除了4nm工艺以外,苹果在下半年推出的iPhone 13系列新机,其搭载的A15芯片也计划在5月底提前量产,将采用5nm工艺强化版。加上AMD、联发科、高通等5nm新品在下半年集中投片,以及产能爆满的7nm工艺,让台积电全年营收增幅可以达到或者超过15%。

回到台积电的4nm工艺,其正式量产时间被提前至2021年第四季度,这意味着其试产时间或将在今年的第二季度。并且首批产能基本被苹果吃下,按照苹果产品时间表来看,首批搭载的设备将是新一代的MacBook系列产品。

当然除了苹果以外,由于量产时间提前,因此第四季度苹果并非唯一的买家。还有如高通的下一代旗舰SoC“骁龙895”(研发代号为Waipio)以及X65/X62 5G基带,NVIDIA或AMD的最新产品等,都可能采用这一制程。

面对台积电4nm的提前量产,有消息称三星将取消这一中间制程,决定在5nm之后直接进行3nm GAAFET的研发生产。

不过台积电的N3工艺也计划将在明年亮相,按照台积电的计划,N3将在2021年试产,2022年下半年量产,并且N3工艺其逻辑密度将提高70%,效能提升15%,功耗则比N5降低30%。

与三星3nm工艺不同的是,台积电的N3将继续采用FinFET晶体管架构,台积电方面表示这其中有两个重要的考量,一个是研发团队发现有新的方式可以将FinFET性能提升到新的高度,另一个则是可以提供最佳的技术成熟度、效能及成本,拥有完整的平台支持行动与HPC应用,让3nm工艺尽快带给客户使用。

但近期也有消息传出,台积电的3nm进度不如预期,初期月产能仅为预期的一半左右,不过台积电董事长刘德英在此前便公开表示,台积电3nm制程依然按照计划持续的推进当中,毕竟比预期要更超前一些。

当然,由于苹果新机通常会在每年的3季度发布,这意味着台积电3nm工艺想要赶上苹果新机的发布计划,就必须在2022年6月份左右完成量产,这对于台积电而言将是一个挑战。

无独有偶,英特尔CEO Pat Gelsinger也在近期公布了英特尔IDM 2.0的计划,将斥资200亿美元建设新的晶圆厂。目前的主要工艺为10nm,而下一个工艺则是7nm。不过由于各种原因,英特尔的7nm已经跳票到了2023年。

有趣的是,Anandtech的主编Ian Cutress在社交媒体上公布了一组数据,台积电的5nm工艺密度是1.71亿晶体管/mm2,3nm工艺可达2.9亿晶体管/mm2,而英特尔的10nm工艺是1.01亿晶体管/mm2,7nm节点可达2-2.5亿晶体管/mm2。如果按最高水平来看,英特尔的7nm晶体管容量已经接近台积电的3nm,这也意味着性能上可能差距也并不是很大。当然这只是理论上而言,实际表现还需要看产品具体情况而定。

或许这也意味着,各家芯片制程标注的数据可能含有许多的水分,这也就解释了为何三星的先进制程有时候与台积电的落后制程做出来的产品相当。反过来想,或许这几家代工厂的工艺差距并没有想象中的那么大。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

英特尔

+关注

关注

61文章

9985浏览量

171966 -

三星电子

+关注

关注

34文章

15867浏览量

181095 -

台积电

+关注

关注

44文章

5652浏览量

166694 -

苹果

+关注

关注

61文章

24431浏览量

199205 -

晶圆代工

+关注

关注

6文章

859浏览量

48614

发布评论请先 登录

相关推荐

台积电设立2nm试产线

最大产能,从而满足苹果、高通、联发科等多家客户的需求。 据悉,台积电新竹宝山厂(Fab20)启动了2纳米制程的试产线的月产能规划约为3000

台积电2025年起调整工艺定价策略

近日,据台湾媒体报道,随着AI领域对先进制程与封装产能的需求日益旺盛,台积电计划从2025年1月起,针对其3nm、5

台积电2nm工艺将量产,苹果iPhone成首批受益者

。然而,最新的供应链消息却透露了一个不同的方向。据悉,A19系列芯片将采用台积电的第三代3nm工艺

台积电美国厂预计2025年初量产4nm制程

台积电在美国亚利桑那州的布局正逐步展开,其位于该地的一厂即将迎来重大进展。据悉,该厂将开始生产4nm制程芯片,并预计在2025年初正式实现

台积电美国工厂4nm试产成功

近日,全球领先的半导体制造商台积电传来振奋人心的消息,其位于美国亚利桑那州的首座晶圆厂成功完成了4nm(N4)工艺的首次试产,标志着这一耗资

台积电SoIC技术助力苹果M5芯片,预计2025年量产

在半导体行业的最新动态中,台积电再次展示了其在制程技术和封装技术方面的领先地位。本周,台积电宣布

台积电3nm产能供不应求,骁龙8 Gen44成本或增

在半导体行业的最新动态中,三星的3nm GAA工艺量产并未如预期般成功,其首个3nm工艺节点SF3E的市场应用范围相对有限。这一现状促使了科

苹果自研AI服务器芯片,预计2025年台积电3nm工艺

4 月 24 日,知名数码博主@手机晶片达人发布动态,爆料苹果正研发自家 AI 服务器芯片,预计 2025 年下半年量产,采用台积

今日看点丨传台积电2nm制程加速安装设备;吉利汽车新一代雷神电混系统年内发布

)架构量产暖身,预计宝山P1、P2及高雄三座先进制程晶圆厂均于2025年量产,并吸引苹果、英伟达、AMD及高通等客户争抢产能。台

发表于 03-25 11:03

•952次阅读

台积电4nm工艺将提前量产 首批产能被苹果包下

台积电4nm工艺将提前量产 首批产能被苹果包下

评论