随着车内网络的复杂化对速度,尤其是对故障容错与实时性的需求不断增加,FlexRay总线的高速度、确定性、容错性等特点引起广大学者和厂商的关注。 FlexRay支持分布式控制系统,具有全面协同工作的能力,其信息传输的确定性离不开其内部的时钟同步机制的支持。时钟同步机制可根据该节点启动的不同工作阶段,定义成不同的工作状态,如初始化、等待接收同步帧等。考虑到传统的FSM方法建立模型存在代码难以复用、维护困难等问题,本文基于量子框架的角度,采用有限状态机的方法对FlexRay时钟同步机制进行研究。

1 量子框架

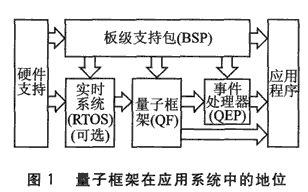

量子框架是基于事件驱动并发状态机的一种应用框架,适用于嵌入式的可重用的基础结构,它为外围的应用系统提供了硬件框架。量子框架在应用系统中的地位如图 1所示。

量子框架理论将应用系统按照功能模块分解成相互独立的活动对象,它们之间通过量子框架提供的软总线和可识别的事件实例来实现彼此间的通信,活动对象彼此间没有任何的通信。事件队列是为活动对象提供的一个外部通信接口,能够使活动对象接收事件实例;还提供了保护内部状态图的缓冲空间,以防止事件的生产爆发带来的破坏,保证了活动对象在运行过程中的完整性。

2 FlexRay时钟同步机制

2.1 FlexRay内部结构

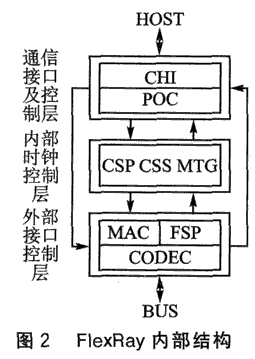

FlexRay按照其功能可以分成3个层次:通信接口及控制层、内部时钟控制层和外部接口控制层,如图2所示。

通信接口及控制层主要包括控制主机接口(CHI)和协议运行控制器(POC)。CHI主要负责内核和主机通信接口,POC是内核的控制单元。

内部时钟控制层包括时钟同步启动模块(CSS)、时钟同步处理模块(CSP)和时钟发生器(MTG)。系统中各个节点的时钟同步就是主要依靠这个层来实现的。

外部接口控制层包括多路访问控制模块(MAC)、数据帧与符号处理模块(FSP)和编码解码处理模块(CO—DEC)三个部分,可实现对接收发送数据信息的处理和对总线读/写操作的编码解码功能。

2.2 时钟周期结构

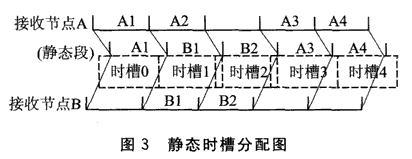

每一个通信周期内包括最小时间节拍层 (Microtick)、最大时间节拍层(Macrotick)、仲裁网格层(Arbitration—grid)和通信周期层4个时间等级。每个通信周期分成4个部分:静态段、动态段、符号窗口和空闲网络段。在静态段中,基于时分复用(TDMA)技术将固定时槽分配给与各个节点匹配的ID,并允许节点传输数据。时槽大小相同,并且是从1开始向上编号。将一个或一个以上的时槽固定分配给每个节点。在运行期间,该时槽的分配不能修改,如图3所示。

2.3 内部时钟同步机制

节点的时钟同步功能主要是由内部时钟控制层实现的。其内部的MTG模块控制周期计数器和最大时钟节拍的计数器,并对其进行修正;CSP模块主要完成一个通信周期开始的初始化,测量并存储时间偏差值,计算频率与相位的修正值;CSS模块负责在集群启动,或者在作为冷启动节点时发出时钟启动信号。

当节点被唤醒并完成初始化后,就能在发出相应的主机命令后进入启动流程。节点开始监控总线,如果没有其他节点在发送数据,则自身发送数据,从而成为启动集群的主冷启动节点。在传输符号通知其他节点后,启动自身时钟,开始第一个通信循环,并根据预定义机制,主启动节点将在其分配的时槽中传输。与其他所有节点一样,它将只在一个时槽的启动阶段传输。

当节点在接收到消息识别码(ID)和时槽编号相同时,

节点接收属于自己的第1条消息。当接收到第2条消息时,后续的冷启动节点启动自身时钟,并通过当前获得通信循环周期号和消息的时槽编号进行初始化。两条消息的时间差理论上应该与主冷启动的通信周期相对应,接收节点要比较它们的可能的偏差,并通过纠正机制计算出修正值,从而通过修改内部时钟发生器的时基频率,使其尽可能地与主冷启动周期值相对应。

FlexRay内部的时钟同步机制同时采用频率修正与相位修正两种方法对时钟进行修正。

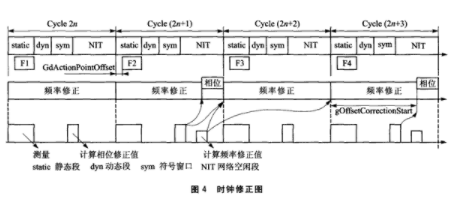

2.3.1 频率修正

在CSP模块中,频率偏差的测量在每个通信周期的静态段中进行,通过内部算法在奇数周期的静态段之后计算偏差修正值。如图4所示,偏差的结果在 Cycle(2n+1)中计算得到,在Cycle(2n+2)和Cycle(2n+3)两个周期内MTG模块利用此偏差值进行频率修正,而在 Cycle(2n+3)中得到的新的偏差值在接下来的2个周期中得到应用。

2.3.2 相位修正

在CSP模块中,相位修正值的计算是在每个通信周期中都进行采集(静态段)和计算(在开始进行相位修正之前完成)的;应用于MTG模块的奇数周期内的NIT段,从 gOffsetCorrectionStart时刻开始到下一个周期开始之前,完成相位的修正过程。

值得注意的是,MTG模块每个周期都要进行频率修正。为了保证两种修正方式的正确性,频率偏差值的更新周期和相位修正周期是分开的。图4中,在 Cycle(2n+1)周期中MTG同时进行频率和相位的修正,但没有进行频率修正值的更新;而在Cycle(2n+2)周期,接收到CSP模块发送的新频率偏差值vRateCorrection,更新频率偏差值,进行频率修正,但没有进行相位修正。也就是说,在没有更新频率偏差值的周期内,两种修正同时进行;在频率更新的周期内,不进行相位修正。另外,每个奇数周期内,CSP在静态段之后进行相位和频率修正值的计算。理论上这两个计算过程没有时间上的先后,只要确保相位修正值在应用前(gOffsetCorrectionStart)得到,而频率偏差值在下一个周期到来之前得到。

3 基于量子框架的行为建模

3.1 有限状态机的设计

有限状态机是对描述对象的抽象描述,它把对象模型分解成一些能够进行读/写操作或者等待外部事件的状态,并且能够由外部事件引起对象状态的转换,即在当前状态下,由外部事件的发生并在满足某些条件的情况下,进入第2个状态。

3.2 对象分析

根据节点配置的不同功能,FlexRay内部的各个模块表现为不同的状态变化。在一个系统的众多节点中,包括数量有限的冷启动节点(cold start node)和普通节点。冷启动的节点分成2种:一种是启动整个集群的主冷启动节点(1eading cold start node);另一种是根据其他冷启动节点的参数来完成启动的从冷启动节点(following coldstart node)。这里只讨论节点作为从冷启动节点的情况。

3.3 活动对象建模

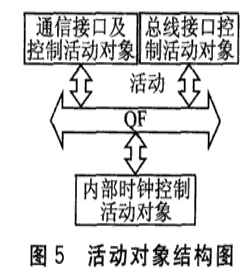

如上所述,每个活动对象都是作为一个相对独立的任务来处理的。量子框架起到了软件总线的作用,系统的功能扩展、分解、集成比较容易,可以方便地进行升级、裁剪。将FlexRay系统按功能模块分解成3个活动对象,如图5所示。

3.3.1 通信接口及控制活动对象

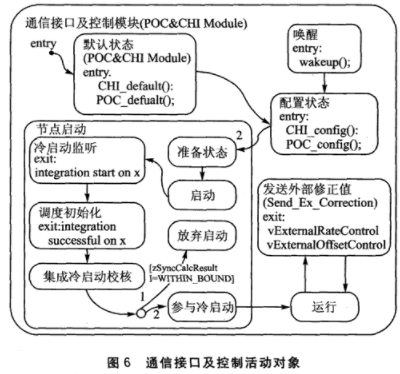

这个活动对象包括CHI和POC两个模块。CHI是主机和FlexRay内核通信接口。在实现时钟同步过程中,该模块主要是接收MTG的内部时钟和CSP 发送的当前接收同步帧的溢出信号,以及向CSP发送外部频率/相位修正值。POC是FlexRay内核非常重要的控制模块,负责协调节点内各个功能模块有效地运行。根据节点时钟同步流程,建立有限状态模型,如图6所示。

如图6所示,节点首先对两个模块进行初始化;当接收到主机配置指令后,进行内部功能配置;完成后进入节点启动状态,最后转换到运行状态。如果在运行状态接收到主机的外部修正值时,则活动对象发送vExternRate—control和vExternOffsetControl两个变量到CSP模块,用于节点内部时钟修正。

3.3.2 内部时钟控制活动对象

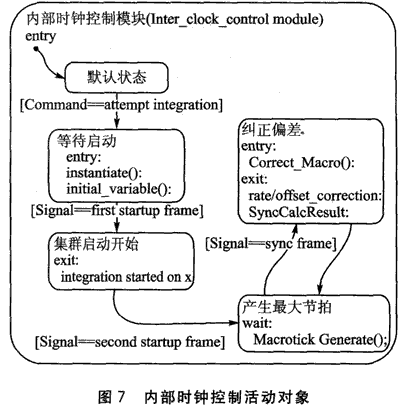

此活动对象包含CSS、CSP和MTG三个功能模块,是时钟同步机制的主要组成部分。这里考虑作为从冷启动节点的时钟同步过程,所以采取使用其他主冷启动节点的同步化参数参来启动,调整内部时钟,从而实现系统中各个节点间的时钟同步,如图7所示。

上电后,活动对象处于默认状态。当接收到主机集群启动指令后,进入等待启动状态并建立CSS实例和对测量偏差的变量初始化;在接收两个启动帧后,节点启动内部时钟。当接收到其他冷启动节点的时钟信息同步帧后,采集节点间时间偏差,采用容错算法计算出频率和相位的修正值并发送给MTG模块,从而完成与主冷启动节点的时钟同步。

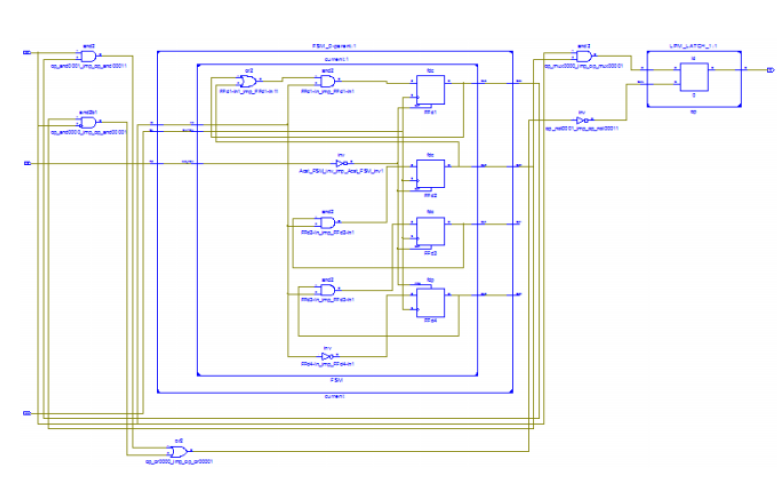

3.3.3 总线接口控制活动对象

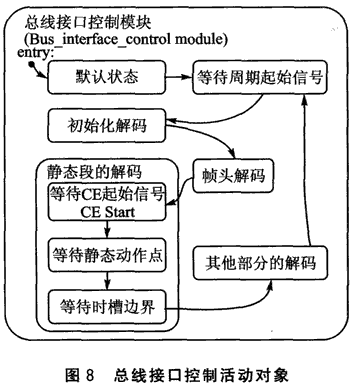

此活动对象是FlexRay内核与外部总线的接口,完成对发送数据信息的编码发送和对接收数据的解码及识别。考虑到静态段采用TMDA方式进行传输,且时钟同步采用接收数据帧的方式,这里只根据数据帧的接收及解码过程建立有限状态模型,如图8所示。

图8中,活动对象在接收到相应信号的空闲标志信号cE Start后,开始对数据帧进行解码,依次对数据帧的起始标志和帧头段进行解码;然后是静态段以及周期内其他部分的解码。通过检查数据帧、符号时序和语法来判断当前接收数据的有效性。

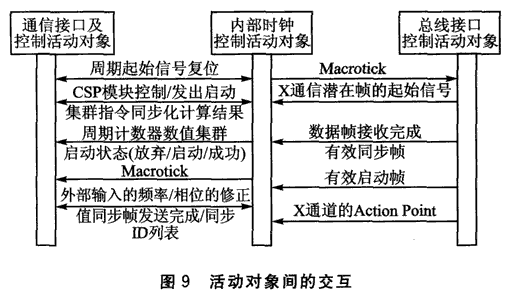

3.4 活动对象交互

在节点集群启动过程中,分解的活动对象彼此之间要发生信息交互,如图9所示。

节点通过通信接口控制对象启动内部模块,并发出集群启动的指令(attempt integration),等待接收主冷启动节点发出的启动帧。首先,总线接口控制对象接收到第一个有效偶数启动帧(valid even startup frame)后,通知内部时钟控制对象集群启动;当接收下一个有效奇数启动帧(valid odd startup frame),并把当前启动的状态信息发送给其他的两个对象,在两通道完成同步帧的接收后,内部时钟模块调用内部宏单元计算频率和相位偏差,修正内部时钟使之和主冷启动节点同步,从而实现时钟同步,并把结果SyncCalcResult发送到协议控制器,后者根据结果来决定当前节点的工作状态。

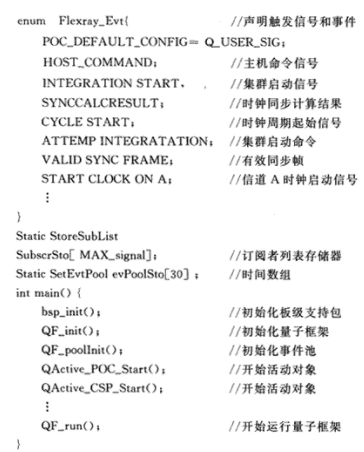

4 软件结构

应用量子框架编写应用程序主要有3步:声明触发信号和事件;定义活动对象(任务);初始化量子框架并开始运行活动对象。基本结构如下:

5 结论

FlexRay是一种支持多种网络拓扑结构,高速可靠,尤其适用于汽车环境下的总线。其协议旨在应用于需要高通信带宽和决定性容错数据传输能力的底盘控制、车身和动力总成等场合,有很好的发展前景;而量子框架则提供了基于有限状态机的实现技术,能方便地将状态图转化成系统的程序代码。

责任编辑:gt

-

嵌入式

+关注

关注

5089文章

19167浏览量

306708 -

控制系统

+关注

关注

41文章

6650浏览量

110755 -

总线

+关注

关注

10文章

2898浏览量

88254

发布评论请先 登录

相关推荐

什么是有限状态机呢

有限状态机的建模与优化设计

VHDL有限状态机设计-ST

初学者对有限状态机(FSM)的设计的认识

如何使用FPGA实现序列检测有限状态机

基于事件驱动的有限状态机介绍

基于事件驱动的有限状态机介绍

一个基于事件驱动的有限状态机

基于有限状态机的FlexRay时钟同步机制

基于有限状态机的FlexRay时钟同步机制

评论