从低频设计过渡到高频设计时,PCB布局的某些方面变化不大,但亦不可等闲视之。

高频去耦

但是,确实需要特别考虑的一件事是去耦。当信号从低频转移到高频时,基本概念不会改变,但是实现可能需要进行一些改进,这仅仅是因为当旁路不够理想甚至完全平常时,低频设计通常会完全起作用。换句话说,在去耦技术方面,低频电路是相当宽容的,因此,我们可能会养成实际上不适用于高频系统的设计习惯。

问题如下:在数字电路中,去耦电容存储电荷并将电荷输送给IC,以补偿由半导体开关动作产生的瞬态干扰。在低工作频率下,电容器有足够的时间放电,然后再充电,直到IC需要另一次电流突发。但是,随着频率的增加,电路板设计者必须尝试降低寄生电阻和电感,这些寄生电阻和电感会阻碍电容提供所需电荷的能力。

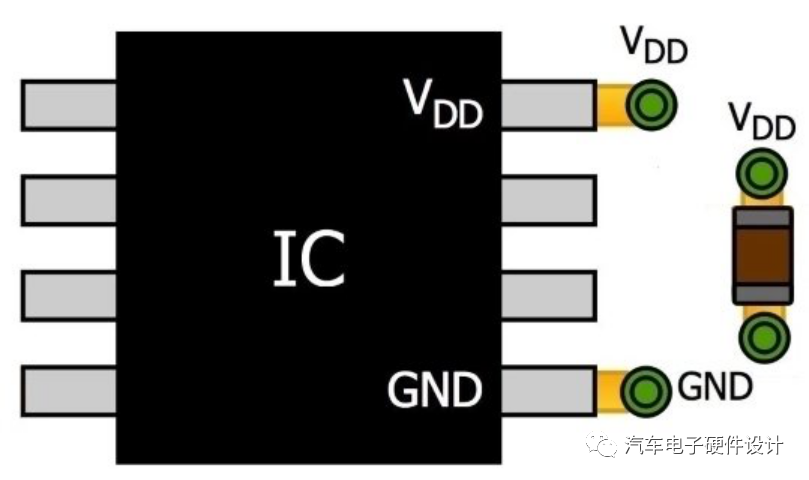

典型的去耦建议如下:“使用0.1 µF陶瓷电容器,该电容器应尽可能靠近电源引脚放置。” 例如:

该建议是一个很好的起点,并且适用于低频设计,不过当您开始了解高速旁路所涉及的复杂性时,该建议被过分简化了。在本文中,我们将研究与高速去耦技术相关的一个特定问题,在另一篇文章中,我们将继续进行讨论。

走线还是通孔?

我们知道应该将去耦电容靠近各自的引脚放置,但是当您将它们很好地闭合后,您如何实际建立连接呢?

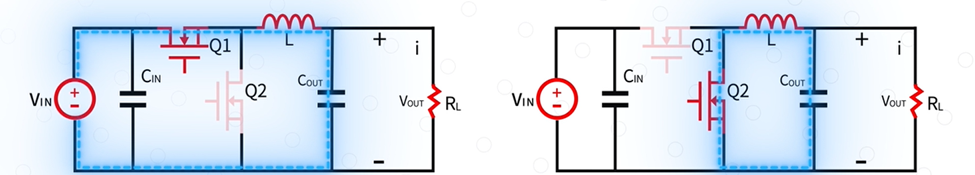

假设电源和接地引脚之间的距离足够远,您就无法对这两个引脚进行走线连接。放置电容的位置应使一个端子靠近VDD,然后使用过孔将另一端子接地。是否应该使用走线或过孔进行VDD连接?好吧,如果您没有电源板,这是一个很容易回答的问题-唯一的选择是走线(或倒铜)。但老实说,如果电路板的频率足够高,使您担心优化去耦电容,那么您确实应该有一个电源平面。

对于包括电源板的电路板,著名的高速数字设计专家Howard Johnson博士的结论是,通孔连接要好得多。下面的示例是对上一个图表的改进,但是正如您将在下一篇文章中看到的那样,via配置不是最佳的。

我最喜欢的陈述如下:在高速数字设计的背景下,将任何不重要的PCB走线长度与电源端子串联在一起“会极大地增加电源噪声”,并且“应避免EMI”。我发现这很有趣,因为它有点违反直觉-与通过通孔连接引脚相比,走线看起来更“直接”。

寻求低电感

当您深入研究此问题时,这个问题相当细微,但是讨论的很大一部分归结为电感,这对于高频数字系统的设计者来说是一个麻烦。通过对电容器和电源引脚都使用过孔,连接两个引脚的导体就是电源层,电源层的电感当然比典型走线要小得多。

您可能想知道,“通孔的电感如何?” 短走线是否真的比两个过孔具有更大的电感?

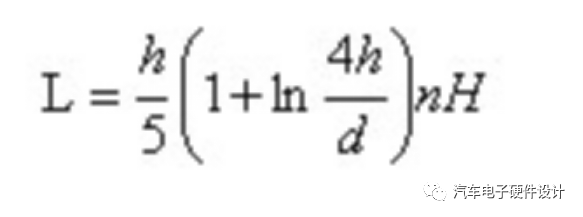

TI的本应用笔记(第4页)给出了用于计算过孔电感的以下公式:

其中h是以毫米为单位的高度,d是以毫米为单位的直径。假设我们在通孔上使用了10密耳(1mil= 0.254毫米)的钻头,我们的标准PCB厚度为63密耳(63mil= 1.6毫米)。这对应于1.3 nH的过孔电感。因此,与半英寸PCB走线的大约3.5 nH相比,两个通孔将给我们提供小于3 nH的电流。降低0.5 nH并不是太令人印象深刻,但这是一个非常保守的估计,因为电流来自电源层,而不是PCB的底部。换句话说,它不必穿过所有通孔的电感。

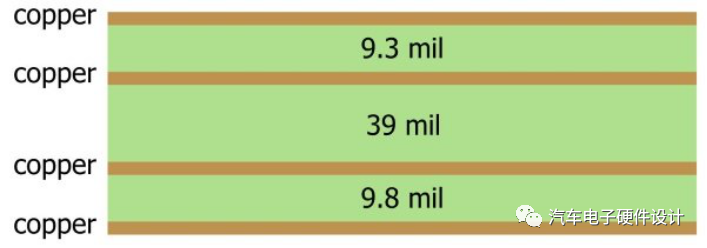

假设电源层位于与IC相邻的层上,预浸料的厚度约为10密耳(= 0.254毫米)。

典型的63 mil厚PCB的铜层分隔距离。

现在计算出的电感仅为0.12 nH,我们可以看到一对通孔可以提供远远优于走线的性能。

结论

我们已经讨论了在去耦电容器和位于同一PCB层上的高速数字IC之间建立高性能连接的一项重要技术。我们将在下一篇文章中讨论其他去耦细节。

编辑:lyn

-

PCB布局

+关注

关注

9文章

184浏览量

27964 -

去耦电容器

+关注

关注

0文章

28浏览量

9033

原文标题:PCB布局技巧和窍门:如何优化去耦连接

文章出处:【微信号:QCDZYJ,微信公众号:汽车电子工程知识体系】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

应用指南导读 | 优化HV CoolGaN™功率晶体管的PCB布局

PCB布局中如何优化去耦电路

PCB布局中如何优化去耦电路

评论