[导读] 基于ZYNQ实现复杂嵌入式系统非常便利,其应用领域也越来越广泛,本文来从对ZYNQ芯片架构的理解来谈谈个人体会。

俯瞰zynq

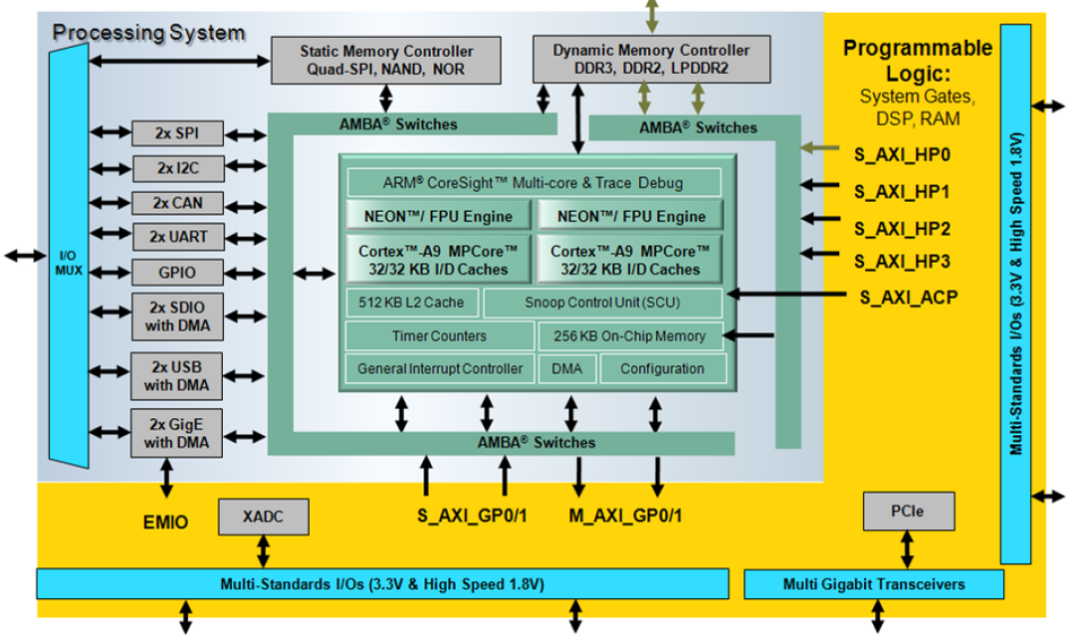

ZYNQ主要由两大部分组成:

处理系统PS(Processing System):上图左上部分即是PS部分,包括:

同构双核ARM Cortex A9的对称多处理器 (Symmetric Multi-Processing,SMP)

丰富的外设,2×SPI,2×I2C,2×CAN,2×UART,2×SDIO,2×USB,2×GigE,GPIO

静态存储控制器:Quad-SPI,NAND,NOR

动态存储控制器:DDR3,DDR2,LPDDR2

可编程逻辑PL(Programmable logic):兼容赛灵思7系列FPGA

基于Artix的芯片:Z-7010以及Z-7020

基于Kintex的芯片:Z-7030以及Z-7045

ZYNQ处理系统端PS所有的外设都连接在AMBA(Advanced Microcontroller Bus Architecture)总线,而基于FPGA设计的IP则可以通过AXI接口挂载在AMBA总线上,从而实现内部各组件的互联互通。这里涉及到两个概念:

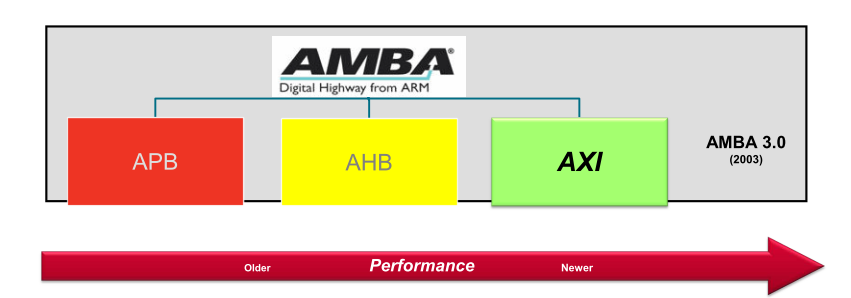

AMBA总线,熟悉ARM架构的朋友应该都大致了解, AMBA是ARM公司的注册商标。是一种用于片上系统(SoC)设计中功能块的连接和管理的开放标准片上互连规范。它促进了具有总线结构及多控制器或组件的多核处理器设计开发。自成立以来,AMBA已广为应用,远远超出了微控制器设备领域。如今,AMBA已广泛用于各种ASIC和SoC部件,包括在现代便携式移动设备中使用的应用处理器。

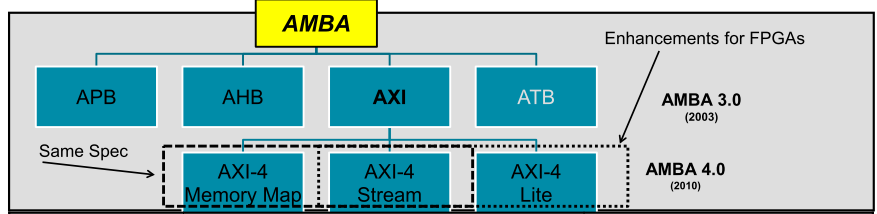

高级可扩展接口AXI(Advanced eXtensible Interface):是ARM公司AMBA 3.0 和AMBA 4.0规范的一部分,是并行高性能,同步,高频,多主机,多从机通讯接口,主要设计用于片上通讯。为啥说AXI是AMBA的一部分,看看下面两个图就可以比较清晰的了解。

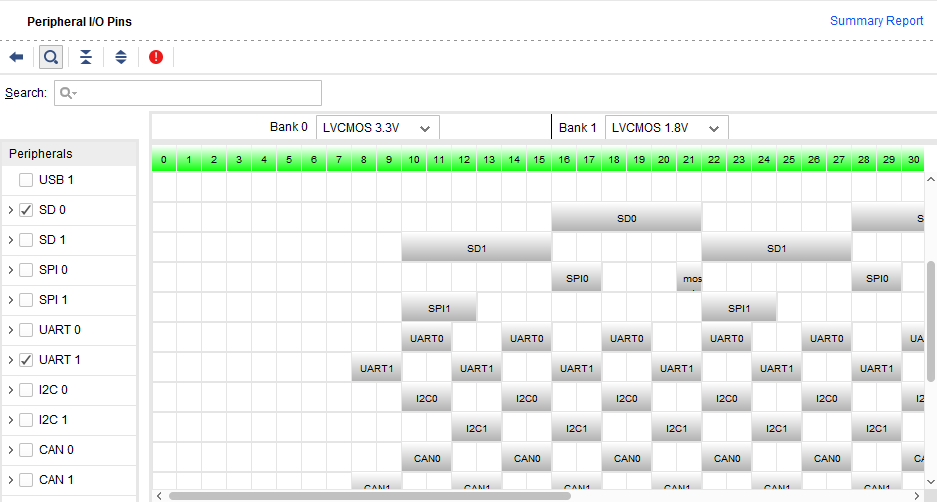

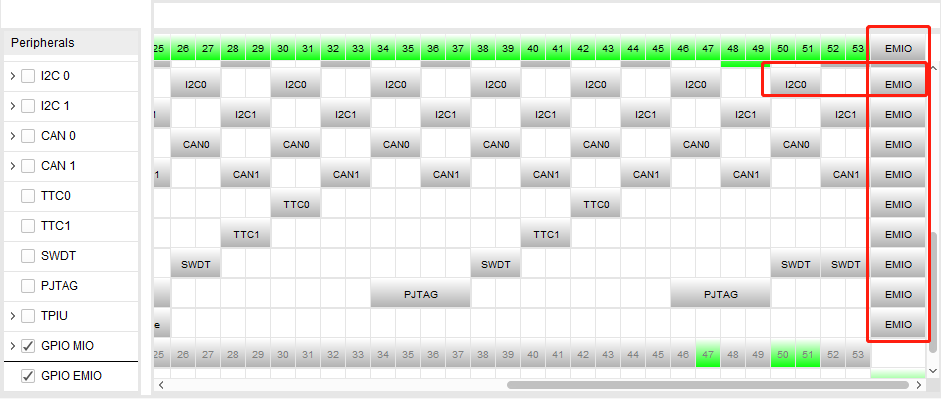

ZYNQ的高度灵活性灵活的PS端IO复用Multiplexed I/O (MIO):PS端外设IO复用,这是什么概念呢?前面介绍了ZYNQ主要分PS/PL两大组成模块,PS端前面介绍的外设如USB/CAN/GPIO/UART等都必要需要引脚与外界打交道,这里所谓的复用与常见的单片机、处理器里引脚复用的概念一样。但是(这里划重点),ZYNQ具有高达54个PS引脚支持MIO,MIO具有非常高的灵活度以达到灵活配置,这给硬件设计、PCB布板带来了极大的便利!,MIO的配置利用vivado软件可以实现灵活配置,如下图所示。

硬件工程师往往发现对一个复杂的系统的布局布线,常常会很困难,也常因为不合理的布局布线而陷入EMC深坑。ZYNQ的IO引脚高度灵活性,无疑在电路设计方面提供极大的方便,可实现非常灵活的PCB布局布线。从而在EMC性能改善方面带来了很大便利。

灵活的PS-PL互连接口Extended Multiplexed I/O (EMIO) :扩展MIO,如果想通过PS来访问PL又不想浪费AXI总线时,就可以通过EMIO接口来访问PL。54个I/O中,其中一部分只能用于MIO,大部分可以用于MIO或EMIO,少量引脚只能通过EMIO访问。

如上图,比如I2C0则可以通过EMIO映射到PL端的引脚输出,这无疑又增加了更多的灵活性!

PS-PL接口HP0-HP3:如上架构图中AXI high-performance slave ports (HP0-HP3) 实现了PS-PL的接口

可配置的32位或64位数据宽度

只能访问片上存储器OCM(On chip memory)和DDR

AXI FIFO接口(AFI)利用1KB FIFOs来缓冲大数据传输

PS-PL接口GP0-GP1:如上架构图中AXI general-purpose ports

两个PS主接口连接到PL的两个从设备

32位数据宽度

一个连接到CPU内存的64位加速器一致端口(ACP)AXI从接口,ACP 是 SCU (一致性控制单元)上的一个 64 位从机接口,实现从 PL 到 PS 的异步 cache 一致性接入点。ACP 是可以被很多 PL 主机所访问的,用以实现和 APU 处理器相同的方式访问存储子系统。这能达到提升整体性能、改善功耗和简化软件的效果。ACP 接口的表现和标准的 AXI 从机接口是一样的,支持大多数标准读和写的操作而不需要在 PL 部件中加入额外的一致性操作。

处理器事件总线信号事件信息到CPU

PL外设IP中断到PS通用中断控制器(GIC)

四个DMA通道RDY/ACK信号

扩展多路复用I/O (EMIO)允许PS外设端口访问PL逻辑和设备I/O引脚。

时钟以及复位信号:

四个PS时钟带使能控制连接到PL

四个PS复位信号连接到PL

灵活的时钟系统PS时钟源:

PS端具有4个外部时钟源引脚

PS端具有3个PLL时钟模块

PS端具有4个时钟源可输出到PL

PL端具有7个时钟源

PL端时钟源域相对PS端不同

PL端时钟可灵活来自PL端外部引脚,因为FPGA的硬可编程性,完全灵活配置

也可使用PS端的4个时钟源

注意

PL和PS之间的时钟同步是由PS端处理

PL不能提供时钟给PS使用

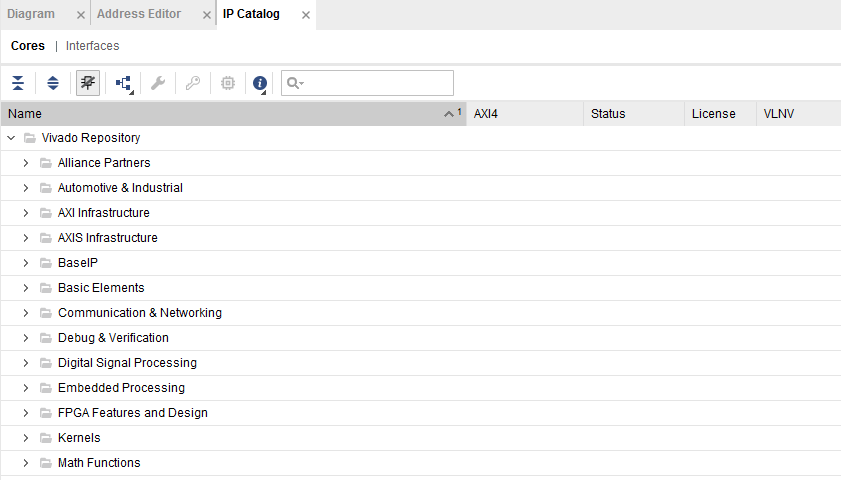

丰富的IP库Zynq 是一种SoC,具有大量的标准 IP,这些部件不再需要重新设计而直接可用。以这样的方式提升了设计抽象层级,加上重用预先测试和验证过的部件,开发将被加速,而成本则可以降低。就像常说的:“ 为什么要重新发明轮子呢?”。

Vivado内置了大量的IP可供使用,比如数学计算IP,信号处理IP、图像视频处理IP,通信互连(以太网、DDS、调制、软件无线电、错误校验)、处理器IP(MicroBlaze等)、甚至人工智能算法IP。

比如信号处理IP,由于采用FPGA硬逻辑实现信号处理无需CPU计算,对于实现复杂的信号运算(比如实现一个非常高阶的FIR滤波、多点FFT计算)具有非常大优势。

双ARM硬核处理器如架构图,ZYNQ内置了双ARM Cortex-A9硬核,对软件设计提供了极大的灵活性,在该处理器上可运行Linux,Android等复杂的操作系统,相比常规FPGA嵌软核IP的做法具有更强大的运算处理能力,你可能会说其处理器的运算能力相比时下的其他ARM芯片或稍有不足,但基本能满足常规的医疗、工业领域等嵌入式系统应用需求。

PL/PS的有机结合通过前面的简要分析介绍,不难发现PL可编程硬件逻辑及处理器单元的结合做的非常好。

PL端:可设计出高灵活的外设系统,同时可编程硬件逻辑电路,可实现真正的硬并行处理、硬实时系统

PS端:PL端与PS的有机结合,有可实现对这种高灵活、硬并行、硬实时处理系统实现集中软件管理

试想,如果一个系统需要实现硬实时、硬并行,复杂外设互连系统:

或许会采用多微控制器(比如单片机)+处理器方案,微处理器实现实时需求,处理器运行Linux实现上层业务逻辑的方式。

或者采用FPGA+处理器来实现。

这两种方案技术复杂度都非常高,硬件电路PCB设计比较复杂,软件开发以及维护也会增加复杂度。而ZYNQ则可以很好的解决此类系统设计需求,真正做到system on chip,这也是SOC的一个很好的体现。

总结一下ZYNQ这种高度灵活性,丰富的外设,丰富的IP库,以及vivado强大易用的开发环境,对使用ZYNQ进行嵌入式系统设计带来了非常多优势。

原文标题:从ZYNQ芯片架构谈谈其为何如此诱人

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

处理器

+关注

关注

68文章

19135浏览量

228947 -

FPGA

+关注

关注

1625文章

21648浏览量

601478 -

芯片

+关注

关注

453文章

50301浏览量

421411 -

嵌入式

+关注

关注

5064文章

18992浏览量

302582

原文标题:从ZYNQ芯片架构谈谈其为何如此诱人

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

对ZYNQ芯片架构的理解谈谈个人体会

对ZYNQ芯片架构的理解谈谈个人体会

评论