摘 要: 设计了一种基于EPF10KRC208-4的误码仪,该设计充分利用了FPGA强大的可编程能力和丰富的资源,以及软件开发平台Quartus Ⅱ的完备功能,具有体积小巧、携带方便、测量精确等优点。其核心部分分别采用了逐位比较法和移位寄存器法,并在仿真过程中设置了多种误码情况进行对比。最后,根据仿真结果分析了方案的可行性和两种方法的优缺点。

自20世纪下半叶以来,信息技术的飞速发展在军事领域掀起了军事变革的浪潮,使武器装备、作战模式和作战理论的本质发生了深刻变化。信息技术促进了卫星通信、光纤通信等现代通信手段与现代侦查监视系统、计算机网络和武器控制的结合,实现了情报、通信、指挥与控制一体化的情报指挥控制系统(C3I系统)正改变着传统的作战模式,使战争形态由机械化战争转变为信息化战争。

随着通信技术的不断发展,数字通信正在逐步取代模拟通信成为主要的通信方式。而误码是影响数字通信系统最重要的因素,因为误码直接破坏了信息传递的正确性。然而在信息化战场上,存在各种各样复杂的干扰,人为干扰如雷达波、各种电器开关通断产生的短脉冲等的电磁波,敌方的电子干扰、各种干扰弹、机动马达和炮击爆炸等电磁辐射,还有非人为的雷电、宇宙辐射、邻近通信系统等的干扰,这些干扰往往是导致信道产生误码的最重要因素。

为了正确地评估战场环境下通信系统的性能,本文研究了基于FPGA的误码仪设计,采用FPGA使设计具有结构小巧,携带方便等优点,其核心部分的设计分别采用了逐位比较法和移位寄存器法。

1 基本原理

设计过程中FPGA开发环境采用Altera公司的开发软件Quartus Ⅱ 9.0,它集成逻辑分析、功率分析、时序优化和EDA工具等功能,使设计变得十分简洁。

1.1 逐位比较法的基本原理

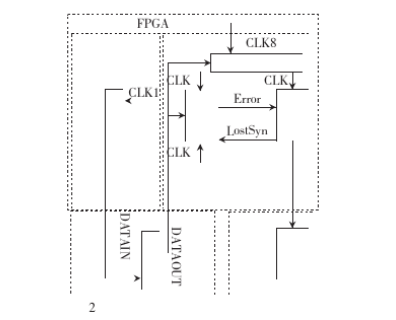

逐位比较法误码仪示意图如图1所示,误码仪由发送和接收两部分组成[3]。发送部分由码型发生器组成,Select为测试码类型选择输入,接收部分由时钟同步器、本地码产生器、逐位比较器和误码统计模块组成。

其原理为:在低频时钟CLK1的驱动下,将码型发生器生成的测试码m序列输入到被测信道,然后由接收端接收,并提取时钟同步器进行时钟同步。在8倍高频时钟CLK8的驱动下,提取数据流的时钟信号。时钟同步完成后,位同步器输出频率同CLK1的同步时钟CLK一致,其上升沿对准接收数据的中间部分,以保证接收数据的正确性。

m序列经过被测信道后,进入接收端的本地码产生器和逐位比较器。接收端把接收到的m序列前N个码元(N为m序列发生器级数)对本地码产生器进行灌码,并把所灌码作为本地产生器的初值。本地码产生器的结构与发送端的码型发生器结构相同,因此,如果所灌码正确,就可以产生与发送端完全一致的m序列,该序列与接收到的数据在逐位比较器中进行逐位比较。

如果测试数据在传输中有误码,则在逐位比较过程中可以检测出来。逐位比较器将检测到的误码信号传输给误码统计模块,该模块的功能是进行误码数累计,累计的数据传送给计算显示模块。当一段时间内误码数量超过所设上限,则该模块给出失步信号LostSyn,说明此时系统失步,统计的误码数据无效,需重新同步。失步信号LostSyn使本地码产生器重新进行灌码,并产生新的本地序列。后续步骤同上。

1.2 移位寄存器法的基本原理

移位寄存器法误码仪的示意图如图2所示,误码仪的设计也包括发送部分和接收部分。发送部分由码型发生器组成,接收部分由时钟同步器、误码检测器和误码统计模块组成。码型发生器与上一种方法工作方式不同,在同一次测试中要先后产生两种码型,先产生时钟同步码,再产生m序列。时钟同步码只用于接收端时钟提取,时钟同步器工作原理与第一种方法相同。时钟同步后时钟同步器发出Syn信号通知码型发生器产生m序列,这样可以避免测试数据的丢失,保证误码检测的正确性。

该方法的最大特点是用一个误码检测器代替了上一种方法的本地码产生器和逐位比较器。当时钟同步后,m序列经过被测信道直接进入接收端的误码检测模块进行误码检测,而不需要再产生本地码,这种设计方法的优点是抗干扰能力更强,设计也简单;缺点是占用FPGA资源多,耗用83%的逻辑单元,设计多种码型时占用资源更是明显增多。而逐位比较法对FPGA资源要求不高,仅占13%的逻辑单元,容易实现多种码型测试。误码统计模块的工作原理与前一种方法相同。

2 设计方法

2.1 逐位比较法的设计方法

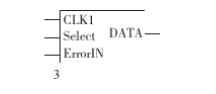

码型发生器模型图如图3所示,其核心为m序列发生器。其中,CLK1为产生测试数据的基准时钟;Select为码型选择输入端,在这里设计了两种码型,通过控制Select端状态来实现测试码型的切换;ErrorIN为手动误码输入端,该端连接一个按钮,按一次按钮产生一个误码;DATA为数据输出端口。

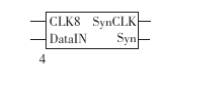

图4为时钟同步器模型,其核心为一个抽样电路。CLK8为8倍高频时钟输入端,DataIN为数据输入端,SynCLK为同步时钟输出端,Syn为时钟同步标志位。设计的方法为:数据输入端DataIN作为抽样电路的控制端,高电平时抽样电路工作,在一个周期内抽样电路需进行3点抽样,当输入数据的宽度无法满足3点抽样时,视为干扰,继续进行时钟同步搜索。当3点抽样皆为高电平时,才视为正常数据,使该模块输出同步时钟和时钟同步标志位。该同步时钟作为接收端后续电路的时钟信号。

图5为本地码产生模块模型图,其核心为灌码电路设计和m序列发生器。CLK为时钟输入端(后续模块相同),DataIN为数据输入端,Reset为复位端,DATA为本地码输出端。灌码电路设计的关键是,在进行灌码时,将m序列发生器(最长线型反馈移位寄存器)的循环回路断开,使其成线性移位寄存器;当灌码完成后,将m序列发生器循环回路接通,此后,DataIN输入的数据无效,即可按照所灌初值自行产生m序列。当出现失步或者手动复位时,复位信号从Reset端输入使该模块重新进行灌码操作。

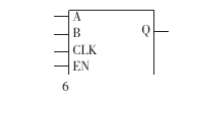

图6所示为逐位比较器模型图,其核心为一个异或门和相应的时延电路。其中A为本地码输入端;B为接收数据的输入端,其在内部需要经过一定的时延,再跟A端数据接到异或门;EN为使能端。若出现误码,则在某时刻B端的码元跟A端的码元相异,经过异或门后输出一个高电平,其他相同的码元经过异或运算后输出为低电平,这样就能判别误码的情况了。Q即为误码输出端,高电平表示有误码,一个时钟的高电平表示有一个误码。

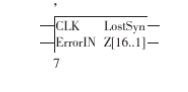

图7为误码统计模块模型图,其核心为高电平到窄脉冲的转换电路和误码计数电路。其中ErrorIN为误码信号输入端,其在内部经过转换电路转换为窄脉冲信号;LostSyn为失步信号输出端;Z[16..1]为误码统计数据输出端。在给定时间内误码数量达到上限,则给出失步信号。失步信号通过一个8位计数器给出,该计数器8位输出连接到一个8位与非门,通过改变连接方法可以设置0~255的任何一个定时值。另外,在其内部设计一个清零电路,清零周期即为所设时间段,每个周期结束时的一个时钟清零电平将计数器清零,以保证每个周期从零计数。误码数据统计器为16位计数器。

2.2 移位寄存器法的设计方法

移位寄存器法的时钟同步器和误码统计模块的设计方法与上一种方法相同。下面仅介绍一下码型发生器和误码检测器的设计。

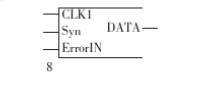

图8为码型发生器模型图,其核心为m序列发生器和方波发生器。其模型图跟逐位比较法的不同之处在于输入端没有Select端,而有Syn端。Syn信号来自时钟同步器的同步标志位Syn。该输入通过控制一个开关电路来达到切换方波发生器和m序列发生器的目的。由于移位寄存器设计方法耗用资源多,不适合设计多种码型,这里仅设计了一种m序列发生器,所以没有Select端。当然,如果不考虑成本,也可以设计多种码型。

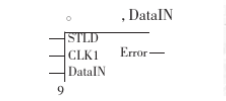

图9为误码检测器模型图,其核心为一个串入并出移位寄存器和一个并入串出移位寄存器。其中,DataIN为数据输入端,STLD为并入串出移位寄存器的移位加载端,Error为误码输出端。

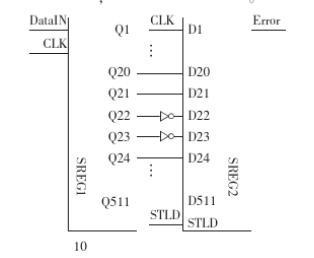

图10为误码检测器设计思路示意图。m序列每一周期的排列规则是固定不变的,即每个周期中的对应位都是相同的。移位寄存器法就是利用了这种周期性。假设该方法设计的码型为511码,又设每个周期的第20~24位的排列是“11001”,则移位寄存器对应位设计如图10所示。按照这种设计方法,当一个周期的511个码元正好出现在SREG1的输出端口上时,如果传输的码元无误码,则SREG2的输入端口全是低电平,否则,对应的高电平即为误码,此时给STLD端口一个低电平,则将SREG1的511个输出数据经过上述处理后加载到SREG2。SREG2在CLK的驱动下,将加载进来的数据从Error端口串行输出,高电平即代表误码。

3 仿真分析

下面利用Quartus Ⅱ开发平台对上述两种方法在给定多种条件下进行时序仿真,并进行分析。

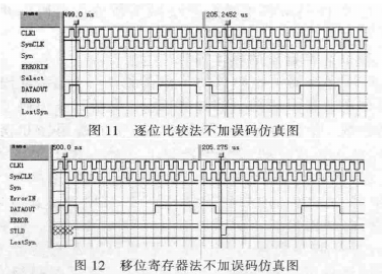

图11、图12所示是在没有手动加入误码的情况下(即ErrorIN为低电平)两种方法的仿真截图,所用码型皆为511码,所用时钟频率相同,分别在两个不同的时间段进行了截取。从图11、图12可以看出,逐位比较法在时间t=499.0 ns处完成了时钟同步,移位寄存器法在时间t=500 ns处完成了时钟同步,在所给时间段内,两种方法的误码输出皆为低电平。对于移位寄存器法,在时间t=205.275 ?滋s处移位加载端STLD加载有效,把一个周期的511个码元经过处理后同时加载到SREG2,此后每隔一个周期就给出一个加载有效信号。

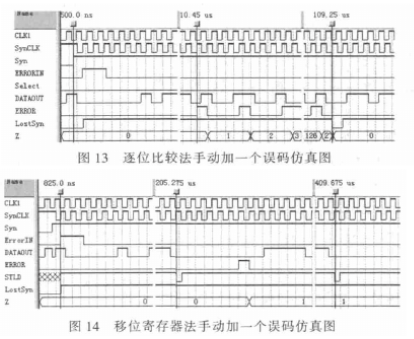

图13、图14所示是手动加了一个误码的情况下两种方法的仿真截图,码型和频率同前,分别在3个不同时间段进行了截取。由图13、图14可以看出,在时钟同步之后,ErrorIN有一段高电平,此操作即给测试码手动加入了一个误码。在此必须注意,加入的误码是落在测试码的前9个码元之内的。对于逐位比较法,这种误码将会使逐位比较法灌码码元出现误码。如图13所示,在时间t=10.45 ?滋s之后连续出现了误码,直到t=108.85 ?滋s误码数在设定时间内达到了上限,系统判断为失步并给出LostSyn信号后,又重新进行灌码等一序列操作,才使误码数归零,继续进行测试。而逐位比较法则可以正确地检测出误码。

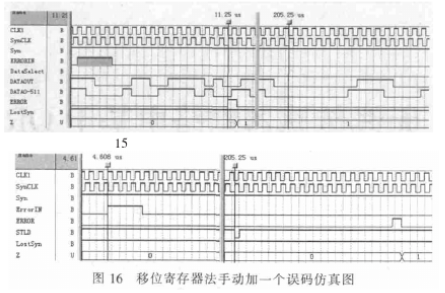

图15、图16也是手动加了一个误码的情况下两种方法的仿真截图,截取了两个时间段。与前一仿真相比,所给条件唯一不同就是加入的误码落在测试码的前9个码元之外,即逐位比较法首次灌码码元正确。由图15、16中可以看出,在给定条件下,两种方法都没有出现失步现象,而且都能正确检测出误码信息。结果说明,逐位比较法能否正确检测出误码,取决于所灌码元正确与否,也即抗干扰能力差,如果出现连续的灌码码元误码,则也会连续出现失步现象。而移位寄存器法不会出现这个问题。

通过对误码仪两种实现方法的设计、仿真与分析可以看出,逐位比较法耗用逻辑单元少,扩展性能也好,适合设计多种PN码的测试。但它的抗干扰能力也相对较差,一旦灌码码元出现误码,则后续测试会出现一连串误码,导致测试结果错误,直到系统判断为失步,才能再次进行灌码操作,重新测试。而移位寄存器法的抗干扰能力好,但耗用资源多,不适合多种PN码测试的设计。结果表明,两种方法都是可行的,但各有优缺点,在实践中可以根据实际需求进行选择。

参考文献

[1] 樊昌信,曹丽娜。通信原理(第六版)[M]。北京:国防工业出版社,2006.

[2] 褚振勇,齐亮,田红心,等.FPGA设计及应用[M]。西安:西安电子科技大学,2006.

[3] 李斌。基于FPGA的误码仪的研究与设计[D]。武汉:武汉理工大学,2006.

[4] 吴继华,王诚.Altera FPGA/CPLD设计(初级篇)[M]。北京:人民邮电出版社,2005.

编辑:jq

-

FPGA

+关注

关注

1629文章

21735浏览量

603195 -

EDA工具

+关注

关注

4文章

267浏览量

31793 -

开发软件

+关注

关注

1文章

25浏览量

12935

发布评论请先 登录

相关推荐

ADS1292R有 \"1 ch ECG + 1 ch呼吸侦测\" 或 \"2 ch ECG\" 两种模式,是否可以在产品上实现自行切换两种使用模式?

晶闸管的阻断状态有两种是什么

wdm设备的两种传输方式

控制器有哪两种实现方式?各有何优缺点?

GYFTA、GYFTY两种光缆的区别

异或门两种常见的实现方式

什么是浪涌电流,关于浪涌抑制的两种方案

一种关于FPGA的两种误码仪实现方法设计

一种关于FPGA的两种误码仪实现方法设计

评论