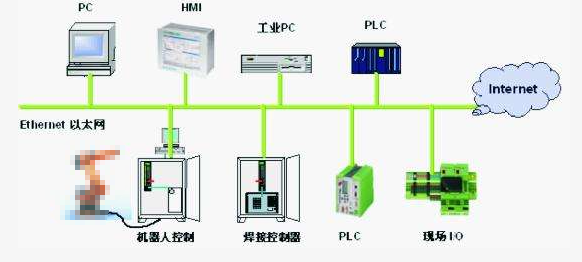

以太网IP核的1588功能是用来实现,在IP内部为TX侧发送包打上发送出去这个时间节点的时间戳,以及获得RX侧收回来的包在IP接口处的时间戳。然而10G/25G的IP例子工程没有提供演示,本文主要介绍了如何使用这个IP的1588功能

产生一个例子工程的仿真

01

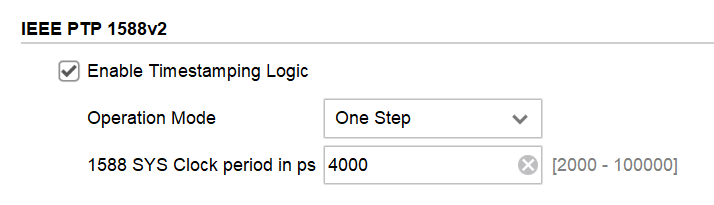

1. 打开Vivado新建工程,添加一个10G/25G以太网IP core,注意在IP的GUI里勾上1588功能(如图),然后右键产生example design

为了能同时支持 1-step 和 2-step,这里在产生 IP 时选择了“OneStep”的 1588

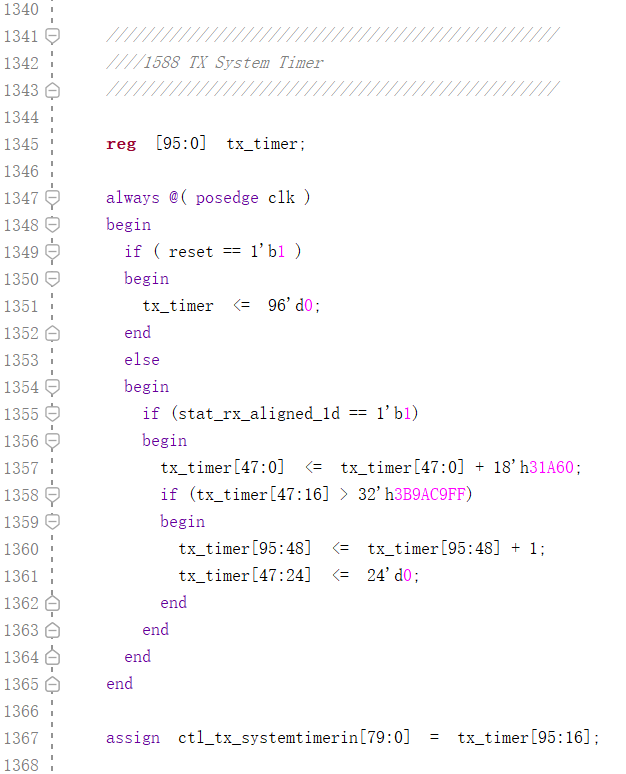

2. 工程产生完成后,需要先给 tx/rx_systemtimer 加上参考时间值。如果用的是 2020.2,新的 IP 例子工程已经自带了 timer_syncer 模块,为 systemtimer 提供输入。但如果用的是之前的版本,你只需要写一个计数器的逻辑,输出为标准时间 ns 计数,提供给 systemtimer 输入就行了,到时候 IP 在发出包的那一刻,会把 tx_systemtimer 当时的值作为时间戳使用,或者在收到包的那一刻,把当时的 rx_systemtimer 的值拿来使用

下面是一个简单的计数器代码示例,选自 100GCMAC 的 IP 参考设计中产生 tx_systemtimer的逻辑,供参考使用

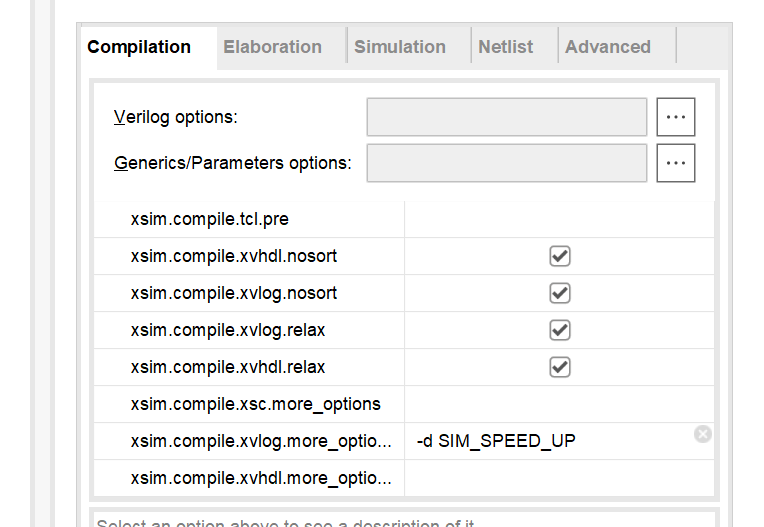

3. 最后给工程加上仿真选项,帮助加速仿真速度,就可以开始做工程的功能仿真了

如何使用1588功能

02

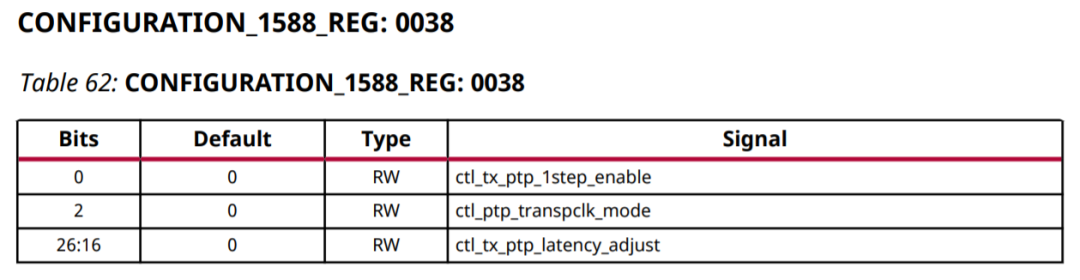

1. 首先使能IP的1588的1-step功能,可以在逻辑里将IP的输入“ctl_tx_1step_enable”置1,如果使能了IP的AXI读写寄存器接口的话,也可以将地址0038的bit0写1

2. 同样地方式,通过修改信号 “ctl_ptp_transpclk_mode”选择OrdinaryClock模式或者TransparentClock模式。在OC模式下,时间戳会直接覆盖原以太网包里的值,但在TC模式下,时间戳则会叠加在原来位置的数值上面。具体可参考1588协议

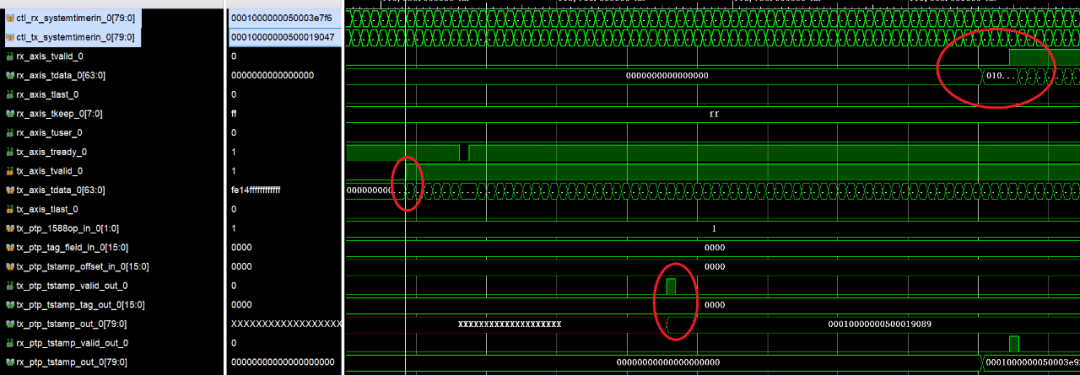

3. 接着跑仿真,先在设计逻辑里将 “tx_ptp_1588op_in”接为01,观察1-step模式下的IP的工作行为,仿真结果如下图示

由于这里的 “tx_ptp_tstamp_offset_in”为0,发送包的第一拍数据 “tx_axis_tdata”会从原来的值“fe14ffffffffffff”被IP替换成时间戳,也就是在RX侧看到收到的数据包的第一拍数据“rx_axis_tdata”已经变成了 “010005xxxxxxxxxx”

实际上 IP 在 1-step 工作模式下,2-step也是同时工作的,对应 “tx_ptp_tstamp_valid_out” 拉高的“tx_ptp_stamp_out” 的值,就是这个包的时间戳,输出给客户,这个时间戳的值客户可以自行稍加修改添加到下一个包再发出去,这就是 2-step 的工作模式

用于2-step的“tx_ptp_stamp_out”和填进包里的1-step时间戳略有区别,差距就是 “ctl_tx_ptp_latency_adjust”,差异的原理细节可参考 IP 的文档 PG210

用户可以自行给他发的每个包输入不同的“tx_ptp_tag_field_in”值,然后当IP输出 “tx_ptp_stamp_out” 时间戳的时候,只要找到对应的 “tx_ptp_pstamp_tag_out” 值,就是相同 tag_in 对应的那个包的时间戳

RX 侧收进包的时间戳,为 "rx_ptp_stamp_out”,目前时间戳的点都是 IP 的接口,所以在环回仿真里面,RX 侧的时间戳会比TX侧的时间戳大,差了一整个 GT 的延时没有计算进去,用户应当在AR搜索中找到自己用的器件对应GT的具体latency,静态延时值可通过ctl_tx/rx_latency 信号合进 IP。并且,延时结果能在功能仿真里面体现出来

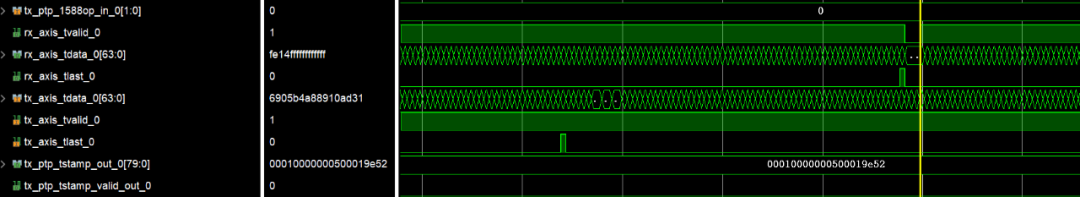

4. 最后你还可以随时在逻辑里修改 "tx_ptp_1588op_in" 的输入,当接为 00 或者 10 的时候,IP 就不会再自动打上时间戳,第一拍保留了数据包的原始数据 "fe14ffffffffffff”,并且如果1588op=00 的时候,"tx_ptp_tstamp_valid_out" 也不会再拉高,如下图

原文标题:开发者分享 | 如何使用 10G/25G 以太网 IP core 上的 1588 功能

文章出处:【微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

以太网

+关注

关注

40文章

5373浏览量

171044 -

IP

+关注

关注

5文章

1643浏览量

149323

原文标题:开发者分享 | 如何使用 10G/25G 以太网 IP core 上的 1588 功能

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

以太网和TCP/IP的关系解析

以太网帧格式和功能详解

以太网端口的类型和特性

以太网要怎么连接

解读工业以太网标准:Profinet与EtherNet/IP

以太网无法连接外网IP,提示No route to host,为什么?

如何使用以太网交换机最大限度地减少网络延迟

用于IEEE 1588和同步以太网的82P33814同步管理单元评估板数据手册

车载以太网 | TSMaster的DoIP功能操作指南

如何使用以太网IP核的1588功能?

如何使用以太网IP核的1588功能?

评论