0 引言

飞行器的工作状态参数和环境参数主要通过无线遥测和回收遥测获得,是评定飞行器性能和分析飞行器故障的依据[1]。随着航天技术的发展,飞行器内部的工作参数越发复杂,遥测数据的信息量越来越大,遥测系统现有的存储能力和信道带宽已经很难满足如此大数据量的存储、传输要求。考虑到技术、成本等条件的限制,一味增加信道带宽和存储器的容量是不现实的。目前,数据压缩技术被广泛应用于遥测系统[2]。根据遥测数据的特点,采用合适的算法对大数据量的遥测数据进行编码压缩,不仅减轻了遥测系统数据存储的压力,也降低了对信道带宽的要求,提高了通信效率。

遥测噪声信号的频率和幅度变化很大且无规则,信号的相关性差,为反映信号的完整特性,需要较高的采样频率,这样就会产生很大的数据量。为有效地完成对噪声信号的测量,这里采用ARC(算术编码)算法对噪声数据进行无损压缩,以DSP+FPGA为硬件平台[3],充分利用FPGA高速、并行的特性和DSP在算法实现上的优势,很好地实现了对遥测噪声数据的实时、无损压缩。

1 系统设计

系统整体设计框图如图1所示,由噪声传感器采集的噪声信号经调理电路滤波、放大后,进行A/D转换得到量化噪声数据;FPGA将噪声数据写入内部8 KB FIFO,直到FIFO达到半满[4],DSP才会读取噪声数据进行算术编码;编码压缩后的噪声数据先是被DSP缓存至SDRAM,然后通过McBSP串口发送到FPGA,FPGA通过内建的4 KB FIFO对接收的压缩数据进行缓冲;422通信控制模块会接收读数命令并在4 KB FIFO达到半满时按照HDLC协议的要求将压缩数据传输到外部设备进行存储、传输和分析等操作。

2 数模转换电路设计

噪声信号的模数转换采用TI公司的ADS8365芯片实现。它是16位6通道并行A/D,最高采样率可达250 kS/s,完全满足对4路噪声信号进行27 kHz采样的要求。

ADS8365的6个模拟输入通道可分为3组,分别为A、B和C组[5]。每组都有一个保持信号(分别为HOLDA、HOLDB和HOLDC),用于启动各组的A/D转换。6个通道可以进行同步并行采样和转换。当ADS8365的HOLDX保持20 ns的低电平后开始转换。当转换结果被存入输出寄存器后,引脚EOC的输出将保持半个时钟周期的低电平,以提示FPGA进行转换结果的接收,FPGA通过置RD和CS为低电平使数据通过并行输出总线读出。

ADS8365的数据的读出模式有3种,分别是:直接地址读取、FIFO读取、循环读取,是由地址/模式信号A0、A1和A2来选择的[6]。本系统FPGA将数据读出配置为FIFO读取模式。A/D转换电路如图2所示。

3 FPGA与DSP通信设计

FPGA控制ADS8365完成对4路噪声信号的A/D转换,各路量化数据加入通道标志后依次写入FPGA内部FIFO。当FIFO达到半满后,通知DSP读取2 048 B数据进行编码,编码时间最长为40 ms,平均20 ms。DSP在编码过程中不能与FPGA进行数据通信,FPGA要对由A/D产生的量化数据进行缓存。按最长耗时40 ms计算,每路27 kHz的采样率会产生为4.32 K个采样点。采用16位FIFO,则FIFO的深度应大于4 320,这里为增加可靠性,设计FIFO深度为8 192。

FPGA内部FIFO由Block RAM构建,其与DSP EMIF接口的连接如图3所示。

噪声数据经DSP压缩后可以通过并行EMIF总线传输至FPGA。但为降低数据传输误码率,提高系统稳定性,本设计采用DSP的McBSP0串口将压缩后的数据以串行数据流的方式传送至FPGA。McBSP0传输单元的大小设置为48 bit,包括4 bit起始位、32位数据位和12 bit停止位。FPGA将串行接收的压缩数据转换成8 bit并行数据并将其写入到内部4 KB FIFO中。FPGA通过422接口与外部设备通信,在接收到读数命令后判断4 KB FIFO是否达到半满。如果FIFO达到半满,就读取FIFO中的数据,并进行HDLC协议编码和帧格式编码后发送出去;否则采用填充帧技术,将预先定义好的一组固定帧结构数据发送给外部设备。

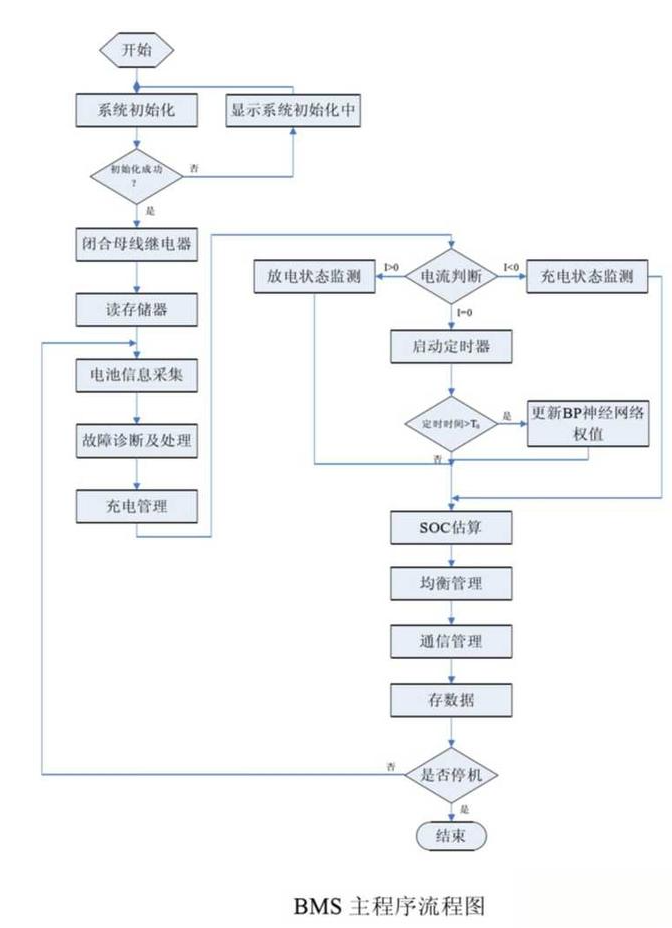

4 DSP程序设计

基于C语言的各种常见压缩算法的开发都已很成熟,ARC算法的源程序也容易调研,算法的具体实现过程在此不再赘述。本设计将ARC源程序移植到DSP中实现算法的压缩功能,DSP上电启动或者复位后,从 Flash中加载程序,进入主函数main()完成外部FIFO数据读入、启动ARC压缩,读写SDRAM和数据输出等工作工作。程序流程如图4所示。

当DSP检测到外部8 KB FIFO半满信号后会读取2 048 B噪声数据到内部4个缓存中,由于4路噪声信号采样时仅相差一个采样点,故各路噪声数据相差一个字节。DSP内4路噪声数据对应的缓存几乎同时达到2 048 B, DSP需要同时对4路噪声数据进行编码,这会使DSP长时间处于繁忙状态而不能进行采样数据的读入和压缩数据的输出,容易引起FPGA内部8 KB FIFO溢出和4 KB FIFO的读空。

如果采用中断方式打断压缩进程、读入量化数据和输出压缩数据,则可能造成DSP内数据量过大,超出DSP片内RAM容量。这里将DSP内的4个缓存预设初值分别设为1 536 B、1 024 B、512 B和0 B,DSP每次从FPGA内部FIFO中读取2 048 B数据,则DSP内每个缓存增加512 B。DAP第一次读取FIFO,第一路噪声数据对应的缓存达到2 048 B,进行编码、输出后,该缓存数据量变为0。

此时,4路缓存中的字节数变为0、1 536、1 024和512。DSP第二次读取FIFO后,第2路数据缓存达到2 048 B,完成对第二路噪声数据的编码、传输。如此循环执行,实现每次只对一路噪声数据进行处理,保证了数据的连续均匀流动。

5 测试验证与分析

采用测试系统对设计的噪声压缩装置的性能进行了验证,测试系统的测试台向噪声压缩装置提供4路信号来模拟噪声传感器的输入,噪声压缩装置对输入信号完成压缩后将数据回传给测试台并由测试台将压缩数据上传至上位机。上位机对压缩数据先进行数据结构分析,如果数据结构正确,就按照HDLC协议将数据解码并去除填充数据和帧标识。之后根据ARC算法将噪声数据解压还原并分离得到各路噪声原始数据,上位机对各路噪声原始数据进行处理,还原出各路信号的原始波形。

给噪声无损压缩装置的噪声信号输入接口输入信号,其中第1路为幅值2 V、频率25 Hz的正弦波,第2路为幅值3 V、频率25 Hz的正弦波,第3路为幅值2 V、频率50 Hz的正弦波,第4路为幅值2 V、频率25 Hz的矩形波。测试结果如图5~图8所示。

从测试结果可以看出,同一种信号幅值、频率不同,它们的压缩去除率会存在差异;幅值、频率相同,不同种类信号的压缩去除率也会不同。对标准信号源,该压缩装置的压缩去除率接近90%。图9为噪声压缩装置对实际噪声信号压缩后由上位机还原得到的波形,可以看出该压缩装置对实际噪声信号的压缩去除率能达到50%以上。

6 结论

数据压缩技术在遥测系统中对包括噪声信号在内的速变参数的处理已经很常见,本文设计的系统以FPGA+DSP为硬件核心,其中,FPGA主要完成对模/数转换和数据通信的控制,噪声数据的编码无损压缩则是在DSP中实现的。同时,采用不同信号对设计的噪声压缩装置进行了测试,得到了理想的效果。本文提出的设计思路对其他类型数据的压缩也有一定的借鉴意义。

参考文献

[1] 谢红卫,张明.航天测控系统[M].长沙:国防科技大学出版社,2000.

[2] 刘文怡.遥测速变数据无损压缩时空性能优化设计与应用[D].太原:中北大学,2009.

[3] 冷佳鹏,刘文怡.一种遥测数据实时压缩系统[J].电子技术应用,2013,39(4):72-74.

[4] 孟楠,杨岩飞,刘文怡.遥测速变数据实时无损压缩技术研究[J].科学技术与工程,2013,13(33):9983-9986.

[5] 张峰,赵慧昌,石现峰.便携式多通道振动信号分析仪数采模块设计[J].自动化与仪表,2014(1):15-18.

[6] 康伟,路秀芬,詹哲军.基于ADS8365的高速同步数据采集系统[J].电脑开发与应用,2009,22(4):48-51.

编辑:jq

-

传感器

+关注

关注

2550文章

51035浏览量

753072 -

FPGA

+关注

关注

1629文章

21729浏览量

602986 -

噪声

+关注

关注

13文章

1120浏览量

47400

发布评论请先 登录

相关推荐

分析遥测噪声数据无损压缩关键技术实现

分析遥测噪声数据无损压缩关键技术实现

评论