在FPGA设计中,我们遵循的原则之一是同步电路,即所有电路是在同一时钟下同步地处理数据。这个概念可进一步展开,即不局限于同一时钟,只要时钟之间是同步关系(两者之间有明确的相位延迟,例如同一个MMCM生成的时钟),这是因为目前的芯片规模越来越大,设计越来越复杂,往往需要多个时钟同时运算。

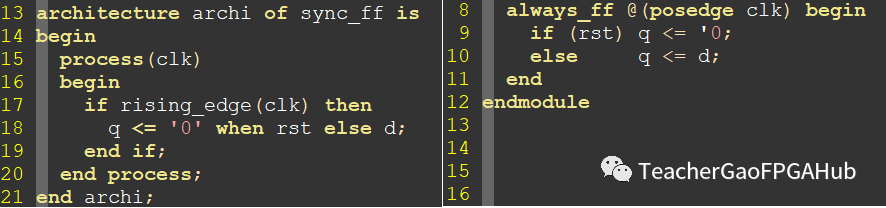

通常,我们说某个信号与指定时钟同步,意味着这个信号是由该时钟驱动的逻辑生成的,或者这个信号只有在时钟有效沿(一般是上升沿有效)下才会被触发。以复位信号为例,就有同步复位和异步复位之分。我们从HDL代码角度看一下二者的区别。如下图所示代码,描述的是同步复位触发器,左侧为VHDL-2008版本的描述方式,右侧为System Verilog版本的描述方式。可以看到敏感变量列表(左侧第15行,右侧第8行)中只有时钟clk,因此,进程中的状态变化就依赖于时钟的变化即时钟有效沿。

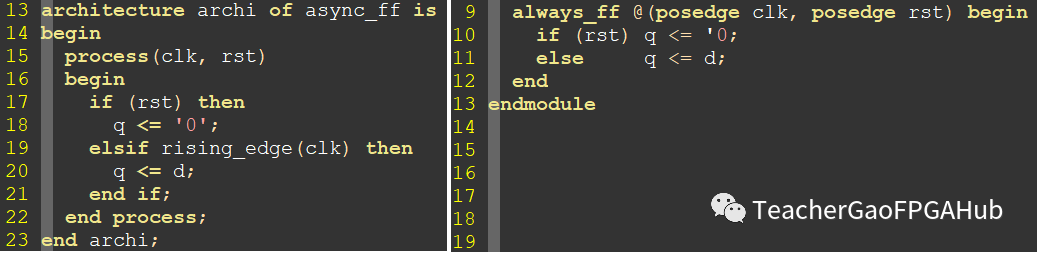

我们再看看异步复位是如何描述的,如下图所示。左侧是VHDL-2008版本,右侧是System Verilog版本。可以看到,此时敏感变量列表中除了时钟clk之外还有复位信号rst。在VHDL版本中,可以明确地看到复位信号位于if条件分支,而时钟有效沿位于elsif分支,优先级低于复位信号。因此,这里只要复位有效,无论时钟沿是否有效都会触发操作。

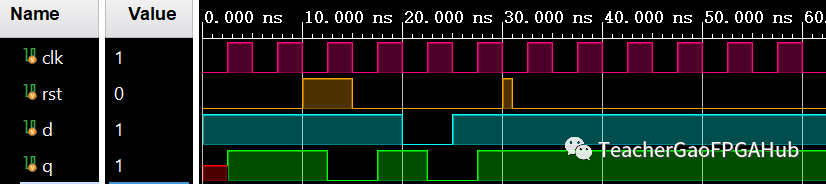

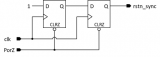

进一步,我们从仿真角度看看这两者的区别。同步复位触发器的仿真结果如下图所示。可以看到复位信号只有在时钟有效沿下才起作用。图中第二个复位脉冲并没有被时钟有效沿采到,故不会导致触发器复位。

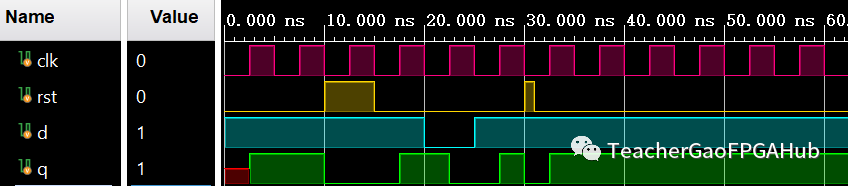

异步复位触发器仿真结果如下图所示。可以看到第二个复位脉冲尽管没有在时钟有效沿下,但仍促使触发器复位。这正是异步的原理。

对比两个仿真结果,我们可以看到同步复位的一个明显的好处就是利用了时钟的过滤功能,去除了复位信号上的毛刺,而异步复位下,如果复位信号有毛刺就会导致触发器误操作,这在状态机电路中尤为严重,很有可能导致状态机进入无效状态。

编辑:lyn

-

仿真

+关注

关注

50文章

4102浏览量

133746 -

同步复位

+关注

关注

0文章

27浏览量

10730 -

异步复位

+关注

关注

0文章

47浏览量

13328

原文标题:同步复位与异步复位

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA复位的8种技巧

复位电路介绍 复位电路的原理及作用

STM32复位电路用复位芯片和阻容复位电路区别

FPGA同步复位和异步复位

L431采用PLL异步时钟,复位后ADC采样值发生偏差的原因?

ABB变频器怎么复位 | 复位时可能会出现哪些问题?

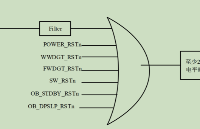

什么是复位同步电路 reset synchronizer?

异步复位异步释放会有什么问题?FPGA异步复位为什么要同步释放呢?

关于同步复位与异步复位的仿真详解

关于同步复位与异步复位的仿真详解

评论