芯来科技为方便客户进行基于鸿蒙生态的RISC-V软件开发,在Nuclei RISC-V 32位处理器上移植并适配了鸿蒙LiteOS-M内核。

目前该内核已可支持Nuclei Demo SoC——FPGA评估软核,和基于芯来科技的RISC-V内核的MCU——GD32VF103。

LiteOS-M内核

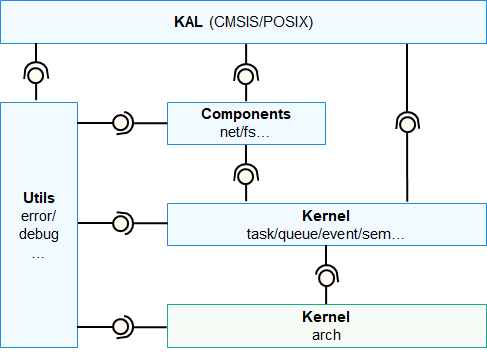

OpenHarmony LiteOS-M内核针对MCU类处理器,例如Arm Cortex-M、RISC-V32位的设备,面向AIoT领域构建的轻量级物联网操作系统内核。此内核具有小体积、低功耗、高性能的特点。其代码结构简单,主要包括内核最小功能集、内核抽象层、可选组件以及工程目录等,分为硬件相关层以及硬件无关层,硬件相关层提供统一的HAL(Hardware Abstraction Layer)接口,提升硬件易适配性,满足AIoT类型丰富的硬件拓展。

OpenHarmony LiteOS-M核内核架构图

芯来开发板

芯来科技目前有两款开发板可以快速体验最新鸿蒙LiteOS-M内核:

Nuclei DDR200T——集成了FPGA和通用MCU的RISC-V评估开发板,以及RV-STAR——基于GD32VF103 MCU的RISC-V评估开发板。

Nuclei DDR200T开发板采用12V外部直流电源,包含一个MCU子系统和一个FPGA子系统。

FPGA子系统采用Xilinx XC7A200T-2 FPGA芯片,并且提供板载FPGA JTAG下载器,不需额外配置FPGA下载器即可完成内核的烧写。此外,开发板还提供丰富的板载存储(Flash,DDR, eMMC, EEPROM)和丰富的接口资源(数字,模拟),以及蜂鸟调试器接口,方便下载调试。

Nuclei Demo SoC(FPGA评估软核)就可以烧写在这块FPGA子系统上运行。

NucleiRV-STAR开发板

Nuclei RV-STAR开发板采用GD32VF103VBT6微控制器,结合芯来科技Bumblebee内核,内置128KB Flash、32KB SRAM。开发板外设资源众多,包括:

Timer(高级16位定时器*1,通用16位定时器*4)、U(S)ART*5、I2C*2、SPI*3、CAN*2、USBFS*1、ADC*2(16路外部通道)、DAC*2、EXMC*1。开发板还提供大量接口,包括:USB Type-C接口、Micro USB接口、microSD卡插槽(默认没焊接)、JTAG接口、PMOD接口*2(SPI、I2C)、双排标准2.54mm排母接口:Arduino兼容接口(外侧),EXMC扩展接口(内侧)以及用户按键*2(复位、唤醒)。

芯来内核

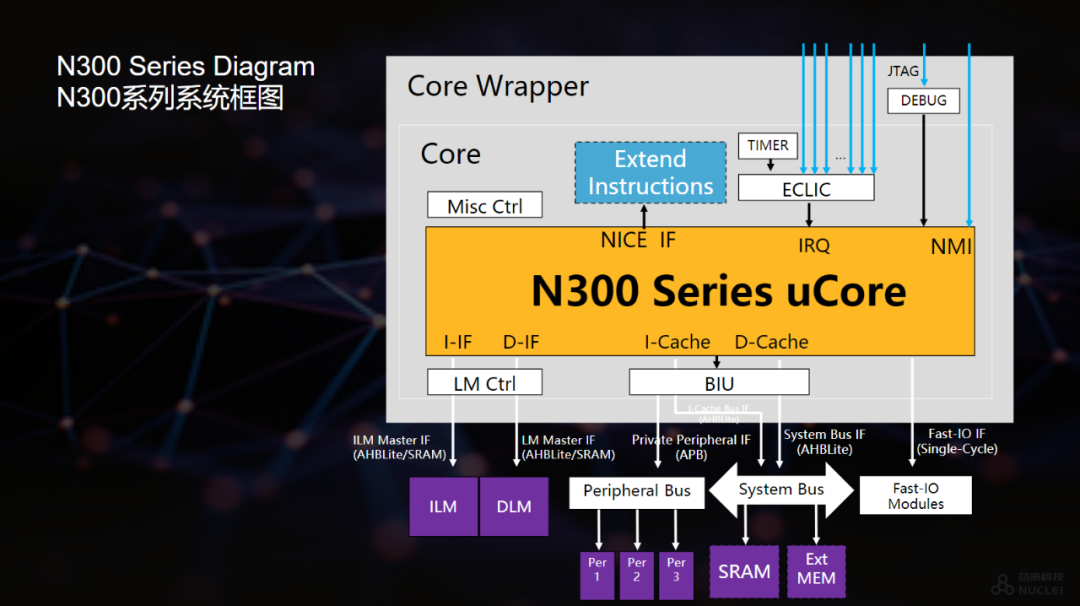

本次OpenHarmony LiteOS-M内核支持针对芯来科技N级别内核RV32架构,并采用N307FD内核作为使用示例。

N300系列32位超低功耗RISC-V处理器面向机制能效比且需要DSP,FPU特性的场景而设计,非常适合对标ARM Cortex-M3/M4/M4F/M33内核,应用于IoT和工业控制等场景。

芯来LiteOS-M内核使用

芯来LiteOS-M内核仓库链接如下:https://gitee.com/riscv-mcu/kernel_liteos_m/tree/dev_nuclei/

仓库内整体文件结构直观明了,在各开发板对应的target文件夹中较为详细的列出各文件/文件夹的作用,便于理解和使用。

芯来科技本次支持的所有工程均采用makefile编译管理,芯来科技GCC工具链编译,资源集中,所有需要的内容均可在芯来官网找到。

这里以RV-STAR开发板为例,介绍仓库的使用方法:

下载工具链并配置驱动

打开芯来科技文档与工具页面,按照以下步骤下载工具链:

CentOS或Ubuntu系统请点击图中红框1下载RISC-V GNU工具链;

点击图中蓝框2-1下载64bit的OpenOCD;

确保make工具版本不低于3.82;

Ubuntu系统使用以下指令安装make工具

sudo apt-getinstall make

CentOS系统使用以下指令安装

sudo yum installmake

新建Nuclei文件夹并在此文件夹中新建gcc文件夹和openocd文件夹;

解压缩之前下载的GNU工具链到任意文件夹中,复制其中bin文件件所在层级的所有内容到gcc文件夹中;

同样解压缩之前下载的OpenOCD到任意文件夹中,复制其中bin文件件所在层级的所有内容到openocd文件夹中。

工具链下载完成后,需要配置驱动,步骤如下:

连接开发板到Linux中,确保USB被Linux识别出来;

在控制台中使用lsusb指令查看信息,参考的打印信息如下:

Bus001Device010: ID0403:6010FutureTechnologyDevicesInternational, LtdFT2232xxxx

将github

https://github.com/riscv-mcu/ses_nuclei_sdk_projects/blob/master/misc/99-openocd.rules

上misc文件夹内99-openocd.rules文件复制到当前路径下,控制台中输入以下指令复制文件到指定路径下;

sudo cp99-openocd.rules /etc/udev/rules.d/99-openocd.rules

断开调试器再重新连接到Linux系统中;

使用ls /dev/ttyUSB*命令查看ttyUSB信息,参考输出如下:

/dev/ttyUSB0 /dev/ttyUSB1

使用ls -l /dev/ttyUSB1命令查看分组信息,参考输出如下。可以看到ttyUSB1已经加入plugdev组,接下来我们要将自己添加到plugdev组。使用whoami命令查看当前用户名,我们将其记录为< your_user_name >;

crw-rw-r--1 rootplugdev188, 1 Nov28 12:53/dev/ttyUSB1

使用sudo usermod -a -G plugdev

再次确认当前用户名已属于plugdev组,使用groups命令,可以看到打印信息中有plugdev即成功将当前用户添加至plugdev组。

编译源码

请在当前控制台中配置NUCLEI_TOOL_ROOT路径,假设Nuclei文件夹所在路径为/home/Nuclei,输入:

exportNUCLEI_TOOL_ROOT=/home/Nuclei

或者使用时make选项增加:

NUCLEI_TOOL_ROOT=/home/Nuclei

复制仓库代码到本地。在命令行中输入:

git clone https://gitee.com/riscv-mcu/kernel_liteos_m.git

复制代码到本地;

打开至代码根目录下

/target/riscv_nuclei_gd32vf103_soc_gcc/GCC

输入:makeall

开始编译,编译结束后部分参考输出如下:

text data bss dec hex filename 243301121676841210a0fa build/Nuclei-rvstar-gd32vf103-soc.elf

若编译前想清理工程,请使用:

makeclean

下载调试、运行

调试或运行前请先连接RV-STAR开发板,确保已按照环境配置中驱动配置部分配置完成。

同样配置好NUCLEI_TOOL_ROOT路径,并打开至代码根目录下的:

/target/riscv_nuclei_gd32vf103_soc_gcc/GCC

输入:

makedebug

进入GDB调试;

等待到进入GDB调试界面时,输入:

load

下载编译好的elf文件,就可以开始调试;

若想直接运行,请同样在调试时所在位置输入:

makeupload

运行时可以查看串口打印内容,使用串口查看工具,这里以minicom为例,若未安装此工具可自行安装或使用其他串口查看工具。打开控制台,输入:

minicom-D /dev/ttyUSB1 -b 115200

打开串口查看工具。

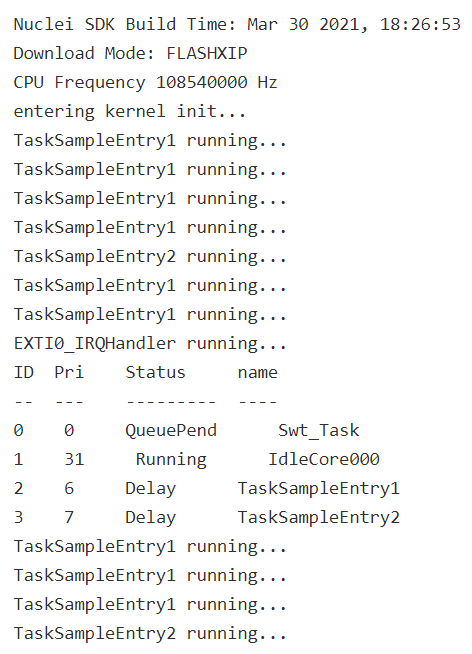

运行时参考输出如下:

总结

本次芯来RISC-V内核支持LiteOS-M内核完成了基于ECLIC的OpenHarmony LiteOS-M内核任务调度移植适配工作,以及芯来内核timer移植适配工作。编译上采用make编译管理系统,各参数区分配置,简单易懂。完全适配芯来GCC编译器,资源集中,便于查找。使用上简单易懂,仅两条指令可完成编译运行。针对不同的开发板创建了不同的工程,可直接运行使用。在根目录下target文件夹内,各开发板对应的工程文件夹配有较为详细的使用说明,可参考说明搭建编译运行环境。

编辑:jq

-

dsp

+关注

关注

553文章

7987浏览量

348745 -

芯片

+关注

关注

455文章

50714浏览量

423142 -

鸿蒙系统

+关注

关注

183文章

2634浏览量

66306

原文标题:芯来科技RISC-V处理器支持鸿蒙LiteOS-M内核

文章出处:【微信号:nucleisys,微信公众号:芯来科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Rivos全新产品采用Andes晶心科技NX45 RISC-V处理器

《RISC-V能否复制Linux 的成功?》

RISC-V内核的32位通用微控制器 GD32VF103芯片简介

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,赋能RISC-V高效落地

RT-Thread Safety AUTO成功适配芯来RISC-V车规内核

请问ESP32s3 ULP RISC-V协处理器是否支持ADC的读取?

算能全系列RISC-V处理器进入PLCT实验室6.6内核维护工程

国产RISC-V MCU推荐

经纬恒润INTEWORK-EAS产品成功适配芯来RISC-V处理器NA内核

经纬恒润AUTOSAR产品成功适配芯来RISC-V车规内核

芯来科技正式发布基于RISC-V处理器的HSM子系统解决方案

芯来科技发布超低功耗嵌入式RISC-V处理器CPU IP—NS100系列内核

芯来科技正式发布首款专用处理器产品线Nuclei Intelligence系列

芯来科技RISC-V处理器将支持鸿蒙LiteOS-M内核

芯来科技RISC-V处理器将支持鸿蒙LiteOS-M内核

评论