一、主要概念

同步逻辑和异步逻辑:时钟域为由单个时钟或具有固定相位关系的时钟驱动的设计部分。也就是说,在一个模块中一个时钟和他的翻转或者分频时钟认为是相同的时钟域,其所驱动的逻辑是同步逻辑。在一个模块中不具有相同相位和时间关系的时钟被视为不同的时钟域,其所驱动的逻辑是异步逻辑。

亚稳态:如果数据传输中不满足触发器的建立时间和保持时间,或者复位过程中复位信号的释放相对于有效时钟沿的恢复时间(recovery time)不满足,就可能产生亚稳态。亚稳态就是无法避免的,亚稳态主要发生在异步信号检测、跨时钟域信号传输以及复位电路等常用设计中。

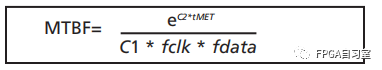

MTBF: 平均无故障工作时间,英文全称:Mean time between failures;利用平均故障间隔时间(MTBF)公式可以预测亚稳态的发生,MTBF越大则说明亚稳态对电路产生的影响越小,反之亦然。

其中C1和C2是常数,依赖于构建触发器所使用的技术;tMET为在不引起同步失败的前提下亚稳态输出持续时间,时间越长MTBF指数级增大,所以高频电路两级触发器不够可能要用三级触发器来保证;fclk和fdata分别是同步时钟和数据翻转率;所以在不影响功能前提下,可以降频工作频率和数据的翻转频率,都可以有效的增大MTBF。

二、CDC典型错误场景

在芯片设计过程中,CDC正向确认时经常会发现几种典型的错误场景:没有处理直接裸跨、输入同步器前组合逻辑输出以及多路扇出和重新聚合场景等,还有一些不太常见情况未列出,请参阅文末资料。

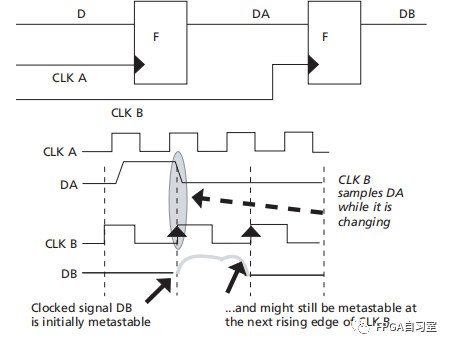

2.1直接裸跨

如上图,如果CLK B采样DA,而DA是变化的(在CLK的上升边缘和下降D)的边缘,则DB将是亚稳态的,这种就是没有使用同步器,显然是不合理的。

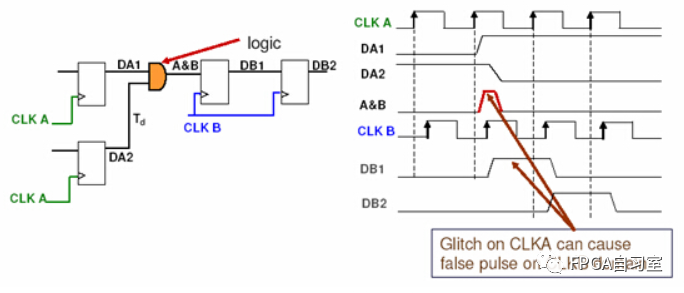

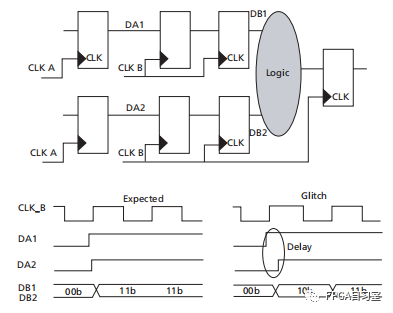

2.2毛刺(Glitch)

异步路径时序工具不会进行时序分析,这条道路上的任何逻辑都必须谨慎精心设计并验证,因为逻辑可能导致故障并在下游产生功能错误。如下图所示,尽管两个源触发器同时给出脉冲,但由于布局布线以及环境原因而引起的传播延迟(Td)不同,导致DA1和DA2信号不能同时到达,因此在CLKA时钟域下A&B会产生毛刺,而在CLKB时钟域下产生一个假脉冲,导致后继电路异常。正确的做法是将A&B在CLKA时钟域下打一拍寄存器输出。

此外,还有另外一种情况出现漏采,如下图所示,DB1在CLKB时钟域下应有的高电平信号,由于DA1和DA2的传输延时不同,导致在CLKB下没有传递出去。

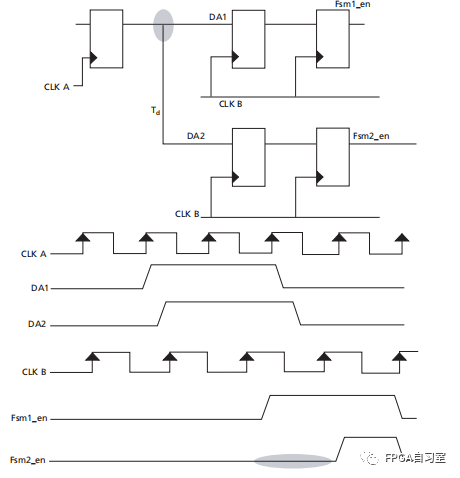

2.3多路扇出

单个信号扇出输入到多个同步器时,由于输入信号到达的同步器的时间不同(传输延时Td不同),同步可能需要一拍或者两拍完成同步,此时同步后的各个信号之间可能存在错拍问题。如下图所示,DA1和DA2信号同步后分别是Fsm1_en 和 Fsm2_en信号,设计时如果仍认为它们是相同的信号,就会导致逻辑功能错误。

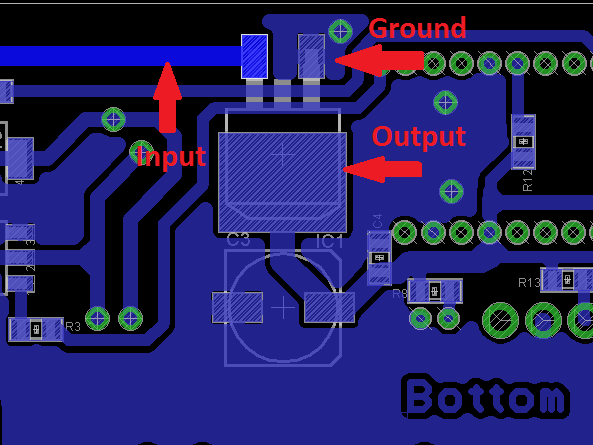

2.4重新聚合(RECONVERGENCE)

在多bit跨时钟传输过程中,如果各个bit之间分别使用单bit同步器进行跨时钟处理,在目的时钟域又重新聚合起来。如下图所示,DA1和DA2由于传输delay不同,在 CLKB上升沿采样时,就会有2’10不期望值的出现,这样DB1和DB2进行逻辑处理(聚合)时,也会得到不期望的值,这也是总线不能采用单bit同步器进行跨时钟处理的原因。此外,格雷码是可以使用单bit同步器进行处理的,AFIFO就是其典型设计。

扩展:上述指的两个两级触发器的单bit同步器,可以扩展为两个AFIFO总线跨时钟,如果设计不当,只使用其中一个AFIFO的empty作为两个AFIFO读判断,由于格雷码同步的不确定性,导致两个AFIFO的empty信号不一致,当出口两组总线聚合时,就会发生错拍问题,从而导致功能异常。解决办法是两个AFIFO的读条件应该关联或者使用一个大的AFIFO.

Referencecadencecdc(1)

Reference Spyglass cdc(2)

编辑:jq

-

CDC

+关注

关注

0文章

57浏览量

17773 -

复位电路

+关注

关注

13文章

322浏览量

44540

原文标题:CDC(四) CDC典型错误案例

文章出处:【微信号:FPGA_Study,微信公众号:FPGA自习室】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

cdc减振器控制原理是什么

关键指南针-NXP USB CDC_VCOM虚拟串口例程

USB复合设备MSC+CDC,MSC异常影响CDC收发怎么解决?

请问如何安装Espressif CDC Device驱动?

esp32-s2-usb-host-cdc示例程序接收错误怎么处理?

ESP32-S2-WROOM使用USB CDC虚拟串口打印log,模组在跑一段时间后会报一下错误,为什么?

ESP32S2使用单根USB线创建MSC+CDC与上位机通信,CDC异常的原因?

STM32 USB CDC为什么只能发送4096个字节?

STM32做3个CDC复合设备遇到的地址问题怎么解决?

USB CDC无法使用中断传输的原因?

USB复合设备MSC+CDC,CDC_Transmit_FS函数发送不正常的原因?

求助,关于USB复合设备HID+CDC串口问题求解

PCB设计工作中常见的错误有哪些?

简述CDC当中最典型错误案例

简述CDC当中最典型错误案例

评论