典型的相控阵CWD(连续波多普勒)架构中,超声传感器的聚焦孔径分成两部分,一半的(64至128个)传感器单元用于发送器,另一半用于接收器。作用在发射单元的信号是方波信号,典型频率为2.0MHz至7.5MHz多普勒频率。发射单元通过发送适当相位的信号聚焦发射波束。同样,CWD接收信号通过对每个接收单元的信号进行相位调整、求和进行聚焦。

“波束成型”CWD接收信号是由固态组织反射的强信号(通常称其为杂波)以及流动的血液反射回来的较弱的多普勒信号。每个相控阵接收通道输入端的典型杂波可能高达100mVp-p,而接收机RTI的噪底只有1至2nV/。为了优化接收性能,需要每通道的SNR达到155dBc/。

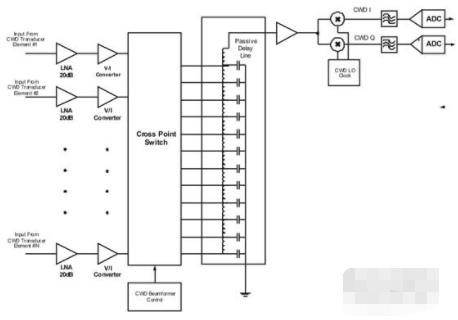

对于一个64通道的CWD接收机,考虑到求和增益,求和后的“波束成型”信号需要额外的18dB动态范围,整体信噪比SNR的要求会达到173dBc/!更加困难的是,感兴趣的低速多普勒信号的频率会在1kHz以内或低于杂波信号。由此可见超声检测设备面临巨大的设计挑战。目前,超声系统大多采用模拟延时线接收器实现CWD信号检测(图1),来自超声接收单元的输入信号经过缓冲、放大,低噪声放大器提供大约20dB的增益。LNA输出被转换成电流信号,随后通过交叉开关和模拟延时线进行波束成型。这种架构很容易集成,因为他所需要的电压-电流转换器、模拟开关、无源延时线以及单路I/Q混频器很容易集成。通过配置交叉开关求和,通过适当的延时线抽头切换信号,达到每个接收器的延时要求。

波束成型后的RFCWD信号混频后得到基带I、Q信号,这两路信号经过带通滤波后进行数字转换。RF至基带的混频处理通常是接收链路保证SNR的瓶颈,这个处理过程对CWD的性能影响较大,对于64通道设计示例,I、Q RF混频器需要在处理波束成型信号时具有173dBc/(1kHz频偏)的动态范围。能够达到这一指标的混频器很难实现,此外,本振驱动信号还必须保持极低的抖动。遗憾的是很难从市场上获得能够达到这样指标的逻辑器件—虽然CWD延时线能够满足结构紧凑的超声系统的最低要求,因此,上述性能的局限性是亟待解决的问题。

图1 基于CWD延时线的接收机简化电路

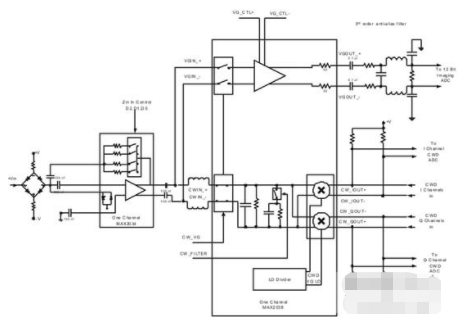

为了获得更高性能,在CWD系统中引入一个CWD混频器/波束成型器,简化框图如图2所示。该架构中,每个通道都具有一个I/Q混频器,在基带端(而非RF端)进行波束成型求和;每路I/Q混频器的LO相位可以调节在N (N =8至16相)个相位中的一种。LO相位的变化将改变接收信号的相位,达到波束成型的目的。

由于混频器的实现基于每个通道,对每个通道混频器的要求可以降低到155dBc/Hz (1kHz频偏)。这一指标虽然苛刻,但利用双极型混频器和标准逻辑器件可以实现。混频器输出为电流,而且在基带进行无源求和,可以满足CWD波束成型的SNR要求。

图2 低功耗LNA和CWD混频器/波束成型电路能够简化CWD接收机设计,获得高性能

过去,由于缺乏适当的集成工艺,很难实现高性能的波束成型架构。但目前这一问题已经得到解决,完全集成的8通道VGA和8通道CWD I/Q混频器以及配套的可编程LO驱动器已经开始供货,图3所示给出了这类器件MAX2038接收链路的示图。采用这种架构可以使超声系统达到优异的CWD性能,不存在上述延时线CWD架构的局限性。

图3 简化后的单通道超声接收机,采用MAX2038单芯片8路I/Q混频器和MAX2034 4路LNA,有效提高系统性能

构建CWD接收器的另外一个潜在问题是LNA放大器的SNR指标,为了降低功耗、减小尺寸,许多超声设计人员选择了CMOSLNA,这样的器件可能适合某些能够控制CWD性能的应用。利用几何尺寸低于0.35μm的CMOS工艺制作放大器时,1/f噪声很大。这种噪声会引起LNA增益的低频调制。较强的RFCWD杂波通过这种LNA时将产生较大的低频调制噪声,从而降低SNR指标和CWD检测灵敏度。因此,为了满足高性能的应用需求,应选择类似于MAX2034 4通道超声LNA的双极型低噪声放大器。

责任编辑:gt

-

传感器

+关注

关注

2548文章

50656浏览量

751817 -

混频器

+关注

关注

10文章

678浏览量

45599 -

发送器

+关注

关注

1文章

258浏览量

26793

发布评论请先 登录

相关推荐

混频器的分类和介绍

混频器怎么选

结构紧凑的超声成像系统连续波多普勒(CWD)设计的挑战

RF和微波设计中混频器件应用

利用双极型混频器和标准逻辑器件满足CWD波束成型的SNR要求

利用双极型混频器和标准逻辑器件满足CWD波束成型的SNR要求

评论