摘要: 针对数字图像处理与传输领域数据量大而传统接口无法满足其高速率传输要求的现状,提出了一种基于LVDS和PCI接口的高速图像传输系统的设计,对系统总体设计和各电路模块进行了详细介绍和分析,并对系统整体功能进行了测试。该系统以FPGA作为控制核心,采用乒乓操作实现数据的无缝缓冲,重点研究了LVDS接口和PCI总线技术,保证图像数据的高速、可靠传输。测试结果表明,该传输系统性能稳定,能可靠地实现图像数据传输,最大传输速率可达18 MB/s,具有一定的实用价值。

近年来,随着电子信息、多媒体技术的快速发展,在图像处理和视频传输等领域中传输的数据量越来越大,这对数据传输的速度和质量提出了很高的要求[1]。然而,一些传统的点对点物理层接口由于在速度、可靠性、功耗、成本等方面的限制,已经无法满足高速数据传输的应用要求,因此迫切需要一种速率快、可靠性高、功耗低的数据传输方式。低压差分信号技术LVDS(Low Voltage Differential Signaling)使用极低的摆幅通过双绞电缆传输数据,是一种最高传输速率可达1.923 Gb/s的通用接口技术,并且由于其低压差分的传输方式,具有较强的抑制信号干扰能力,大大提高了数据传输的距离、速率和可靠性[2]。此外在计算机测量领域,PCI总线凭借其出色性能以及良好的兼容性,在工业控制、数据采集、信息通信、航空航天等领域得到广泛的应用[3],为图像数据高速传输提供了有力的保障。

结合LVDS接口与PCI总线能够满足高速传输的特性,本文主要从系统总体设计、硬件设计和逻辑设计等方面介绍一种基于LVDS和PCI接口的高速图像传输系统。

1 系统总体设计

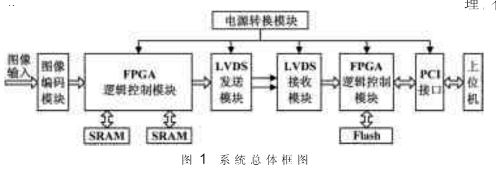

本文设计的高速图像传输系统主要实现对数字图像信息的编码、传输以及显示功能,突出传输系统的高效与可靠。系统采用模块化设计思路,各个模块之间既相互独立又相互配合,主要由电源转换模块、图像编码模块、LVDS收发模块、FPGA逻辑控制模块和PCI接口等模块组成。其中,图像编码模块的功能由软件完成,根据图像格式进行相应的二进制编码; FPGA逻辑控制模块实现系统对硬件高集成度的要求。系统总体框图如图1所示。

该系统的图像信息输入主要包括单幅图片以及视频流数据,图像编码模块首先根据内部协议规范的帧格式对图像信息进行二进制编码,之后将数据帧依次发送到FPGA逻辑控制模块中;FPGA逻辑控制模块对两片SRAM采用乒乓操作,将接收到的数据交替读/写进行缓冲,然后通过LVDS发送模块发送出去;在接收端,LVDS接收模块对接收的数据进行串/并转换,FPGA逻辑控制模块将数据写入Flash存储芯片进行备份,同时将数据通过PCI接口传输给上位机进行处理及显示。在此过程中,系统指令的下发均由上位机完成。

2 硬件设计

2.1 LVDS收发单元

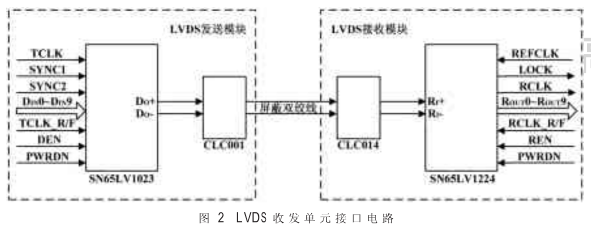

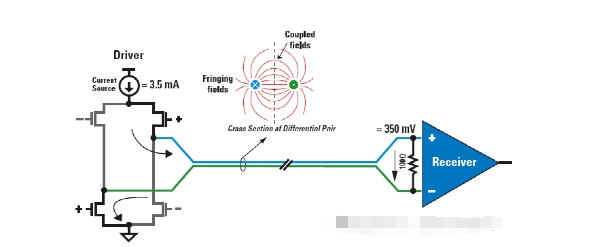

LVDS收发单元由LVDS发送模块和LVDS接收模块两部分组成。设计选用美国德州仪器公司的10位总线型低压差分信号串化器SN65LV1023A和解串器SN65LV1224A作为数字图像数据高速传输的LVDS接口芯片,接口电路如图2所示。

SN65LV1023/1224A芯片组采用主动工作模式,可输入的频率范围为10~66 MHz,芯片最高传输速率可达792 Mb/s,具有初始化、同步、数据传输、休眠、高阻5种工作状态[4]。该芯片组在正常工作之前必须经过时钟同步操作。当系统上电后,芯片组首先将输出管脚置为高阻态并启动锁相环,再由串化器发送SYNC(“000000111111”)同步信息,若解串器LOCK管脚置“0”,则说明时钟已同步,可以进行数据传输。

在数据传输过程中,串化器将接收到的10 bit电平数据进行并/串转换,然后将内嵌有时钟信息的串行数据发送到差分端口经由屏蔽双绞线输出;在接收端,解串器在REFCLK时钟下将接收到的串行数进行串/并转换并存入锁存器中,根据重建的同步时钟信号RCLK将10 bit并行数据输出,从而完成整个传输过程。设计中采用内嵌时钟恢复技术进行数据处理,有效地解决了由于时钟与数据同步不严格而引起的制约其性能的一系列问题。

由于高频信号在PCB导线和电缆上的损耗会使边沿变化速率降低,引入码间串扰,但这会导致传输信号衰减。所以为了保证数据的传输质量,设计中配合使用LVDS芯片和电缆延展器芯片。采用CLC001驱动器和CLC014均衡器实现高速传输的信号调理作用,降低了信号损耗,补偿了信号衰减,从而保证数据传输的稳定性和可靠性。

2.2 PCI接口单元

本设计采用PCI接口单元实现底层电路与上位机之间的数据传输。上位机通过PCI接口单元实现指令下发和数据上传,并完成数据处理和显示功能。PCI(Peripheral Component Interconnect)总线规范是一种高性能32/64 bit地址数据复用的高速外围设备接口标准[5]。该总线具有众多优点,当采用33 MHz时钟,32 bit数据总线最大传输速率可达132 MB/s,当扩展到64 bit数据总线后,其数据吞吐量可达264 MB/s的峰值。

如果换用66 MHz时钟,数据传输速率理论峰值高达528 MB/s[6]。考虑到PCI协议复杂性较高,如果直接使用FPGA对其进行设计难度较大,因此采用PLX公司的PCI总线通用接口芯片PCI9054作为PCI总线与本地总线的桥接芯片,其控制方便、成本低廉、通用性强。PCI接口电路如图3所示。

PCI接口单元主要由PCI9054、HT93LC56和外部晶振组成。PCI9054芯片提供PCI、LOCAL和E2PROM 3个接口,分别实现与PCI总线、本地总线和配置芯片的物理连接。本设计采用32 bit数据宽度,数据与地址不复用,故配置PCI9054工作在C模式下。测试指令的下发采用直接从模式,应用程序首先利用API将指令数据复制到主机内核空间,然后CPU通过驱动程序获得PCI总线的控制权,实现对本地总线和配置寄存器的访问;

而数据上传过程由于数据量大、速率快,所以采用DMA方式,DMA方式无需CPU的参与即可实现本地总线与PCI总线的数据交换,能够完成高速传输的任务。数据上传操作同样由应用程序发起,首先申请用户空间用于存储上传的数据,并通过API将其地址映射到内核空间地址,然后配置PCI内部的DMA寄存器,启动DMA传输。在DMA方式下,PCI9054作为PCI总线和本地总线的主控设备,将本地总线中的数据传输至内核空间,此时应用程序通过访问用户空间处理上传的数据。指令下发和数据上传过程分别如图4、图5所示。

3 系统逻辑设计

3.1 FPGA逻辑程序

设计中,FPGA采用Xilinx公司的SPARTAN系列芯片,该芯片具有很高的逻辑资源,易于配置。系统发送端的FPGA逻辑控制模块主要完成高速数据的接收缓存以及LVDS接口的时序控制。为了提高传输速度,避免数据流不连续,系统采用“乒乓操作”,交替对两片SRAM进行读/写。当FPGA接收到数据时,首先对SRAM 1进行写操作,接着将下一帧图像写入SRAM 2;

同时对SRAM 1进行读操作,并将读出的数据转发到LVDS发送模块。系统在对一片SRAM进行写操作的同时,可以对另一片SRAM进行读操作,如此交替读/写有效地节省了等待时间,从而提高了数据的传输速度,实现数据的无缝缓冲与处理。“乒乓操作”控制时序流程如图6所示。

3.2 固件配置

PCI9054内部寄存器的初始化配置由Microchip公司的E2PROM HT93LC56完成,主要包括PCI和Local配置寄存器、DMA寄存器、Runtime寄存器等寄存器组[7]。本设计采用从方式和DMA两种数据传输方式,配置LAS0BA(0)=1、LAS0RR(0)=0、LBRD0(1:0)=11,将地址空间0作为指令下发的本地空间并设置数据宽度为32 bit;对DMA寄存器的配置包括:DMAMODE0(1:0)=11表示数据宽度为32 bit,DMAMODE0(8:7)=00表示传输采用单周期方式等。这些配置信息均可借助PLX公司提供的PLXMon工具进行烧写。

4 测试结果

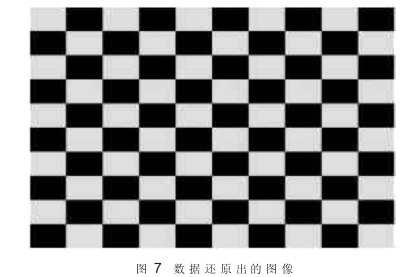

为了验证本系统图像数据处理与高速传输的可靠性,对其整体进行了功能测试。图像信息源采用大小为720×480的黑灰规律变化的图像,将二进制数据还原成图片之后通过肉眼观察并进行软件分析来判断是否发生错误。

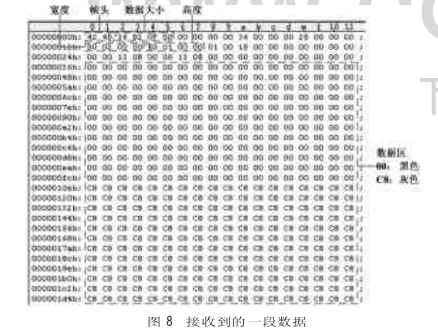

图7是接收到的一帧数据还原出的图像,图像清晰明了,没有明显的异常现象。图8是测试系统功能时计算机记录的一段数据,虚框内的“42 4D”为帧头,“36 D2 0F 00”为一帧图像的数据大小,“D0 02 00 00”和“E0 01 00 00”分别表示图像的宽度与高度,随后是图像数据区域(“00”代表黑色,“C8”代表灰色)。经过软件对比分析,接收到的数据准确无误码,所以该系统可以实现设计功能并具有较高的稳定性。

本文充分利用了LVDS技术的传输特点与应用优势,结合“乒乓”读写操作和PCI总线传输技术设计了一种基于LVDS和PCI接口的高速图像传输系统,并通过实验验证了该系统的可靠性和准确性。该系统可以应用到工业数据采集、测试等领域,具有较高的可靠性。

参考文献

[1] 陈伟,宋燕星。基于LVDS技术的高速数图像传输系统[J]。电子测量技术,2008,31(11):172-174.

[2] 彭乡琳.LVDS在长距离信号传输中的应用[J]。兵工自动化,2006,25(7):60-61.

[3] 邓凤军,张龙,王益忠。基于PCI总线的HDLC通信卡的设计与实现[J]。电子技术应用,2012,38(8):30-36.

[4] Texas Instruments.SN65LV1023A/SN65LV1224A 10-MHz to 66-MHz,10:1 LVDS serializer/deserializer[Z].2003.

[5] 安冬冬,刘文怡,郅银周。基于PCI9054从模式的数据采集卡设计与应用[J]。计算机测量与控制,2010,18(10):2439-2440.

[6] 叶勇,沈三民,郭铮,等。基于PCI总线的高速串口通信卡的设计[J]。电视技术,2013,37(3):82-85.

[7] PLX Technology.PCI 9054 data book version 2.1[Z].2000.

编辑:jq

-

芯片

+关注

关注

455文章

50791浏览量

423482 -

PCI

+关注

关注

4文章

666浏览量

130265 -

lvds接口

+关注

关注

1文章

128浏览量

17407

发布评论请先 登录

相关推荐

lvds接口在工业显示中的应用

lvds接口适用于哪些设备 lvds接口兼容性问题解析

lvds接口传输距离限制 lvds接口优势及劣势分析

lvds接口和HDMI的区别 lvds接口电路设计技巧

lvds接口用途与应用 lvds接口连接方法指南

PCIe接口的工作原理 PCIe与PCI的区别

高速ADC与FPGA的LVDS数据接口中避免时序误差的设计考虑

浅谈LVDS和PCI接口的高速图像传输系统设计

浅谈LVDS和PCI接口的高速图像传输系统设计

评论