引言

近年来,实时信号处理的要求越来越高,所用系统要求具有处理大量数据的能力,这就要求系统硬件要达到很高的运算速度,并且软件处理程序也要尽可能优化,以保证系统的实时性。本文基于FPGA和ADSP-TS101S所实现的一种高速数据并行处理系统,可以进行实时连续波和脉冲波的处理,并将连续波的频谱和脉冲波脉冲幅度信息、脉前时刻、脉宽及载频打包输出。整个系统的输出延时被控制在1ms之内。

系统任务及系统结构

系统任务

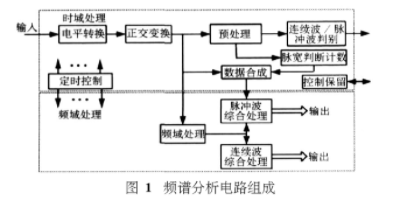

系统频谱分析电路组成结构如图1所示。

前端输入为高频宽带模拟信号经过数字化采样后得到的数字信号。系统主要完成的任务是对该数字信号进行实时处理,并识别出高频宽带模拟信号为连续波还是脉冲波。如为连续波,系统计算出它的频率,并输出其频谱;如为脉冲波,系统计算出它的脉冲宽度和脉载频,并把载频与时域中的脉冲前沿时刻信息、宽度信息及幅度信息对应起来,传送给后面的系统进行处理。

系统先对输入的数字信号进行电平转换,然后进行正交变换。接下来开始对信号进行频域处理,并以1.92μs为最小时段输出其频谱,同时进行预处理和连续波/脉冲波判别。对连续波,将各小时段的信号频谱进行综合处理后输出其频谱。对脉冲波,确定其脉冲前延时刻和脉冲后延时刻,从而确定其脉冲宽度,接着将脉冲幅度、后延时刻及宽度进行数据合成,之后再结合各个小时段的频谱进行综合处理,最终将脉冲幅度信息、脉冲前延时刻、宽度及载频打包输出。

系统结构

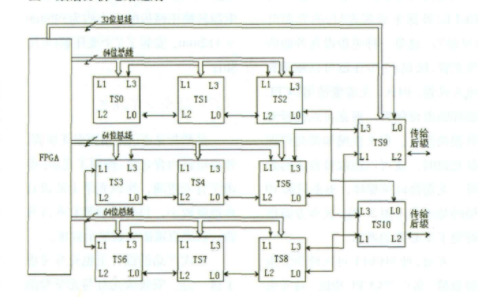

该信号并行处理系统结构框图如图2所示。

该系统主要由1片FPGA和11片TS101系列的DSP构成。FPGA首先将16位高速ADC采集进来的数据预处理后拼接成64位,使数据总线上的数据传输速率降低为输入速率的1/4,然后通过数据总线依次送给TS0~TS8,同时产生TS0~TS9的控制信号DMAR和IRQ来控制每片DSP读取数据总线上的数据。

由图2可以看出,TS0、TS1、TS2(第1组)和TS3、FS4、TS5(第2组)以及TS6、TS7、TS8(第3组)在结构上为完全相同的三部分,且所进行的工作也完全相同,都需将处理完的数据通过链路口送给TS9和TS10。接着由TS9和TS10进行综合比较,最后再通过链路口将处理结果送给后级板,并将结果分为3组,可进行相同的处理。每片TS101S只有4个链路口,因此TS9和TS10只能提供3个链路口给TS0~FS8,TS0的数据通过TS2的链路口中转给TS9和TS10,TS1的数据也通过TS2的链路口中转给TS9和TS10,其它两组与第1组处理方法相同。

在1.92μs内,TS0~TS8将接收到的一帧64×64位数据拆分扩展成256×32位浮点数,然后对数据进行32位浮点FFT(快速傅立叶变换)运算,接着求模平滑,将得到的频域数据发送给TS9和TS10进行综合处理。TS9负责完成脉冲波综合处理任务,TS10负责完成连续波综合处理任务。最后,TS9和TS10将数据通过链路口送往后级进行处理。

信号处理软件实现

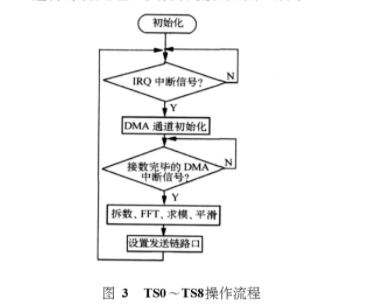

在整个并行分析系统中,TS0~TS8需要各片DSP在时序上达到高度统一,每片DSP都应尽量简化流程,节约时间开销。TS0~TS8的主要任务是将接收到的数据进行FFT运算,并最终将各个小段信号的频谱发送到TS9和TS10进行综合处理。其操作流程如图3。

这里,DSP首先进行初始化设置,设置完毕进入等待,直到接收到FPGA发出的信号,DSP跳出等待,进入IRQ中断服务子程序。在IRQ中断服务子程序中,进行DMA通道初始化,准备从总线上接数,设置完毕DSP前台进入等待。DSP后台接数操作每接到一个FPGA发出的信号,就完成接一个数。当接满64个64位数时,发出DMA中断,并使DSP跳出等待,进入DMA中断服务子程序。在DMA中断服务子程序中,进行拆数、FFT、求平方和、平滑等运算,待所有运算完毕,DSP开始设置链路口,将平滑后的结果,即128个32位的数传给每组的最后一片,最后一片发往TS9和TS10。

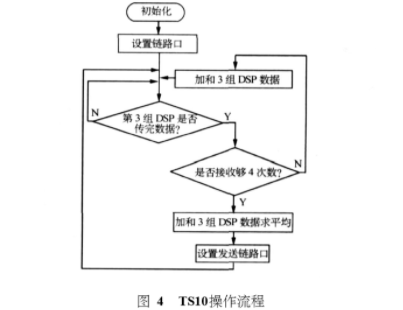

连续波信号需要在FFT变换后再做平滑处理,然后依次输出各频率点的幅度值,从而获取连续波信号的频谱信息。具体而言,就是TS0~TS8分成3组,每组3片;每组DSP中,前两片的链路口分别与第3片的链路口相连,然后通过第3片的链路口将其运算结果传送到TS10中;以17.28μs×4=69.12μs为一帧,9片DSP分时并行完成2.56点FFT运算和求模运算,TS10将这9片DSP的运算结果在一帧内进行平滑,完成一帧内信号的频谱分析,同时将该帧的谱信息打包处理,最后通过TS10的第4个链路口将包数据发送到后级处理器。图4为TS10的处理流程图。

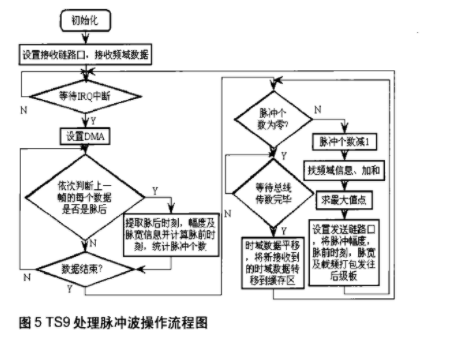

对于脉冲波综合处理,其操作流程如图5所示。

脉冲波综合处理要同时输出该段时间内的时域脉冲幅度信息、脉冲起始时间、宽度及载频信息。上述参数中,时域脉冲幅度信息、脉冲起始时间和脉冲宽度已经通过相应的DMA中断送到TS9,TS9通过32位总线中的高24位接收数据,次高位用于设置脉后标志(即当次高位为1时脉冲结束,低22位即为脉后时刻),脉后时刻前的数据为脉冲幅度信息,脉后时刻后的数据信息表示了脉冲宽度,由此可得到脉冲起始时刻)。

另外,对于载频信息,TS0~TS8将FFT结果送到TS9之中,TS9连续循环存储多帧频域数据,由于前9片DSP所得到的信息是按照严格的帧定时运算所得的,所以需要将它们的信息做相应的融合合并才能打包输出。具体融合原则为:

a.当在接收到的时域数据中搜索到脉冲结束标志时,计算出该脉冲的脉前信息,并存储脉前信息、时域脉冲幅度信息、脉冲起始时间及脉冲宽度;

b.在TS0~TS8送来的谱信息中搜索,与存储的时域脉冲波信息相结合确定脉冲波,且将数个小段数据(1.92μs)内的几个(最多只加5个)谱信息组合合并,得到相对完整准确的脉冲载频;

c.向后级发送数据时发送脉冲前沿时刻、时域幅度信息、脉宽及载频等信息。

结语

本文中的高速实时信号并行处理系统已通过测试,系统能够完成连续波和脉冲波的处理,对连续波计算出它的频率并输出其频谱,对脉冲波计算出它的脉冲宽度和脉冲载频,并把脉冲载频与时域中的脉冲前沿时刻信息,脉冲宽度信息及脉冲幅度信息很好地对应起来打包输出。各个DSP算法程序均已完成,并已通过测试。整个DSP中程序均使用汇编程序编写,最大地简化了运算流程,节约了时间开销。

编辑:jq

-

脉冲

+关注

关注

20文章

899浏览量

96240 -

电平转换

+关注

关注

3文章

148浏览量

34033 -

连续波

+关注

关注

0文章

10浏览量

10349

发布评论请先 登录

相关推荐

芯有灵犀智创未来,基于中科亿海微FPGA实现图像处理系统及应用——第九届集创赛中科亿海微杯赛题解析

EE-174:ADSP-TS101S TigerSHARC处理器引导加载程序内核操作

EE-218:为ADSP-TS201 TigerSHARC处理器编写高效浮点FFT

EE-217:更新ADSP-TS101S TigerSHARC EZ-KIT Lite固件

EE-176:ADSP-TS101S TigerSHARC处理器硬件设计核对表

EE-205:将代码从ADSP-TS101S TigerSHARC处理器移植到ADSP-TS201S TigerSHARC处理器的注意事项

EE-182:ADSP-TS201S TigerSHARC处理器散热设计

EE-157:ADSP-TS101上的分支目标缓冲器说明

EE-178:ADSP-TS101S TigerSHARC片上SDRAM控制器

EE-170:估算ADSP-TS201S TigerSHARC处理器的功耗

AN-813: ADSP-BF533/ADSP-BF561 Blackfin处理器与高速并行ADC接口

基于FPGA和ADSP-TS101S所实现的一种高速数据并行处理系统

基于FPGA和ADSP-TS101S所实现的一种高速数据并行处理系统

评论