DQ0-7 八根线必须连到同一T块(也称为字节组)上,一旦分在一起,这个字节组就不能放地址线和控制线了,只能放数据线。

每组数据线对应的DQS必须连到N6,N7上,也就是QBC或者是DBC上

字节组的N1和N12不能使用作为数据线,并且如果这个字节组放了其他数据线,则N1,N12相当于废掉,地址线和控制线也不能放。

DM信号必须位于与其相对应的DQ所在的字节组的N0引脚上

当然如果禁用DM,N0可以用于其他DQ,但是不能给地址线和控制线,

如果禁用DM,必须将其在PCB上拉低,

x4作为半个字节,必须成对使用,比如半个字节,一个字节,两个字节,四个字节 分别对应DQ0-3 DQ0-7 DQ0-15 DQ0-31

如果是用四片DDR,必然会用到3个bank,三个bank必须连续,地址线控制线bank必须位于中间bank,

地址线和控制线必须位于同一bank中,并且,可以位于那一个字节通道的13个引脚的任何一个。

对于RDIMM和UDIMM的双插槽配置,cs,odt,cke和ck端口宽度加倍。

ck对必须位于地址/控制字节通道中的任何PN对上

RESET_N可以位于任何引脚,且IO标准为SSTL15 复位的时候应该是拉低,加电期间保持高电平。加个4.7K下拉电阻,

DDR使用的IObank必须在同一列中,64 65 66这样

支持接口最大是80位宽,五个DDR同时存在 对DIMM无效

不允许跳着bank使用DDR,比如使用64 66bank

并且有一个晶振输出放在地址线控制线bank的GCIO引脚上,而且必须是差分时钟。

在UG571中指出,如果某一bank用于连接存储芯片,要将其VREF引脚连接1k电阻再到GND

如果字节组被设置用于存储IO那么不能将系统复位分配给字节N0和N6

给DDR ip核的时钟输入必须是差分时钟。

以上均属于个人拙见,不保证正确,仅供参考。

原文标题:总结了20个DDR3和FPGA部分的设计规范

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

FPGA

+关注

关注

1628文章

21722浏览量

602893 -

DDR

+关注

关注

11文章

712浏览量

65316

原文标题:总结了20个DDR3和FPGA部分的设计规范

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

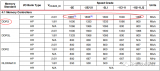

DDR3、DDR4、DDR5的性能对比

如何选择DDR内存条 DDR3与DDR4内存区别

基于FPGA的DDR3多端口读写存储管理设计

三星和SK海力士下半年停产DDR3内存

华邦倾力挺进DDR3市场,抓住转单商机

全套DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 电源解决方案同步降压控制器数据表

完整DDR,DDR2,DDR3 和LPDDR3 存储器电源解决方案同步降压控制器数据表

具有同步降压控制器、2A LDO和缓冲基准的完整DDR2、DDR3和DDR3L存储器电源解决方案TPS51216-EP数据表

完整的DDR2、DDR3和DDR3L内存电源解决方案同步降压控制器TPS51216数据表

适用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF缓冲基准的TPS51206 2A峰值灌电流/拉电流DDR终端稳压器数据表

具有同步降压控制器、2A LDO和缓冲基准的TPS51916完整DDR2、DDR3、DDR3L和DDR4存储器电源解决方案数据表

具有同步降压控制器、2A LDO和缓冲基准的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4内存电源解决方案数据表

完整的DDR、DDR2和DDR3内存电源解决方案同步降压控制器数据表

关于DDR3和FPGA部分的20个设计规范总结

关于DDR3和FPGA部分的20个设计规范总结

评论