在FPGA视频图像处理系统中,经常需要使用到SDRAM作为视频图像缓存。SDRAM控制器可以分为上电初始化,自动刷新,读操作和写操作这四个部分,他们之间的转换可以通过状态机来控制。下面分别实现这几个部分。

1.SDRAM上电初始化

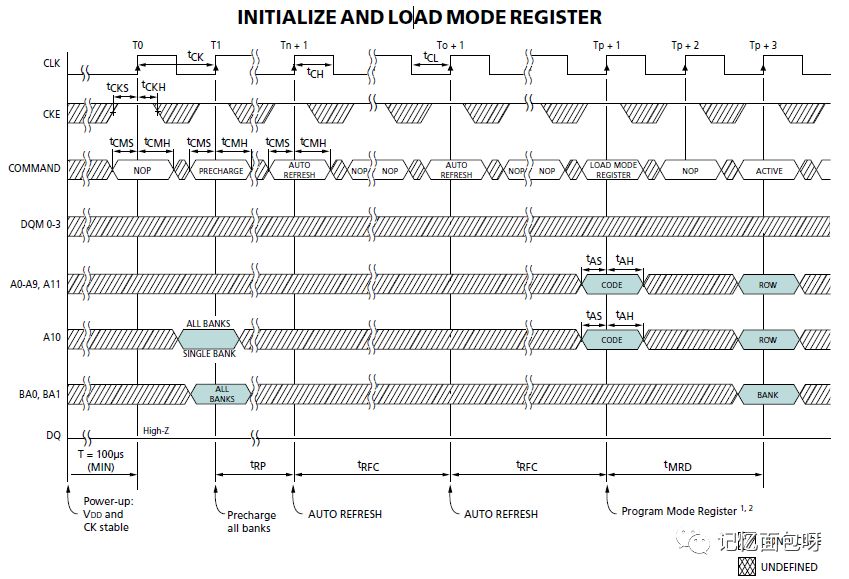

SDRAM上电初始化时序如下图所示。

由时序图可知初始化大概的过程为:上电后等待电源VDD和时钟信号稳定100μs(期间命令为空命令),同时在100μs内设置CKE(时钟使能)信号为高。随后对所有Bank发送预充电(PRECH ARGE)命令,发送两次自动刷新(REFRESH)命令,最后发送装载模式寄存器(LOAD MODE REGISTER)命令,并将设置寄存器的值传入地址总线A0~A11。

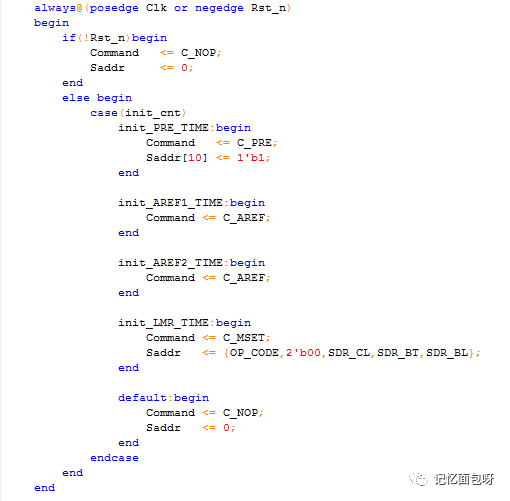

上述过程的实现可以通过线性序列机来实现。即需要对初始化过程时间进行计数,当时间到达时就执行某个命令。下面是部分代码。

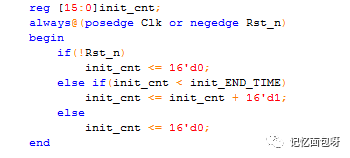

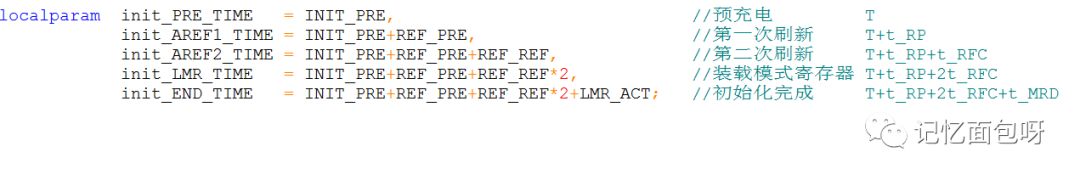

1.计时器

2.命令执行时间设置

3.对应时间执行对应命令

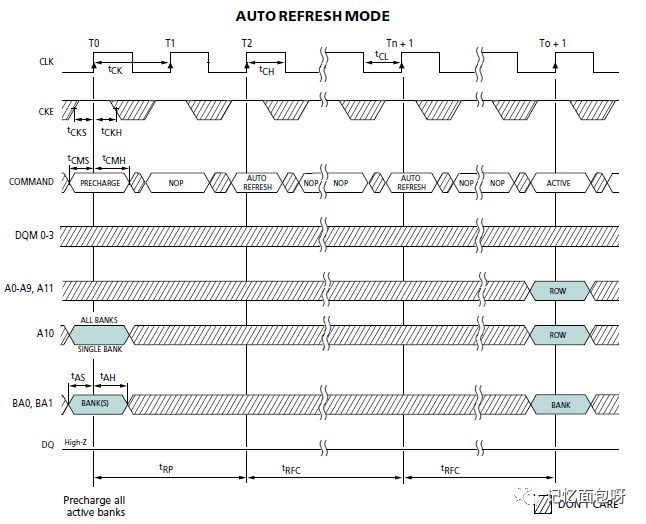

2.SDRAM自动刷新

同样给出自动刷新的时序图。

过程比较简单:首先对所有Bank预充电,然后发送两次自动刷新命令。

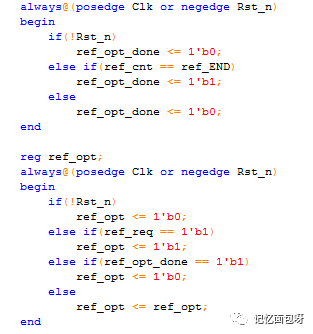

同样可以使用线性序列机的方法来实现,这里就不重复了。但需要添加一个刷新状态标志。ref_opt_done=1表示刷新完成,ref_opt=1表示正在刷新。

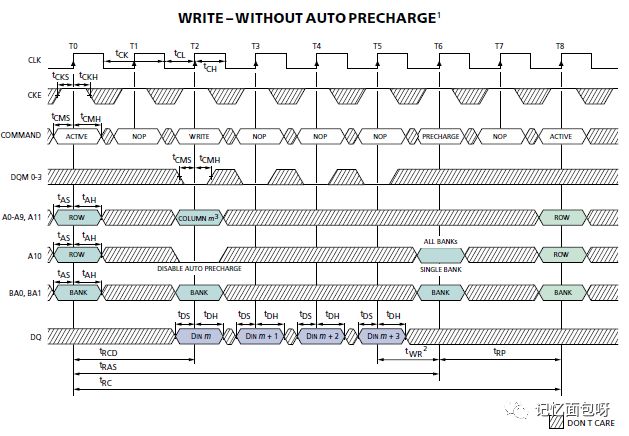

3.SDRAM写操作

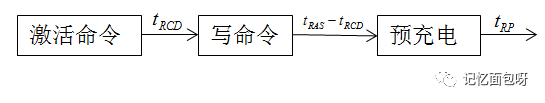

从时序图上看首先发出激活命令,并给出行地址Bank地址;随后发出写命令,并指定写入Bank,起始列地址和写入数据;最后进行预充电,关闭所有Bank。这里每次突发写入4个数据,即突发长度为4,突发长度可以在之前初始化的模式寄存器中设置。

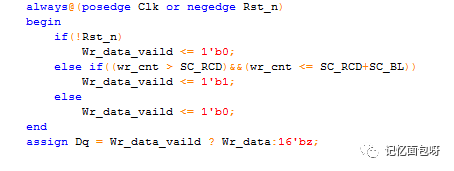

同样使用序列机的实现方法,在写操作中也需要添加写操作完成状态标志,和过程状态标志。此外只有当写入突发长度数据的时候我们才使能数据线输入有效,其他时刻让数据线保持高阻态,所以要添加一个写数据状态标志Wr_data_valid=1时表示正在写数据。

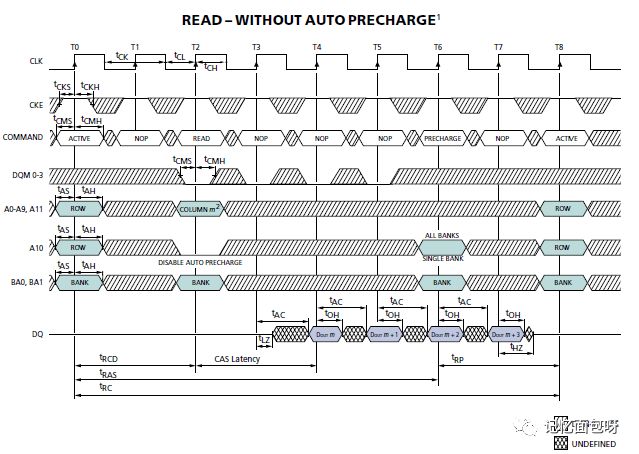

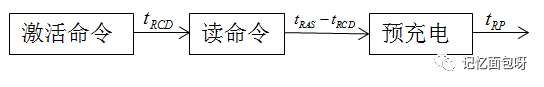

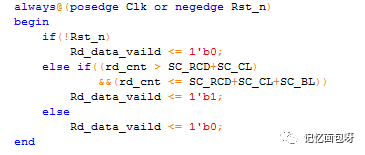

4.SDRAM读操作

与写操作类似,但是我们输入读命令的时候,数据并不是立刻输出,而是要经过一个CAS_Latency后输出。这个延时也可以通过模式寄存器的配置来调整。我们同样需要给出读操作完成、读操作过程,读出突发数据的有效区间。

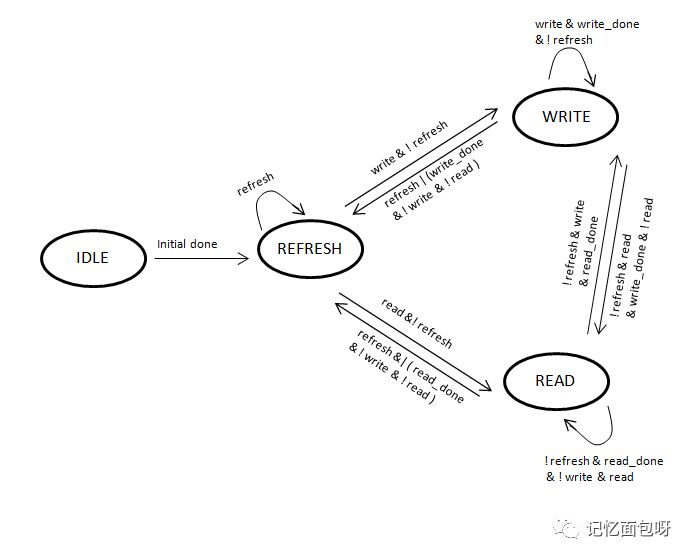

5.SDRAM控制器设计

首先SDRAM上电后进入空闲状态,初始化完成后进入刷新状态,然后根据输入命令进行转换,实际上状态机的控制对于刷新操作,读/写操作是有一个优先级的:刷新操作》写操作》读操作。即假设写命令和刷新命令同时到来时先执行刷新操作。下图为状态机的状态转移图。具体实现可参考完整代码。

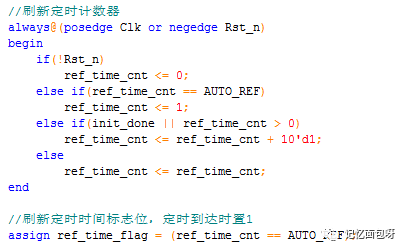

由于SDRAM需要固定时间间隔刷新一次,我们还得考虑一个刷新定时器,固定时间产生一个刷新请求。

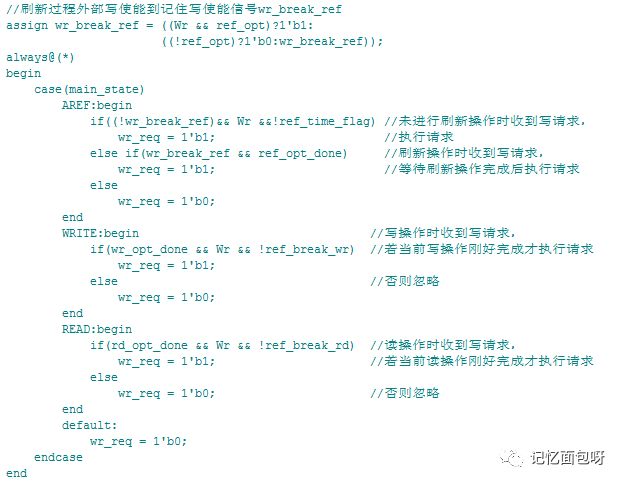

最后我们还需要考虑如果在读操作的时候,产生了刷新请求或写请求怎么办呢?写操作的时候,产生了刷新请求或读请求怎么办?或者在刷新操作时产生了读/写请求怎么办?

对于刷新请求的突然到来我们采取记住刷新标志,等待当前任务完成后进行刷新操作。

在刷新操作时读/写请求突然到来,我们也采取记住读/写标志,等待当前任务完成后进行读/写操作。

但是对于在读/写操作时外部读/写请求的到来,我们选择了忽略这次请求。部分代码如下。

由于视频信号数据读入读出都是连续不断的,因此在某些时刻会导致读写的遗漏,但一般会在SDRAM读出写入前加上一个FIFO进行缓存控制数据的读写,当写FIFO中数据大于一次突发长度时,使能写信号;当读FIFO中数据小于突发长度时,使能读信号,就可以解决这个问题。

编辑:lyn

-

FPGA

+关注

关注

1629文章

21736浏览量

603248 -

计时器

+关注

关注

1文章

420浏览量

32701 -

代码

+关注

关注

30文章

4787浏览量

68589 -

SDRAM控制器

+关注

关注

0文章

28浏览量

8138

原文标题:SDRAM控制器设计

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

DDR4 SDRAM控制器的主要特点

一文详解智能汽车域控制器基础知识

关于SDRAM控制器的基础知识详解

关于SDRAM控制器的基础知识详解

评论