集成电路设计发展到超深亚微米,其特征尺寸越来越小,并趋近于曝光系统的理论极限,光刻后硅片表面的成像将产生严重的畸变,即产生光学邻近效应(Optical Proximity Effect)。随着光刻技术面临更高要求和挑战,人们提出了浸没式光刻(Immersion Lithography),离轴照明(Off Axis Illumination),移相掩膜(Phase Shift Mask)等各种分辨率增强技术(Resolution EnhancementTechnology)来改善成像质量,增强分辨率。

双重光刻基本原理及流程

双重光刻技术(Double Patterning )作为一种有效的光刻分辨率增强技术被广泛的应用于22nm,20nm,14nm技术节点。当前主流的1.35NA的193nm浸没式光刻机能够提供36-40nm的半周期(half-pitch)分辨率,可以满足28nm逻辑技术节点的要求,如果小于该尺寸,就需要双重曝光甚至多重曝光技术。

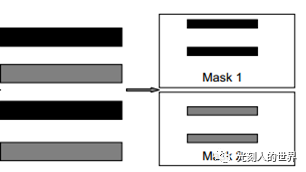

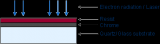

双重光刻技术主要的实现方式有两种:一种是曝光——刻蚀——曝光——刻蚀(Lithography-Etch- Lithography-Etch),LELE的基本原理就是把原来一层光刻图形拆分到两个或多个掩膜上,利用多次曝光和刻蚀来实现原来一层设计的图形。另一种是自对准双重成像技术(self-aligned double patterning),SADP的原理是一次光刻后,再在第一次光刻图形周围通过淀积侧墙,通过刻蚀实现对空间图形的倍频。

图1 LELE原理

图形拆分

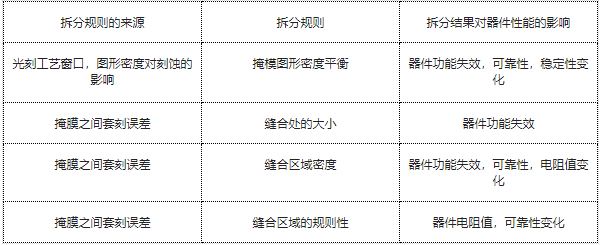

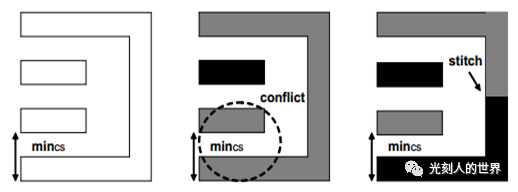

双重光刻的关键步骤需要对复杂版图进行拆分,也就是按照一定的规则将设计图形转移到两个掩膜版上。事实上,版图的拆分可以被认为是着色问题,原因在于拆分时不同掩膜上的图形用不同的颜色加以区分。在拆分过程中,拆分后的图形必须满足根据工艺条件确定的规则,不满足规则的部分称为冲突。根据版图的结构和复杂性,拆分模式可以分为两类:一种模式允许引入切割解决冲突,称为缝合(stitch);另一种模式不允许引入切割,只能自然分解或重新设计版图,称为非缝合式(non-stitch)。表1中列出了一些基本的拆分规则。

表1 拆分规则及其来源和对工艺的影响

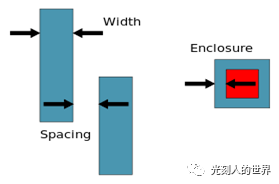

基于DRC的拆分规则会对版图提出一定的要求,最基本的拆分规则如图4所示。宽度规则指定设计中任何形状的最小宽度,间距规则指定两个相邻对象之间的最小距离。根据这些规则对版图进行分解。

图2 一些基本的图形拆分规则

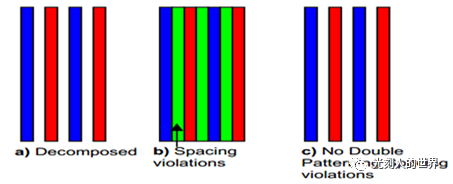

下面以一个简单的4线条版图拆分为例。首先对图形进行拆分,红/蓝表示不同的掩膜,绿色线条表示分解后可能存在的冲突。分解后对掩膜进行DRC检查,通常情况下拆分能够满足要求。

图3 一个简单的DRC拆分示例

然而对于一些复杂的图形,如DRAM及逻辑单元等的复杂二维电路结构,简单的二色法和设计规则检查DRC(Design Rule Cheek)是不能完全消除冲突的,往往需要引入切割才能完成拆分规定的要求。

如下图所示。在图中圆圈部分表示线间距小于最小线间距(minSpace),通过在U形底部引入分割将复杂图形分成了两部分,然后将分割后的图形置于两块掩膜版上从而达到了消除冲突的目的。

图4 缝合式拆分

引入切割虽然可以解决原来的冲突,但是切割的最大问题是缝合(stitch)处对套刻误差(overlay)十分敏感,可能产生颈缩(分割后图形小于设计图形)和桥连(过曝光导致图形粘连)现象。为减少颈缩现象可以在缝合点引入一定程度的交叠。此外,对于切割引起的新的冲突又需要进一步的优化和切割,直至最终的冲突数最小。如果引入切割仍然不能解决冲突,就只能对版图进行重新设计。应当在设计之初就考虑到版图中的特殊拓扑结构,如环形,U形,H形等,尽量避免这些结构可能产生的影响。

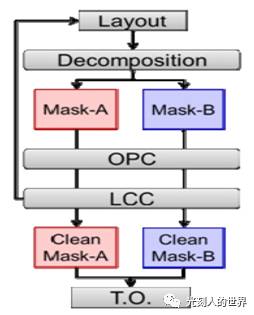

对版图拆分完成后,就需要对两张掩膜进行OPC(optical proximity correction)等分辨率增强技术,提高光刻的成像质量。紧接着进行光刻可行性检查(lithography compliance check),清除坏点(Hotspot)等操作。其中这样的过程需要反复操作多次,直至满足设计要求。DPT数据处理流程如图所示。

图5 DPT版图数据处理流程

双重光刻面临的挑战

双重光刻技术只需对现有光刻基础设施进行很小的改动,就可以有效填补更小节点的光刻技术空白。然而,双重光刻仍然会带来一些挑战。

(1)套刻精度是需要考虑的关键问题,因为两套图形必须非常精确地对准以避免电路错误。由于两次曝光的对准误差直接和最终的关键尺寸(critical dimension)误差相联系,当通常的CD误差认为是最小尺寸的10%时,由于需要考虑双重图形的对准误差,CD误差只允许是最小尺寸的5%。同时对掩膜版上图形的精确放置(placement)也提出了挑战,对分割出来的掩膜相互之间的叠合离散要求也变得十分复杂与严格。

(2)另一个关键点还在于寻求一种合适的高对比度非线性光刻胶或对比度增强层材料。因为第二次曝光易对第一次曝光图形产生影响,因此需要其能够吸收来自邻近曝光的弱光,但又不会形成图案;需要这种光刻胶能同时兼顾导线和间距区的曝光,且更适合实现光学临近效应。

(3)双重曝光降低了光刻机的要求,但也提高了掩膜制造的难度和设计的难度。掩膜的设计需要合理地分割掩膜版图形,并检验分解正确性。这也正是可制造性设计(design for manufacturability)的目的,使设计出的产品最终可以生产出来

在双重光刻的实现中,套刻精度是不得不面对的关键问题,因为两套图形必须精确地对准在一起以保证线宽及其均匀性,这是量产的重要参数。套刻精度误差来源于一系列可能的因素包括图像校准误差、晶圆变形、掩模扭曲、过程误差等,一般难以完全消除。

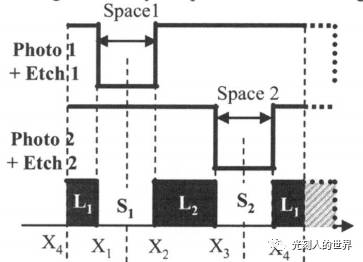

如图6所示,第一次曝光图形的中心位置为S1,第二次曝光图形的中心位置为S2。线宽L1由晶圆边界X4和曝光图形边界X1确定,线宽L2由两次曝光图形的边界确定。在版图确定的情况下,S1的位置决定了L1的线宽,S1,S2的套刻误差决定了L2的线宽,这样最终线宽及其均匀性也就由两次曝光的位置S1,S2确定。对于45nm半周期节点,最小的线宽尺寸为45nm,如果可接受的CD变化范围为10%,那么套刻误差必须控制在4.5nm以内。综合各种因素,目前而言,3nm的套刻精度被认为是广泛认可的精度目标。

图6 套刻误差对线宽及其均匀性的影响

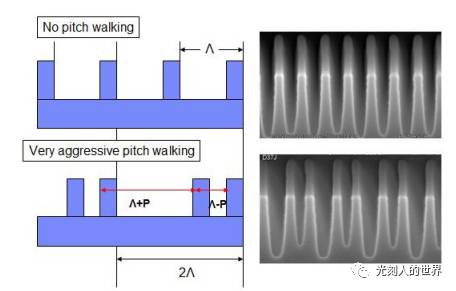

双重光刻虽然增强了图形分辨率,降低了对光刻机分辨率的要求,但是每次曝光时线条的尺寸仍然与单次曝光相同。因此,光刻机的成像质量仍然会影响到线条的尺寸。此外,如果光刻工艺控制不够严格,还有可能出现周期移动——每次曝光的线宽偏差以及第二次曝光相对于第一次曝光图形套刻误差都将导致图形局部周期性的起伏。

图7 套刻误差引起的周期移动

参考文献

[1]韦亚一。 超大规模集成电路先进光刻理论与应用[M]。 科学出版社, 2016.

[2]姚树歆。 基于32nm光刻双重图形技术的研究和工艺实践[D]。 复旦大学, 2011.

[3]Arnold, W, M. Dusa, and J.Finders. “Manufacturing Challenges in Double Patterning Lithography.”IEEE International Symposium on Semiconductor Manufacturing IEEE Xplore,2006:283-286.

[4]Drapeau, Martin, et al.“Double patterning design split implementation and validation for the 32nmnode.” 6521(2007):652109-652109-15.

[5]Yuan, Kun, J. S. Yang, and D.Z. Pan. “Double Patterning Layout Decomposition for Simultaneous Conflictand Stitch Minimization.” IEEE Transactions on Computer-Aided Design ofIntegrated Circuits and Systems 29.2(2010):185-196.

编辑:jq

-

集成电路

+关注

关注

5400文章

11689浏览量

364529 -

光学

+关注

关注

4文章

766浏览量

36590 -

光刻机

+关注

关注

31文章

1159浏览量

47730

原文标题:双重光刻概述

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

芯片制造:光刻工艺原理与流程

IC载板制造商需要了解的光刻技术信息

用来提高光刻机分辨率的浸润式光刻技术介绍

对于双重光刻你们了解多少?

对于双重光刻你们了解多少?

评论