据IPNest机构预测,2015~2024年全球接口类IP保持16%的平均年复增长率。未来几年,在主流的五大类接口IP,包括USB、PCIe、DDR、D2D&Ethernet、MIPI的市场份额方面,DDR IP市场需求强劲,将持续保持前三的市场份额。

但是,目前在DDR IP的市场上国内IP企业占比很小,究其原因,主要是由于DDR PHY具有较高的技术门槛,要在这类PHY上实现突破并不容易。

首先与其说DDR PHY是一个芯片技术,不如说DDR PHY是一门系统工程。DDR的数据传输采用并行多位、单端突发的传输模式,对电源完整性PI(Power Integrity,电源完整性)和信号完整性SI (Signal Integrity,信号完整性)的要求很高。另一方面,DDR可以说是对训练(Training)要求最多的接口。各种训练是否获得最佳的结果直接影响DDR工作的可靠性。

对于PHY开发人员来说,既要懂物理层的设计,也要懂训练算法的设计,只有这样才能开发出可靠的产品,然而这又无形中抬高了设计的门槛。最后,如何实现高速的单端信号传输,是DDR IO设计的一大考验。

作为一家专注于半导体IP研发和服务的高科技公司,芯耀辉科技看准了企业的需求和市场机遇,通过可靠的SI和PI分析、优化的训练算法设计、高性能的IO设计等一系列技术创新,成功突破了DDR PHY的技术瓶颈。

关键技术点一:可靠的SI和PI分析指导

DDR数据传输的特点是:多位并行传输,单端数据突发模式。目前SoC可以集成多达72位(DDR4带ECC)的DDR接口,多位并行传输在封装和PCB上的布线是非常复杂的,很多走线有一定等长要求,同时还要尽量减小线间串扰,所以合格的封装和PCB设计是一大挑战。另外突发模式的传输,SSO(Simultaneous Switching Output)噪声也会严重影响DDR的性能。所以DDR稳定的工作需要可靠的SI和PI分析。

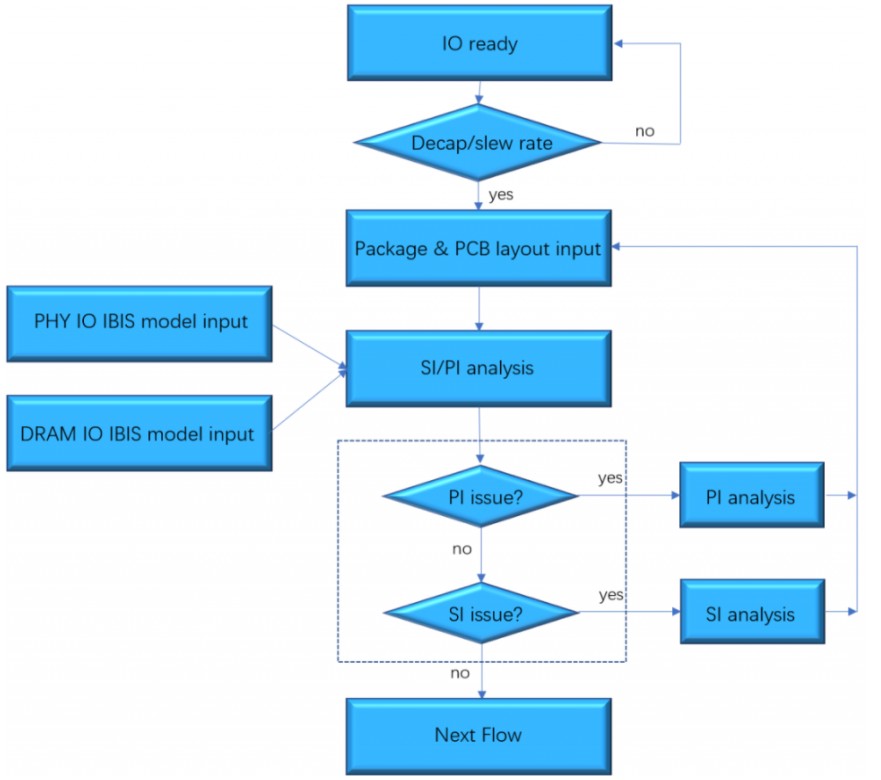

在芯片开发早期,确定好芯片的PAD规划和封装规划,对于设计后期优化DDR的SI和PI性能至关重要。芯耀辉在系统级芯片设计早期、IO准备阶段就开展SI和PI的分析,提前帮助客户规划,以确保集成的DDR PHY的量产性能。如下图2所示为芯耀辉的SI和PI流程示意图。

图2 芯耀辉SI和PI流程示意图

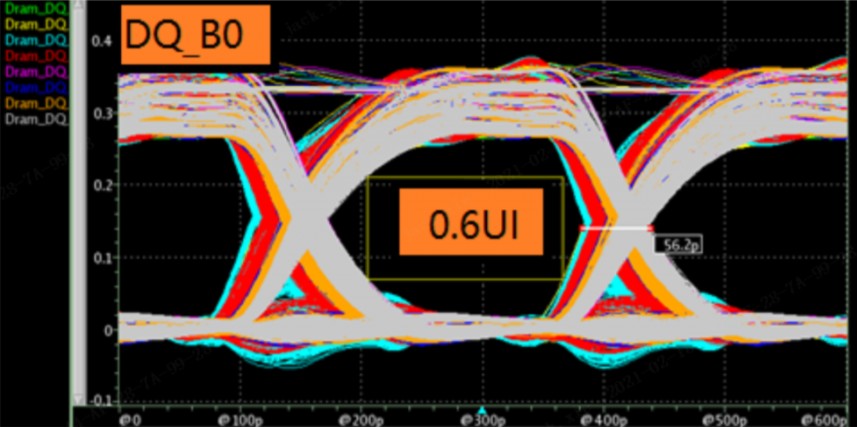

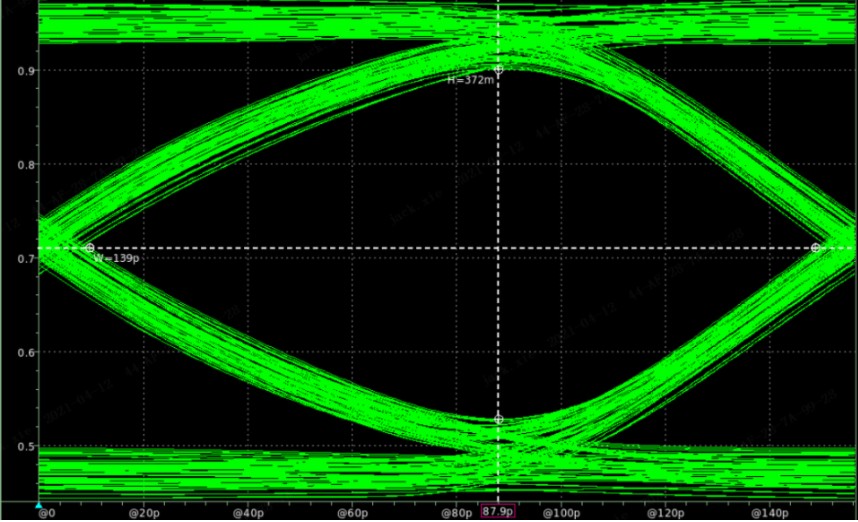

另外,芯耀辉团队还开发出了一套特殊码流分析技术。通过该技术,在设计阶段可以高效地分析封装和PCB设计是否满足DDR眼图的要求,可以快速定位缺陷,并指导客户优化完善。图3给出了一个实际合作案例,展示了系统设计最终完成后的眼图质量。

图3 芯耀辉LPDDR4X-3733仿真写数据眼图

关键技术点二:高可靠性训练设计

DDR系统的稳定工作离不开各种训练。在启动的时候需要做初始化的CA Training,Write Leveling,Read Leveling和 Write Eye Training等一系列训练,对于DDR4、LPDDR4及以上的更高协议,还需要VREF的二维训练。基于纯硬件的方式无法提供复杂的训练范式。例如JEDEC的DDR4协议里面规定了DRAM只能提供简单的01010101等范式, 这对于高速DDR的训练是不足够的,因为这些范式频率单一,无法反映数据通道衰减带来的码间串扰(ISI)。另外,不同范式在终端的反射也会不一样。所以如果采用JEDEC规定的简单范式来训练DDR,特别是在较高速率下,不能得到一个最优化的训练结果。

芯耀辉的DDR PHY采用基于固件的训练方法,可以设置不同的范式,如PRBS范式、特殊设计的扫频范式等。显然此类范式能更全面的反映数据通道特性,因为它包含了高频、中频、低频信息,以及长0和长1带来的码间串扰等问题,可以保证获得更优的训练结果。

初始化的训练完成之后,芯片内部温度和电压会随着工作状态和环境温度的变化而变化,此温度和电压的变化会让训练的结果偏移理想值,使得DDR的读写裕量减小,严重的情况还会造成读写数据错误。芯耀辉开发了一种可以动态检测芯片内部温度和电压变化的技术,通过实时补偿各种训练结果,保证数据的读写具有足够的裕量,确保DDR工作的稳定性。

关键技术点三:高性能DDR IO设计

信号码间串扰和走线的阻抗不匹配带来的信号反射严重影响数据通信。为了保证DDR数据读写的可靠性,在DDR IO设计中,芯耀辉采用了FFE(前向反馈均衡)和DFE(判决反馈均衡)技术。

FFE 前端预均衡

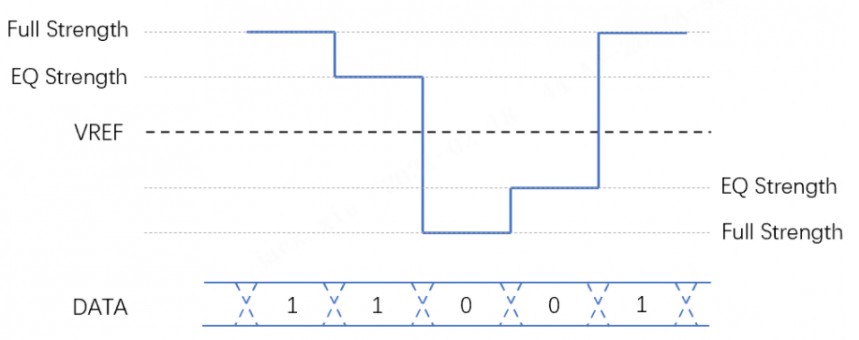

FFE前端预均衡是在DDR TX端采用的技术。因为数据通道有衰减,使得信号高频部分被抑制较大,低频部分被抑制较小,所以在RX端看到的眼图眼高和眼宽均比较小。FFE的思想就是减小低频分量的能量,使得信号的高频低频部分在信道之后达到均衡。图4展示了FFE原理,如果信号有0-》1的或者1-》0的变化,则输出满强度(Full Strength)的信号,如果信号是连续的1或者0,则输出均衡强度的信号(EQ Strength)。

图4 FFE前端预均衡原理示意图

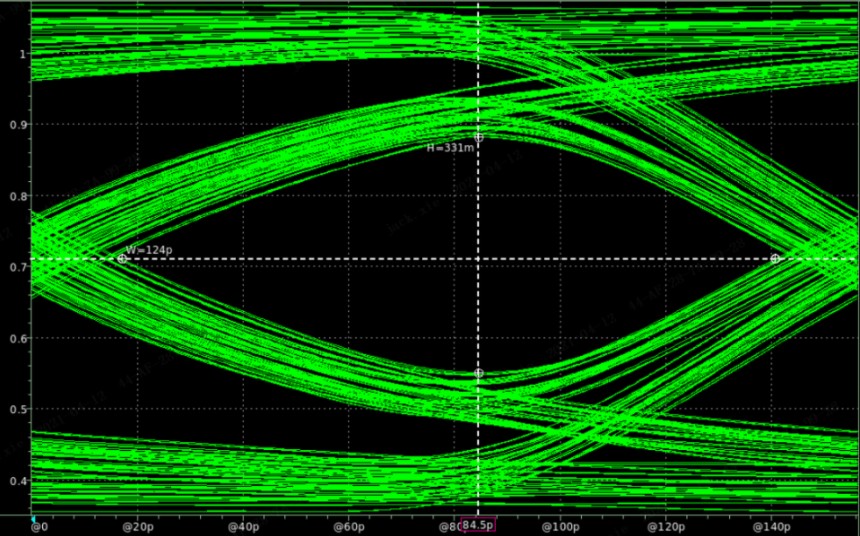

图5 展示了在RX端,数据速率是6400Mbps时,关闭FFE和打开FFE的仿真示意图。可以看到,打开FFE的眼图质量明显好于关闭FFE的眼图质量。

图5 芯耀辉仿真效果示意图(6400Mbps),左图没有打开FFE,右图打开FFE

芯耀辉采用可编程的前端预均衡方案,通过设置不同参数可以获得不同的均衡效果,以适应各种应用场景的需要。

自适应算法支持的接收端DFE(判决反馈均衡)

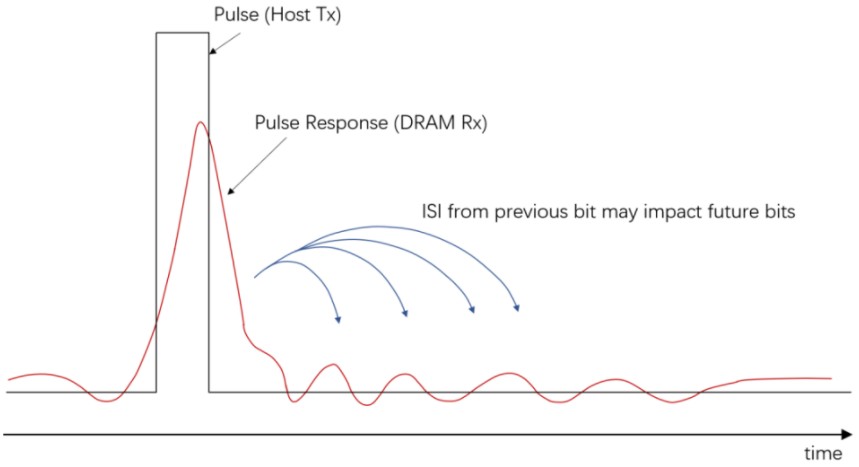

信号的码间串扰可通过脉冲响应(pulse response)示意图理解,如下图67所示。

图6 经过信道的脉冲响应

当脉冲信号经过信道时,因为高频衰减和信道反射,会形成一个拖尾的波形,前一个bit的信号会影响将来bit的信号质量。DFE的原理是:判断之前几个bit的信号是1或者0,然后通过加权和反馈相加,减弱前bit信号的拖尾影响,以达到改善当前bit信号质量的目的。相比于CTLE等均衡技术,DFE不会放大噪声信号,因此固态技术协会在JEDEC79-5 规范中正式引入了DFE技术,目的就是为了增强接收端的能力。

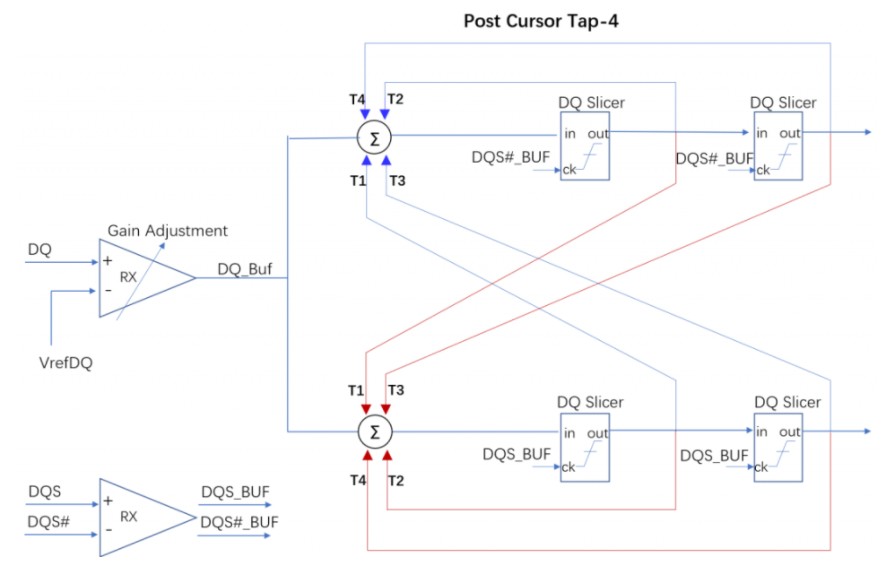

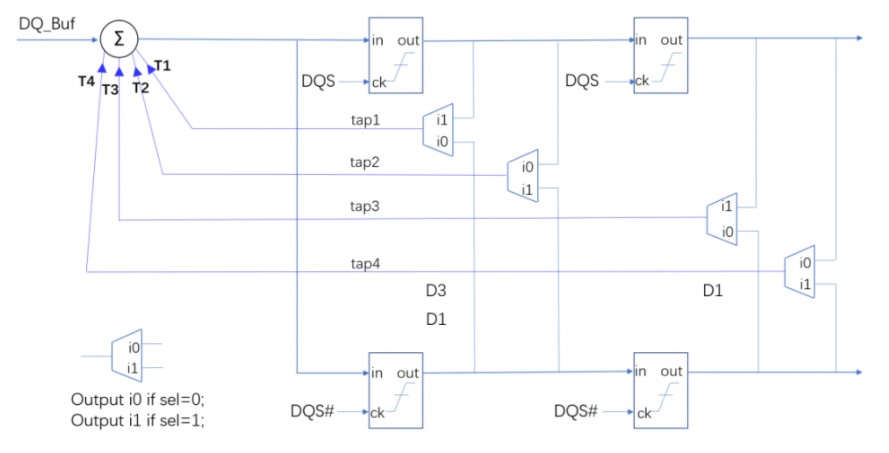

图7是常见的4 tap DFE架构,也是JEDEC规范推荐的架构之一。因为DQS的上升沿和下降沿均会采样DQ,所以采样电路分为上下两个数据通路。两个数据通路的4个采样值经过加权系数处理后会反馈到每一个数据通路对应的求和器(∑),从而减去这4个之前信号对当前信号的ISI影响。这种结构采用了两个求和器,会加大DQ_Buf端的负载。另外4个采样值均需要直接反馈到两个求和器,会使得芯片内部连线比较复杂,影响高速性能。图8是DFE的另一种架构,这种结构通过MUX选择两路数据通路的采样值,并把选择后的值送到求和器进行EQ处理。因为只用到了一个求和器,减小了芯片内部的连线复杂性,最重要的是减小了DQ_Buf端的负载,提升了高速性能。

图7 常见的4-tap DFE架构

图8 另一种常见的4-tap DFE架构

DFE各级tap的加权系数可以通过手动设置,前提条件是要得到信道的参数,这样做不适合产品的大规模量产,因为对不同的产品来说,它的IO特性、信道参数是有随机偏差的,同样的一套设置不能保证每个产品都有最佳的DFE性能。通过自适应训练得到DFE各级tap的系数是目前主流的方式。芯耀辉的DDR PHY提供了一套特殊的固件训练机制,DFE的各级tap的反馈系数可以通过训练快速得到,自适应程度高,可保证每一颗芯片都有更优的DFE性能,有效减小码间串扰和反射造成的影响。

关键技术点四:支持多频点的快速频率切换技术实现低功耗设计

DDR是SoC系统中的功耗大户,如何减小DDR的功耗一直是DDR技术革新的动力和方向之一。最直接的方法就是降低供电电压,而这正是DRAM规范的演进之路。另一方面,从DDR4和LPDDR4开始,DRAM规范定义了POD IO 架构(针对DDR4和DDR5)、LVSTL IO架构(针对LPDDR4和LPDDR5)和数据总线倒置(DBI)技术,能有效地减小IO端的功耗。

以上降低功耗的方法是JEDEC规范限定的技术,芯耀辉还开发出一种动态频率切换技术,能有效降低系统总功耗。该技术在DRAM初始化的时候可以训练多达多个频率点的配置,并保存相关训练结果。当系统确定不需要DRAM工作在高频率时,可以通知DDR控制器,然后DDR控制器会通知DFI,并让DRAM进入自刷新状态,之后频率切换就会自动在DFI和DDR PHY内部进行,频率切换完成之后DDR控制器则会让DRAM退出自刷新,这样DDR就可以切换到一个较低的工作频率,从而降低功耗。相较于同类产品,该技术最大特点是整个过程无需固件接入,在新的频率点无需重新做训练,从而快速稳定地实现频率切换。

总结

未来,市场对DDR PHY的需求持续增长,在先进制程上的需求更加突出。芯耀辉较早切入了基于FinFET工艺的IP开发,通过不断的技术创新,成为目前少数能提供先进制程、优越性能,稳定可靠的DDR PHY的本土企业之一。

百尺竿头,更进一步,芯耀辉人必将以提供高性能的接口类IP,高品质的设计服务为己任,奋发图强,助力携手合作广大芯片设计公司及晶圆代工厂,推出更优秀的产品,助力提升中国芯片产业的发展。

本文综合整理自芯耀辉科技 EDN电子技术设计 半导体行业观察

责任编辑:pj

-

半导体

+关注

关注

334文章

27305浏览量

218169 -

数据传输

+关注

关注

9文章

1882浏览量

64566 -

DDR接口

+关注

关注

0文章

5浏览量

7534

发布评论请先 登录

相关推荐

芯耀辉DDR PHY训练技术简介

芯耀辉推出可编程的前端预均衡方案

芯耀辉推出可编程的前端预均衡方案

评论