本文介绍了在通信系统中,同步Buck变换器上部功率MOSFET和下部功率MOSFET的工作特点,同时讨论了在设计高效率的同步Buck变换器时,选取上部和下部功率MOSFET原则;介绍了一种新型的采用栅极屏蔽的功率MOSFET,极低的漏栅极米勒电容适合于上部功率MOSFET的应用;还介绍了一种适合于下部功率MOSFET应用的具有超低导通电阻的功率MOSFET,两者的配合实现超高的变换效率

目前,通信系统要求越来越快的处理速度。其内部专用集成芯片,处理器单元等电路所消耗的电流也越来越大;同时,为了减小系统的体积和尺寸,内部的低压大电流的DC/DC变换器不断向高频、高密度方向发展。频率的提高带来系统变换效率的降低,另外,由于世界范围能源危机和环境污染提出了对节能减排的要求,因此,基于高频的变换器必须采用新型的器件,从而可以保证系统既工作在高频状态下,实现小尺寸、小体积,又整体的提高系统的效率,实现节能减排的目的。效率的整体提高进一步降低了电源系统的发热量,提高系统的可靠性。通信系统内部的系统板上使用了大量的Buck变换器,本文将针对这种变换器进行详细的讨论。

Buck变换器工作特点

在通信系统的系统板上,通常前级是从-48V通过隔离电源或电源模块得到12V或24V输出,也有采用3.3V或5V的输出,目前基于ATCA的通信系统大多采用12V的中间母线架构,然后再由Buck变换器将12V向下转换为3.3V、5V、2.5V、1.8V、1.25V等多种不同的电压。常规的Buck变换器续流管采用肖特基二级管,而同步的Buck变换器下部的续流管却使用功率MOSFET,由于功率MOSFET的导通电阻小,导通也远远低于肖特基二级管的正向压降,因此效率更高。因此,对于低压大电流的输出,通常采用同步的Buck变换器得到较高的效率。

对于Buck变换器,有以下的公式 :

:

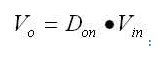

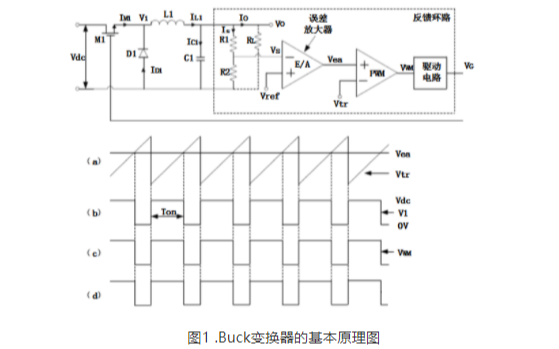

其中,Don为占空比。当输入电压较高时,占空比就小。因此,对于高的输入电压,而输出电压较低,即输入输出的电压差较大时,在一个开关周期,上部主功率开关管导通的时间将减小,而下部续流开关管导通的时间将自延长。图1为上部MOSFET管和下部MOSFET管的工作波形,阴影为产生开关损耗的部分。

图1 Buck变换器MOSFET管的工作波形

上部MOSFET管在开关的瞬态过程中,产生明显的开关损耗,同时也存在因为MOSFET导通电阻Rds(on)产生的导通损耗。导通平均损耗与占空比和导通电阻Rds(on)成正比,对于基于ATCA的通信系统。输入电压为12V,输入输出的电压差大,占空比小,因此导通损耗相对较小,而开关损耗占较大的比例。开关损耗主要与开关频率及MOSFET在开关过程中持续的时间成正比。开关持续的时间与MOSFET的漏栅极的米勒电容直接相关。米勒电容小,开关持续的时间短,因此开关损耗降低。因此对于上部MOSFET管的功率损耗必须同时考虑到开关损耗和导通损耗。对于MOSFET,通常为了降低导通电阻Rds(on),就要采用更大面积的晶圆,这样就可以得到更多的小单元,多个小单元并联后总的导通电阻Rds(on)就降低,但同时也会增加漏极和栅极的相对面积,也就增大了漏极和栅极米勒电容。

从波形可以看到,对于下部MOSFET管在开关的瞬态过程中,没有产生明显的开关损耗。通常MOSFET的关断是一个自然的0电压的关断,因为在MOSFET的漏极和源极有一个寄生的电容,由于电容的电压不能突变,因此在关断的瞬态过程中,漏极和源极电压几乎为0,这样,在关断的过程中,电压与电流的乘积也就是关断的功耗为0。所以对于MOSFET,要想实现0电压的开关ZVS,关键要实现其0电压开通。

通常同步的Buck变换器为了防止上下管的直通,上下管有一个死区的时间,在死区的时间内,上下管均保证关断。那么在上管关断后,由于输出电感的电流不能突变,必须维持原来的方向流动,因此下部功率MOSFET内部寄生二极管导通,寄生二极管导通后下部MOSFET的漏极和源极的电压为二极管的正向压降,几乎为0,所以在寄生二极管导通后,MOSFET再导通,其导通是0电压的导通,开通损耗几乎为0。这样下管是一个0电压的开关,开关损耗几乎为0。因此在下管中,主要是由导通电阻Rds(on)形成的导通损耗。下管的选取主要考虑尽量用低的导通电阻Rds(on)。

此外,为了减小在死区时间内由于体内寄生二极管产生的正向压降功耗和反向恢复带来的功耗,通常会并联一个正向压降低、反向恢复时间短的肖特基二极管。过去主要是下管MOSFET的外部并联一个肖特基二极管,现在通常将肖特基二极管集成在下部MOSFET管内部。起初,是将一个单独的肖特基二极管和一个MOSFET封装在一起,后来是将它们做在一个晶圆上。将一个晶圆分成两个区,一个区做MOSFET,一个区做肖特基二极管。

由于二极管具有负温度系数,并联工作不太容易,在一个晶圆上分成两个区做MOSFET和肖特基二极管,那么肖特基二极管在与MOSFET交界的区域,温度高,离MOSFET较远的区域,温度低。当肖特基二极管温度高时,流过更大的电流,所以与MOSFET交界的肖特基二极管区域由于温度高,流过的电流更大,温度进一步上升,就可能产生局部的损坏。目前,通常将特基二极管的单元做到MOSFET的单元里面,这样就可能得到更好的热平衡,提高器件的可靠性。

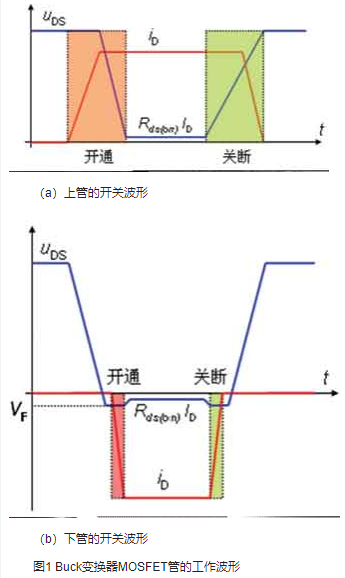

适用于上管的SGT新型功率MOSFET

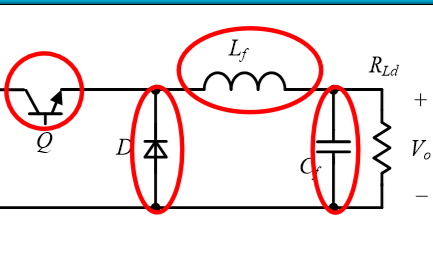

通常,对于MOSFET,导通电阻Rds(on)和漏极栅极的米勒电容是一个相互矛盾的参数,除非采用新的技术,才能解决这个问题。对于同样面积的晶圆,如果要减小米勒电容,就必须想方法减小漏极和栅极相对接触的面积,最为直观的方法就是对栅极采用一定的屏蔽技术,从而减小漏极和栅极的相对电容。图2就是采用AOS的专利技术SGT所制作的新型的具有极低漏极栅极米勒电容的功率MOSFET。

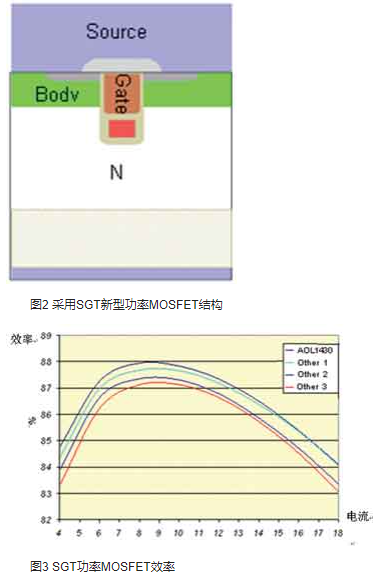

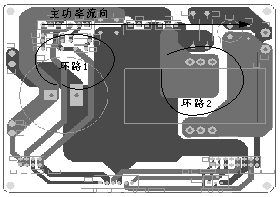

注意到图2中,除了栅极结构,其他的部分就是标准的采用Trench工艺的MOSFET。栅极被分割成上下两个部分,下部分用一些特殊的材料屏蔽起来,下部分在内部和上部分的栅极相连,而栅极的屏蔽层被连接到源极,从而减小漏极栅极米勒电容。用这种技术设计的MOSFET如AOL1464,其Vds为30V,Vgs在10V条件下Rds(on)为6.2mΩ,而其Crss只有20pF,极大地减小了开关过程中米勒平台的持续的时间,降低了开关损耗。AOL1430,其Vds为30V,Vgs在10V条件下Rds(on)为2.5mΩ,而其Crss为50pF。图3中,下管采用AOS的AOL1428,上管采用AOL1430和其他厂家目前Crss最低的器件的效率曲线,可见,上管采用AOL1430具有非常高的效率。注意:输入电压12V,输出电压 1.7V,开关频率300kHz。

适用于下管的超低Rds(on)功率MOSFET

下管主要是导通损耗,因此要尽量使用导通电阻Rds(on)低的功率MOSFET。目前,主要通过改进工艺和使用新的材料,在同样面积的晶圆上,降低每个单元的电阻,同时尽可能的设计出更多的单元,提高单元的密度,以形成低的导通电阻Rds(on)。

图4中,每个MOSFET单元,在相同额定的Vds电压条件下,导通电阻相同,其具有更高的单元密度,在水平和垂直两个方向都尽可能缩小了尺寸。AOS的AON6702采用DFN的封装,其Vds为30V,Vgs在10V条件下Rds(on)为1.9mΩ,同时内部集成的具有优异特性的肖特基二极管。

结论

(1)同步Buck变换器的上管同时具有开关损耗和导通损耗,在输入输出压差大的应用中,开关损耗为主。导通损耗与MOSFET的导通电阻Rds(on)成正比,开关损耗与漏极栅极米勒电容相关。

(2)采用SGT技术的功率MOSFET具有超低的漏极栅极米勒电容,从而减小了开关过程中米勒平台的持续的时间,降低了开关损耗。

(3)同步Buck变换器的下管只有导通损耗,开关损耗几乎为0。要选取 Rds(on)尽量小的MOSFET。使用新工艺和新材料,可以提高晶圆上单元的晶胞密度,降低单元的电阻密度。

责任编辑:gt

-

处理器

+关注

关注

68文章

19404浏览量

231085 -

变换器

+关注

关注

17文章

2109浏览量

109520 -

通信系统

+关注

关注

6文章

1204浏览量

53454

发布评论请先 登录

相关推荐

Buck-Boost变换器的两种工作方式解析

ZCS-PWM Buck变换器的工作原理是什么?

DCDC降压型BUCK变换器应用于汽车电子系统中的设计技巧有哪些?

BUCK变换器设计

Buck变换器的工作原理结构及其过程分析

Buck变换器的EMC分析

DCM_Buck_Boost变换器的建模与控制设计讲解

buck变换器设计_自制buck变换器

buck变换器的工作原理和降压原理等资料详细概述

Buck变换器的工作原理与设计的学习课件免费下载

Buck变换器的工作特点及在通信系统中的应用

Buck变换器的工作特点及在通信系统中的应用

评论