复用不仅是SOC设计思想的核心,也是解决SOC测试的基础。本文在分析SOC的基本概念和特点的基础上,从复用的角度对现有的SOC测试方案进行分析和综述,并探讨了亟待解决的问题。

1 引言

90年代国际上出现的SOC概念,以系统为中心、基于IP模块多层次、高度复用的设计思想受到普遍重视和广泛应用 [1,2]。SOC的高集成度和复杂度使得SOC测试面临挑战,传统的基于整个电路的测试方法不再适用。对于IP模块和SOC而言,在电路设计向可复用这一目标发展的同时,测试中的复用也变得愈加重要,成为解决SOC测试的关键 [3],也成为目前该领域研究的焦点。本文在分析SOC与SOB(system on board)本质区别的基础上,阐明复用对于SOC测试的重要性,对现有主要几类基于复用思想的SOC测试进行分析。

2 SOC的测试

SOC使集成电路设计者分为两个部分:IP模块的设计者和SOC集成者(IP模块的使用者)[2,4,5] 。IP模块是设计者提供的具有特定功能和相关参数描述的模块;而SOC集成者利用它们和用户自定义逻辑(UDL)集成在一起,实现既定的功能。从表面上看,这种设计类似于传统的基于芯片的SOB 设计,但二者存在本质区别。

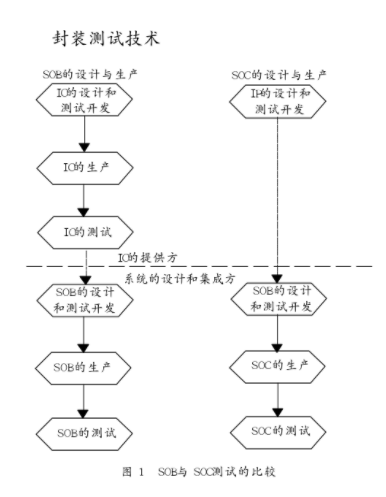

SOB中的IC是经制造生产和测试后的实体,因此对SOB集成者而言,测试是针对系统中IC之间连接的测试。在SOB的设计集成过程中,IC的制造商和系统的集成者有相对独立的测试开发和实施阶段,如图1所示。从描述的层次而言,SOC中的IP模块可以分为软核、固核以及硬核。每一个核又可以是若干更小的模块共同构成,但无论什么模块,相对于SOB中的芯片而言是虚拟器件,在进行SOC集成设计时都未经物理实现。

IP模块提供者对所设计的虚拟模块进行测试开发,却不能对IP模块进行实际的物理测试。因此IP模块设计者和SOC集成者的测试开发和实施将不再是彼此独立和分割的两个阶段。SOC集成者要完成包括IP模块在内的整个芯片的测试方案[2]。因此,SOC测试较传统的SOB测试而言,更加复杂,也更具挑战性。

3 复用技术与SOC测试

随着技术的发展和市场的需要,IP模块和SOC 的设计正逐渐以分布和并行的方式进行。来源于不同的各种IP模块的多层次复用是SOC的基础。IP 模块是对功能和实现方式的描述,是未经物理实现的虚拟器件,不同类型的IP模块有不同的模型和测试方法,IP模块的提供者虽然无法对模块进行物理测试,但必须向SOC集成者提供模块的测试信息,其中包括模块的测试方法、可测性结构、测试产生方法及测试集等 [2,4,6]。

如果不以这些模块的测试信息为基础,SOC集成者就无法对高达千万门级的芯片进行测试,而复用则是SOC测试的关键。因此,国际上IEEE P1500工作组和VSIA(virtual socket in ter face alliance)联盟正在制定相关的国际标准[6,7] ,研究焦点集中于规范IP模块设计者和SOC集成者之间的软硬件接口,如模块测试语言(CTL,)和可扩展结构,以实现SOC测试中IP模块测试信息的即插即用。

但标准并不进行复用方法和测试集成及优化的研究,有许多问题尚未解决。因此采用何种方式复用,如何解决复用中遇到的问题成为目前 SOC测试研究的焦点之一。从复用的角度,现有的SOC测试解决方案大致分为两类:直接复用和间接复用。

3.1 直接复用

该方法的基本思路是自顶向下,直接在芯片级使用已有的模块测试信息,通过实现对每个IP模块的测试访问从而解决整个芯片的测试[8]。核心是通过构建测试通路实现对各IP模块的测试访问,前提是各IP模块都具有良好的可测性和完整的测试信息。这类方法的有效性关键在于两个方面,即各模块原有测试信息的质量和在SOC中各模块测试访问的实现。具体的方案如下。

① 测试总线。ARM公司发布的32位AMBA(advanced microcontroller bus architecture)总线结构,通过解决每个IP模块的测试访问问题来最终完成整个SOC的测试,但其兼容性、测试费用及测试时间上有其局限性 [9]。Duel Technologies公司也作了类似的工作,提出了“测试总线”,连接每个IP模块,虽然优化了测试所占用的芯片面积,但无法同时将多个IP模块连到总线上进行测试。

② 端口访问。Intel公司提出将每个IP模块的接口端通过多路选择器接到芯片的引脚上直接进行访问[10]。但当IP模块增加时,对多路选择器的控制就会过于复杂,且该方法对IP的端口数有明确的限制。

③ 模块的透明模型。文献[11]提出一种基于IP模块透明模型的方法,它要求每个IP模块都有一种工作模式——透明模式。当对SOC中某一个IP模块进行测试时,其它模块均处于透明模式,从而为该模块提供测试访问通路。这种方案较前两种方案减少了硬件开销,但对IP模块的设计有特殊要求,且数据传输通道多位串行会导致测试时间过长。

④ 边界扫描。Texas Instrument公司利用IEEE 1149.1标准中的边界扫描测试(BST)技术,通过标准的扫描链串行访问IP模块,该方案是将用于解决SOB的测试技术移植到了SOC上。该方案的硬件开销会随着电路集成度提高而加大,测试时间也会随着SOC规模的增加变得无法接受[12]。

3.2 间接复用

这类方法的基本思路是自底向上,利用每个模块级的测试信息,通过综合转换形成该模块在芯片级可以实施的测试信息,直至形成整个芯片的测试。核心是以系统为出发点,利用各IP模块的测试信息,综合SOC的结构或功能特点,形成SOC 对各IP模块的测试数据和方案。具体的方案如下。

① 宏测试。从设计出发,在自IP模块向系统集成的过程中不断将模块的测试信息进行扩展,直至芯片级。其中较为典型的是Philips公司将解决IC测试的Macro Test技术用于SOC测试[13]。其基本思路是将每个IP模块的测试信息以测试协议描述,结合整个系统的设计,识别合适的访问路径扩展到芯片级,再通过芯片级的测试协议调度每个模块的测试顺序,最终通过单独测试每个IP的方法来完成SOC测试。该方法对SOC中的IP模块及其测试信息有严格的规定。

② 层次复用。文献[13]提出了一种层次法,基本思路是针对系统进行分析,提取系统中与待测IP 模块的约束关系,使模块在约束下直接产生测试集,进而解决整个芯片系统的测试问题。该方法每次只考虑一个模块,先对每个模块产生功能约束,将约束和该模块一起综合,形成一个从芯片级可以访问的对应电路,再用商业软件对模块内部的故障生成测试。但当该技术应用到集成度很高的SOC时,模块本身测试的生成变得非常困难。如果SOC中的模块是多层次复用的,需要进一步分解成子模块,约束条件的提取变得十分繁复。为解决这个问题,文献[14]提出一种新的层次地提取可重复使用的约束方法,并在提取约束时利用综合工具剔除冗余的逻辑部分,提高了测试生成效率,使其更有效。 中联网

③ 功能复用。SOC的功能日益强大,其中许多都含有内嵌处理器和存储器。文献[16],[17]提出,在SOC内部通过内嵌处理器模块和存储器模块实现对其他IP模块的测试。具体就是首先将各IP模块的测试数据压缩并存入存储器模块,再由内嵌处理器利用这些数据,对IP模块进行测试并收集响应进行测试分析。这种方法充分利用了SOC内部资源和已有的各IP模块测试信息,可以实现芯片内部的高速测试。但测试数据处理和测试控制的复杂度都会随的SOC设计复杂度的加大而增加。

4 面临的问题

SOC内部晶体管集成度的增长远远高于芯片引脚的增长,有限的管脚资源使得外部数据带宽和内部数据带宽之间的差异越来越大[1]。这种差异不仅降低了内部模块的可测性,还加大了间接复用方案中测试生成的难度。同时,具有一定故障覆盖率的测试数据会随着电路集成度和规模的增加而增加,大量的测试数据会对直接复用方案中的测试访问的频率和带宽提出要求。

SOC嵌入了类型丰富的IP模块,一些公司已将模拟电路、数字电路、嵌入式DRAM等不同形式的模块集成到芯片中。随着技术的发展,将有更多的电路类型被集成到SOC中,如嵌入式的FPGA、Flash、射频发生器等。混合信号测试在SOC测试中占有重要地位,现有的复用方案还未解决该问题。

前面分析的现有方案有的来自于专业厂商,有的是利用自己的技术传统,对原IC、SOB测试技术的改进,着眼于解决各自产品的测试问题,因此研究的出发点有局限性,各方案的适用范围有限。

5 结论

迄今为止,还没有一个贯穿IP模块和SOC设计始终的完整的SOC测试解决方案,因为这不仅需要尽快订立相关的国际标准,还需要进行一些关于复用方法上的研究,例如,如何在进行IP模块的测试开发中引入可复用的因素,使得模块级的测试信息对被集成环境具有更好的适应性,能被更高层电路模块的测试开发高效率地复用;研究基于复用的测试集成和优化技术,利用已有模块测试信息,集成出更高层模块的测试并保证其可复用性等。

编辑:jq

-

芯片

+关注

关注

457文章

51345浏览量

428237 -

soc

+关注

关注

38文章

4218浏览量

219269 -

IP

+关注

关注

5文章

1724浏览量

150093 -

晶体管

+关注

关注

77文章

9796浏览量

139066

发布评论请先 登录

相关推荐

光通信中波分复用技术的优势

信道复用技术在移动通信中的应用

Advantest推出适用于V93000 EXA规模测试平台的先进功率多路复用器

soc技术在智能设备中的应用

最新SOC芯片技术发展

soc芯片测试有哪些参数和模块

波分复用技术是如何工作的

密集波分复用和稀疏波分复用的区别

光纤是波分复用还是频分复用?波分复用和频分复用有什么不同?

简述多路复用技术的工作原理 多路复用技术有哪些

频分多路复用和时分多路复用的区别有哪些

波分复用的特点 波分复用(WDM)和频分复用(FDM)的区别

多路复用技术主要有几种类型?它们各有什么特点?

频分多路复用的原理 频分多路复用方式的分类

浅谈复用的SOC测试技术

浅谈复用的SOC测试技术

评论