如今随着有源相控阵雷达技术的不断发展,雷达信号所需要实时处理的数据量也在迅猛的增大,这就使得数据流的高速传输面临着较大的挑战[1]。以往系统多采用并行方式传输高速的数据流,这种方式实现起来相对简单,但是当数据率超过1 Gb/s时,信号的同步管理变得十分困难,同时接口的数据对齐问题也影响着与外部设备的有效通信。为了解决这一难题,高速串行I/O技术应运而生。串行传输所需的引脚数少,降低了背板开发的要求,印制电路板的制作更加简单,同时可以满足远距离高速通信可靠性的要求,被各行各业运用在通信系统的设计中[2]。

为了适应串行技术发展的趋势,Xilinx公司也推出了内嵌高速串行收发器Rocket I/O的FPGA产品,并在此基础上开发了Aurora协议。Aurora协议是一款可自由使用相对较简便的点对点链路层协议。其设计目的是使其他高层协议可以很简单地运行在Aurora之上[3]。其中Aurora IP核支持与光纤的无缝连接,传输过程中抗电磁干扰能力强,集成度高,具有很强的灵活性。

1 Aurora IP核的实现

Rocket I/O是内嵌在FPGA中的一款高速串行收发器,支持多种通信协议标准,如Aurora、PCI Express、光纤通道、千兆以太网等[4]。该收发器提供单工或全双工的数据传输模式。

每个Rocket I/O支持622 Mb/s~3.125 Gb/s的数据传输速率,并且利用通道绑定功能可以实现更高的数据传输速率。收发器模块物理媒质适配层(PMA)集成了串行/解串器(SERDES)、时钟和数据恢复电路(CDR)、电流模式逻辑(CML)、预加重/均衡电路等,物理编码子层(PCS)集成了8 bit/10 bit编解码电路、循环冗余校验(CRC)、相位调整FIFO、弹性缓冲器、PRBS产生和检测等[5]。这些集成的模块可用于补偿信号的高额损耗,减小时钟的偏差和内部噪声对接收性能的影响,从而提高信号的质量。

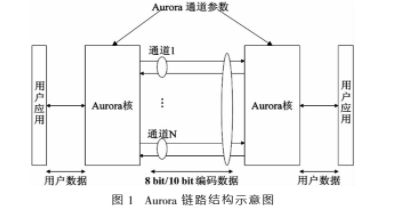

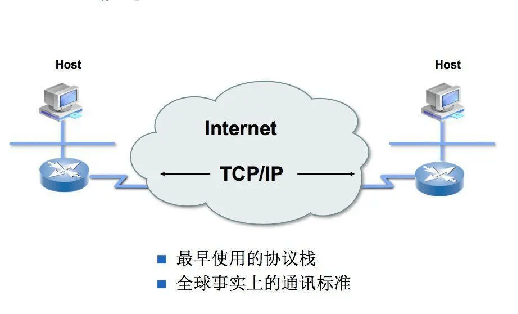

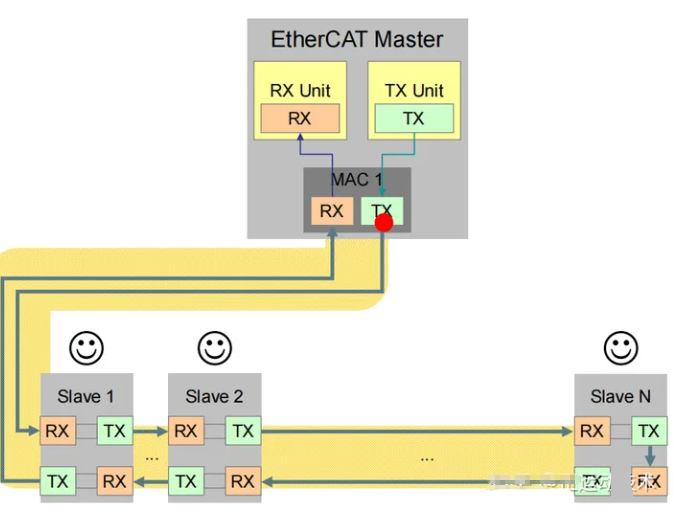

Aurora协议是一款高带宽、低成本、可扩展、框架简洁、适合点对点串行数据传输的协议。该协议支持专用的上层协议或符合工业标准的协议(例如以太网、TCP/IP),提供了透明接口的串行互连协议,其允许数据进行任何分组封装,可以使芯片间的数据传输在一个较高的水平而不需要改变已有的通信系统或计算机系统[6]。Aurora协议可以配置每个通路中的Rocket I/O工作在全双工或半双工的模式下,其链路结构图如图1所示。

Aurora IP核是Xilinx公司在Aurora协议和高速串行收发器Rocket基础上研发出来的硬核。该核嵌入在Rocket I/O模块中,提供了简单的用户接口,极大地方便了信号的可操作性。通过IP核用户界面可以改变Rocket I/O中复杂的控制结构。Aurora IP核主要包括本地流控制、用户流控制、用户数据接口、时钟输入与时钟修正模块、高速串行收发模块和状态信息控制模块[7-8]。

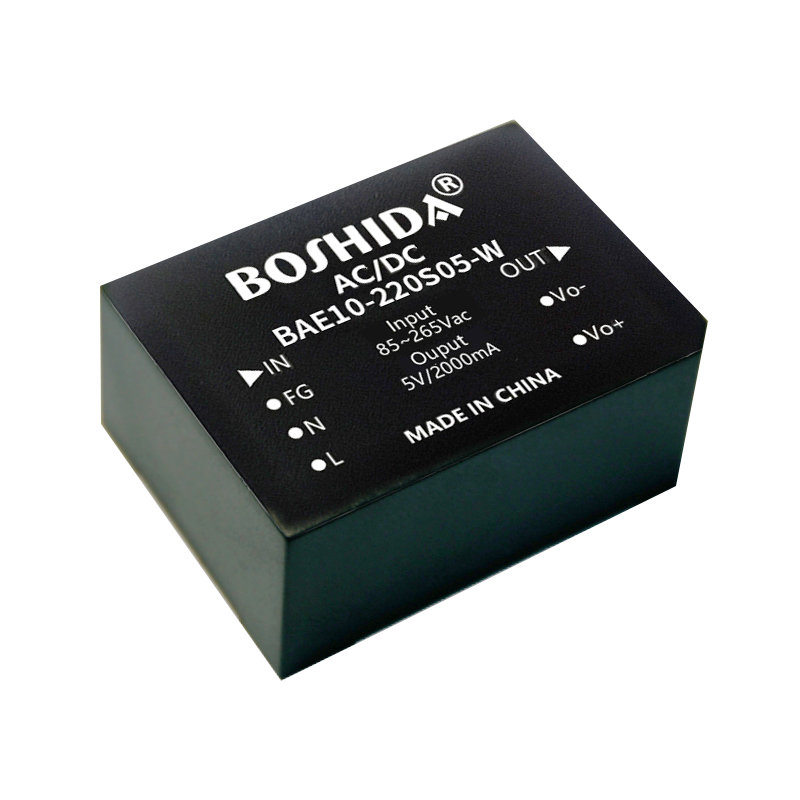

本系统所用Aurora IP核为全双工模式,通道的线速度为2 Gb/s,输入参考时钟为125 MHz,用户时钟100 MHz,发送和接收位宽都为16 bit,采用流控的数据传输模式。由于发送数据经过Rocket I/O进行了8 bit/10 bit编码,故而通道串行线性速率为1.6 Gb/s。IP核封装图如图2所示。

其中IP核设计的参考时钟需要选择高精度的差分时钟,这里选用3.3 V供电的贴片差分时钟,经过IBUFG一级缓冲直接连接到GTX的参考时钟输入端,而不能使用经过DCM分频/倍频而来的时钟。因为由DCM引出来的时钟抖动较大,Rocket I/O在数据传输时相当不稳定,会造成数据丢失。

由于Aurora IP核具有时钟补偿功能,在数据接口宽度为2 B的情况下,每5 000个user_clk就需要6个user_clk的时钟补偿,一旦启用时钟补偿功能,数据流将不能进入Rocket I/O,所以在Aurora IP 核收发器的两端需要加上一个16 KB的FIFO为数据缓冲做准备,以避免IP核在进行时钟补偿时的数据丢失,同时可以用来匹配AD采样信号数据时钟和用户时钟user_clk的不一致。解决方案程序如下:

process(USER_CLK)

begin

if USER_CLK‘event and USER_CLK=’1‘ then

count_16bit《=count_16bit+1;

if count_16bit》0 and count_16bit《=2 then

DO_CC《=’1‘; else DO_CC《=’0‘; end if;

end if;

end process;

IP核封装程序如下:

My_Aurora_AXI4_2Gbps is

Port (

GTX_CLK_125MHz : in std_logic; -- MUST

be 125 MHz

TXP ,TXN : out std_logic; --2 Gbps

RXP ,RXN : in std_logic; --2 Gbps

local_clk : in std_logic; -- 《=200 MHz

reset : in std_logic;

S_AURORA_TX_TDATA : in std_logic_vector

(15 downto 0);

S_AURORA_TX_TVALID: in std_logic;

S_AURORA_TX_TREADY: out std_logic;

M_AURORA_RX_TDATA : out std_logic_vector

(15 downto 0);

M_AURORA_RX_TVALID: out std_logic;

ERROR : out std_logic;

CHANNEL_UP: out std_logic

);

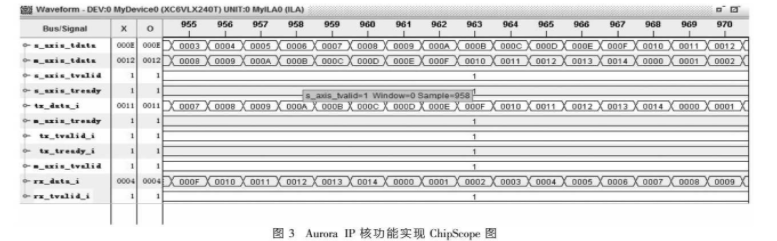

Aurora IP核功能实现ChipScope图如图3所示。

2 测试系统结构

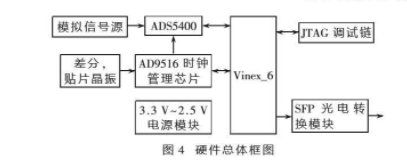

该系统主要由FPGA、ADS5400模/数转换器以及AD9516时钟生成模块、SPF光纤收发模块、电源模块等功能模块组成。首先高频信号经由ADS5400模/数转换器采样,送入并存储到FPGA的FIFO中。然后经过一系列的逻辑控制,高频数字信号进入Aurora IP核中,经过Rocket I/O进入SPF光纤模块将电信号转换成光信号,通过光纤进行有效的传输。系统总体框图如图4所示。

2.1 超高速A/D转换与系统时钟的实现

在系统发送端采用的是12 bit分辨率及1 GS/s采样率的ADS5400模/数转换器。ADS5400中可调节的精细增益、失调和相位可以大幅度地简化两个ADC的交错,这样就简化了I/Q接收机中两个ADC的平衡问题。ADS5400同时有着较好的信噪比,这使其在较高的中频条件下能够完成模/数转换,极大地提高雷达信号处理的速度。

ADS5400的输入时钟(也就是采样频率)由专用的时钟芯片产生,其写配置接口遵循SPI总线接口,采用125 MHz时钟频率经由FPGA向其中写入配置,其中时钟必须是独立的外部时钟且不能和Rocket I/O共用同一时钟,以防止芯片不能正常工作。此模块ADS5400输出采用双端口模式,clkout被2分频,使用内部参考时钟。

在本系统中,AD9516的输入时钟是由外部晶振产生的高精度差分时钟,频率为200 MHz,使用内部VCO,内部压控振荡器的频率为2 GHz。经过分频器在LVPECL端和LVDS端分别产生100 MHz的时钟信号。其中LVPECL端产生的时钟作为ADS5400的输入时钟,LVDS端产生的时钟作为FPGA的信号时钟,以便对信号在FPGA中进行进一步的处理,以满足信号的同源问题,时钟信号具有较大的灵活性。

2.2 性能测试

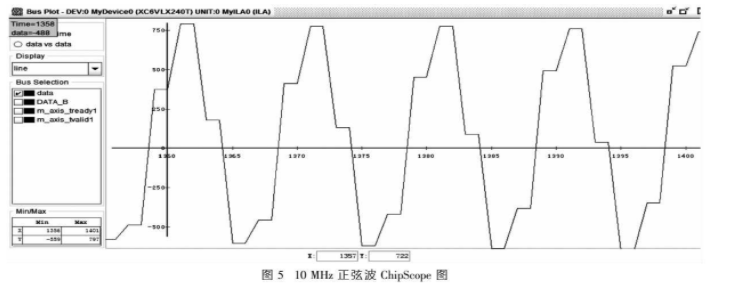

在本系统中采用了Rocket I/O进行光纤通信,为了测试系统的通信性能,Rocket I/O采用了全双工、流控制的工作模式,其数据传输速率为2 Gb/s。由于GTX内部采用了8 bit/10 bit编码,因而实际上传输的有效数据率为1.6 Gb/s。在SFP光纤收发模块发送器发送数据的同时,接收器立刻接收数据。本设计中选择Finisar公司的FTLF8519P2xTL光电转换模块。主要测试步骤为:(1)给FPGA 处理板上电,向ADS5400和AD9516写配置之后分别产生100 MHz的采样信号和100 MHz FPGA时钟信号;(2)信号发生器产生10 MHz的正弦波连接到ADS5400模/数转换器;(3)ADS5400把模拟信号转换成数字信号;(4)将转换完成的数字信号写入FPGA的FIFO中;(5)FPGA 将FIFO中的数据通过Aurora IP核经由光纤模块发送出去,同时光纤模块接收刚刚发送的数据,并将数据传入FPGA的FIFO中;(6)运用ChipScope观测发送和接收到的数据,比较数据传输是否正确。

经过长时间的测试,ChipScope抓取的发送和接收数据一致,这表明本系统的光纤通信模块能够正常地工作,完成了预期的设计。在硬件实现上的10 MHz ChipScope图如图5所示。

本文首先介绍了Rocket I/O在雷达信号处理中的应用,可以极大地提高通信卡之间的通信速率;然后描述了Rocket I/O功能和Aurora核实现高速通信的具体实现过程。整个系统主要实现了对超高速AD采样信号的高速光纤传输,数据传输速率达到了2 Gb/s,并且解决了不同通信卡进行数据传输Aurora时钟补偿时的数据丢失问题。同时,Aurora核自身有着通道扩展的功能,可以进一步提高数据的传输速率,并且可以在实际情况中根据不同的信号频率动态地调整采样频率。由于系统的可编程性,不需要对系统的结构进行大的调整,只需对具体功能进行有效实现,提高了系统的灵活性。

参考文献

[1] 李江涛.RocketIO高速串行传输原理与实现[J]。雷达与对抗,2004(3):48-50.

[2] SAVAGE S.Implementing high-speed serial and custom digital protocols thru FPGA technology and graphical programming techniques[C].Baltimore,2007 IEEE Autotestcon,2007:214-223.

[3] 林振华。基于PCI-X和RocketIO的高速数据传输系统设计[J]。现代雷达,2011,33(6):49-52.

[4] Xilinx.Aurora protocol specification[Z].2007.

[5] Xilinx.Virtex_6 FPGA GTX transceivers user guide UG366(v2.6)[Z].2011.

[6] 杨雷,龙哲仁,卢继华,等.LVDS高速并口通信协议设计[J]。电子技术应用,2013,39(3):119-122.

[7] Zhou Dexiang,Zheng Liping.Study of Aurora IP nuclear communication module based on FPGA[C].2011 IEEE 3rd International Conference on ICCSN,2011:581-583.

[8] Xilinx.LogiCORE IP Aurora 8B/10B V7.1 user guide UG766[Z].2011.

编辑:jq

-

FPGA

+关注

关注

1629文章

21736浏览量

603385 -

IP

+关注

关注

5文章

1708浏览量

149547 -

cdr

+关注

关注

1文章

50浏览量

18103 -

内嵌

+关注

关注

0文章

3浏览量

7477

发布评论请先 登录

相关推荐

高速点焊工艺中先进控制电源的关键技术探究与应用

【米尔-Xilinx XC7A100T FPGA开发板试用】+04.SFP之Aurora测试(zmj)

PROFINET通信协议是什么

NFC协议分析仪的技术原理和应用场景

USB协议分析仪的技术原理和应用场景

从表象到本质:深入探究TCP/IP协议

高速串行通信协议都有哪些

高速串行通信协议详解

epa通信协议是什么?epa协议介绍

epa通信协议是什么?epa协议介绍

CC-Link协议是什么?CC-Link协议详细介绍

高效节能的DC电源模块技术探究

基于以太网的EtherCAT协议技术

探究Aurora协议的高速通信技术

探究Aurora协议的高速通信技术

评论