01

概述

本文通过matlab自带的工具箱生成一个可编程FIR滤波器的硬件HDL代码,可生成VHDL或者Verilog HDL两种类型的代码。

02

具体操作步骤

新建一个matlab的脚本,键入下面两行代码,这里是直接调用matlab已经定义好的“dspprogfirhdl”模型,然后在simulink工具中打开该系统模型。

modelname = ‘dspprogfirhdl’;open_system(modelname)

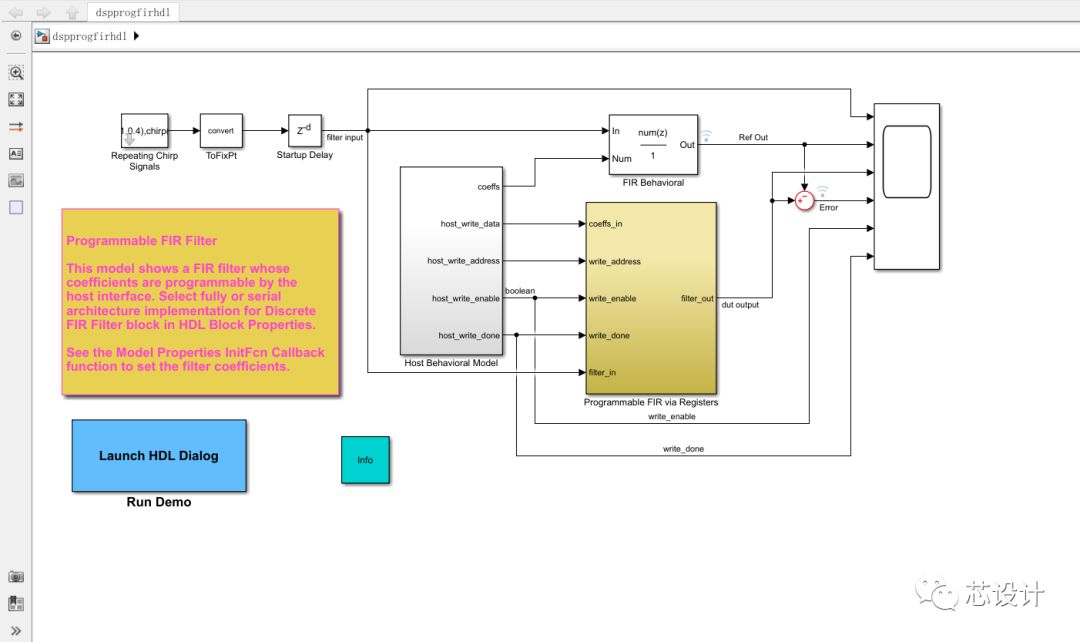

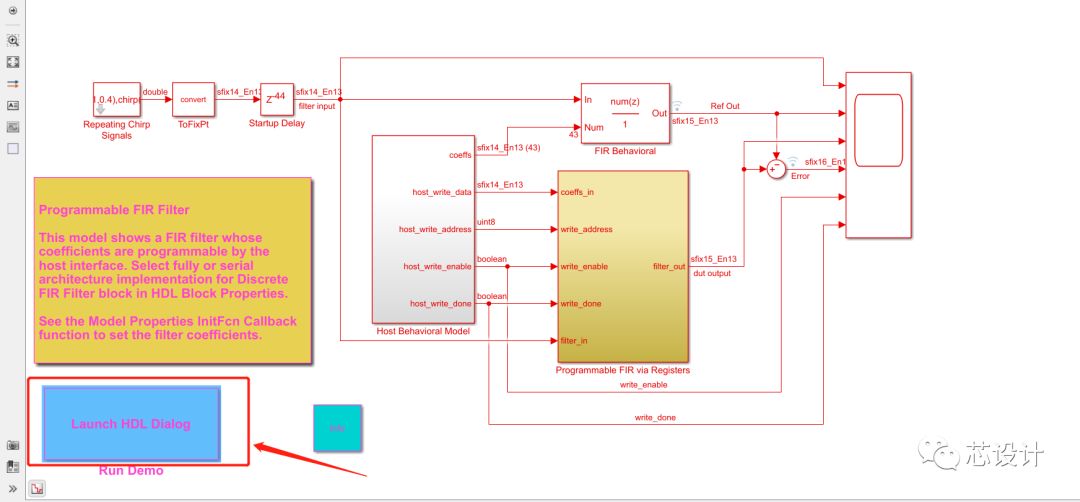

运行上面两行代码后,会打开simulink并出现下图:

上图就是“dspprogfirhdl”模型的结构图, 图中Host Behavioral Model 是用来产生可编程FIR滤波器的系数(低通或者高通滤波器系数),Programmable FIR via Registers 是我们要生成的可编程滤波器模块,FIR Behavioral 是一个行为级的参考模块,它用来和可编程滤波器模块做结果的比对。

双击上图中的 Programmable FIR via Registers 模块或者运行如下脚本中:

systemname = [modelname ‘/Programmable FIR via Registers’];open_system(systemname);

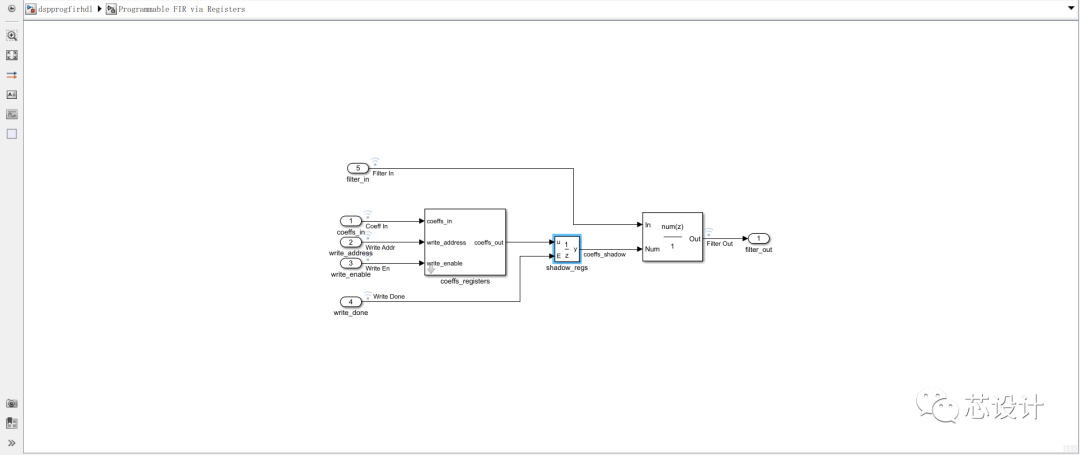

会出现下图,这是programmable FIR via Registers模块的内部结构:

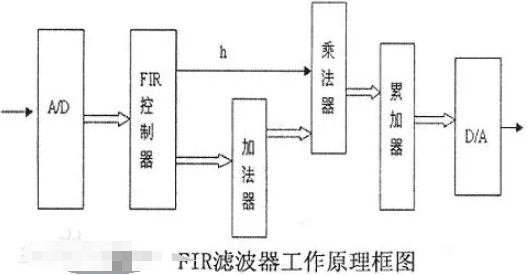

上图中coeffs_registers 是一个FIR 滤波器的系数寄存器,当‘write_enable’ 信号拉高写FIR的系数;当 ‘write_done’ 拉高,也就是写完成时, shadow registers 才会更新一次FIR的滤波器系数,该模型生成的HDL代码默认是全并行的结构实现,可根据需要改为串行流水结构。

开始执行仿真,以及查看仿真波形,执行如下代码;

sim(modelname);open_system([modelname ‘/Scope’]);

会生成如下的仿真结果:

上图中,filter_input是输入的信号,ref_out和dut output是参考模型和dut的输出结果,error是二者的结果比对情况。

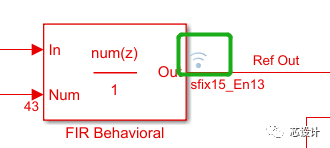

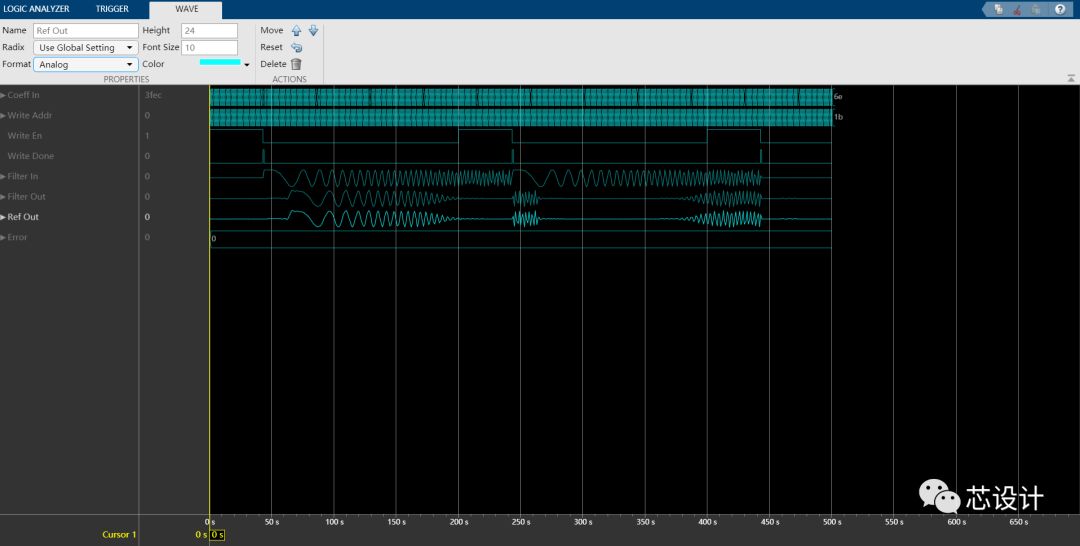

也可以使用simulink工具中的 Logic Analyzer逻辑分析仪查看波形,点击本文第一张图中的wifi符号,如下图:

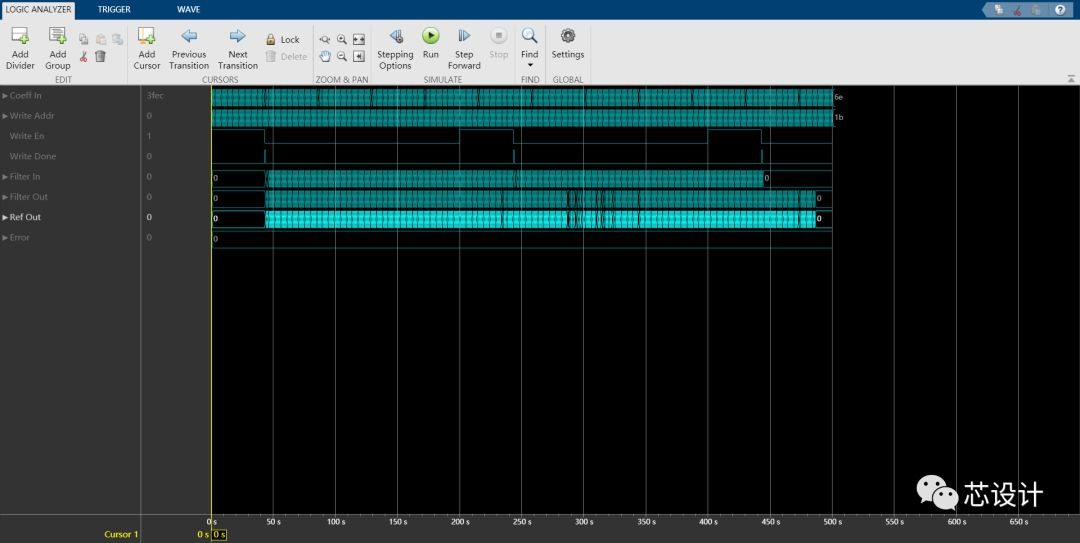

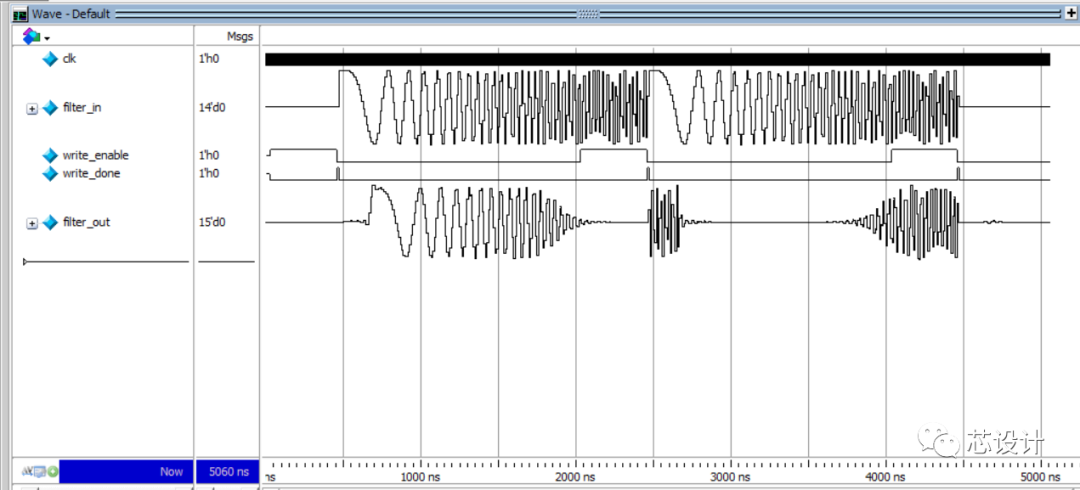

最后会在 Logic Analyzer中生成如下的波形图:

将filter滤波器输入信号和输出信号用模拟形式展开,如下图:

03

生成HDL代码

下面通过两种方式生成HDL代码

方式一(脚本):

脚本中键入如下代码,生成HDL的dut代码(默认生成.vhd的代码):

workingdir = tempname;makehdl(systemname,‘TargetDirectory’,workingdir);

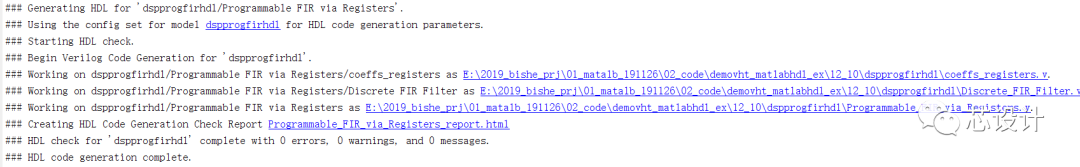

matlab命令行窗口中出现如下图,表示成功FIR滤波器的DUT代码:

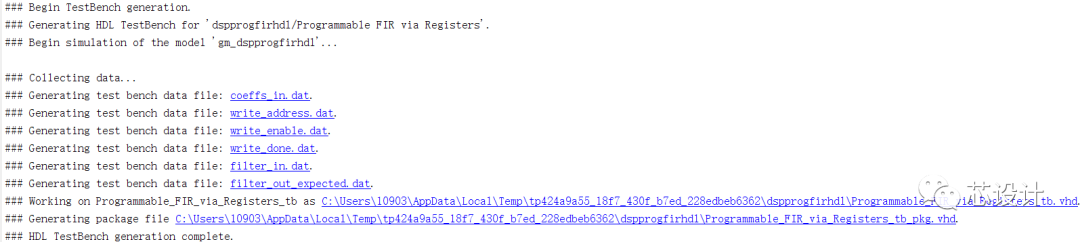

脚本中键入如下代码,生成HDL的tb代码:

makehdltb(systemname,‘TargetDirectory’,workingdir);

matlab命令行窗口中出现如下图,表示成功FIR滤波器的TB代码:

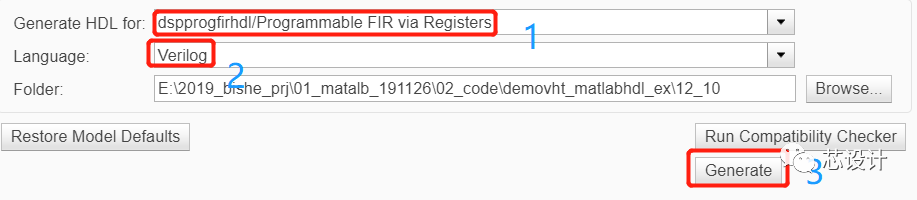

方式二(界面):

在下图中双击箭头所示部分,会出现configration配置界面(生成.v格式的代码):

出现下图,按照如下图操作1,2,3,然后点击下方generate。

matlab的命令行出现下图,表示成功生成FIR滤波器的DUT代码:

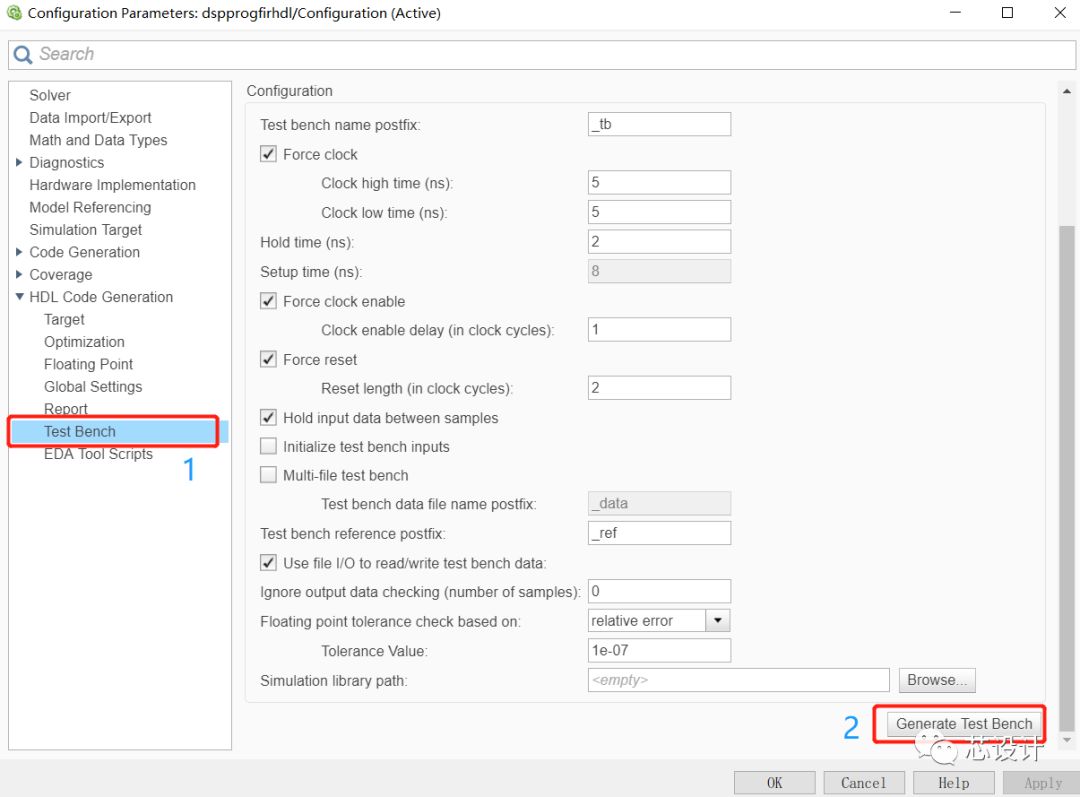

在configuration中选取testbench然后点击生成testbench即可。

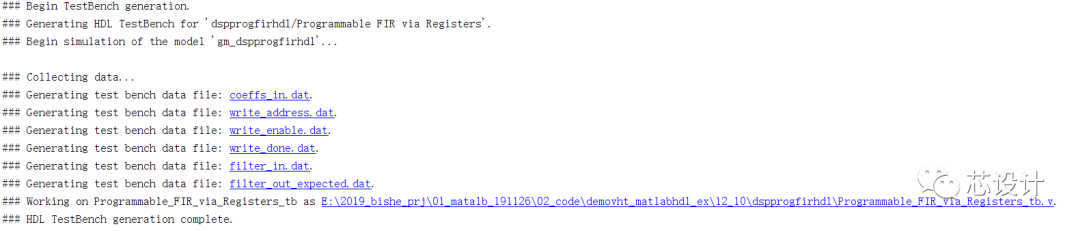

matlab的命令行出现下图,表示成功生成FIR滤波器的TB代码:

04

modelsim工具仿真

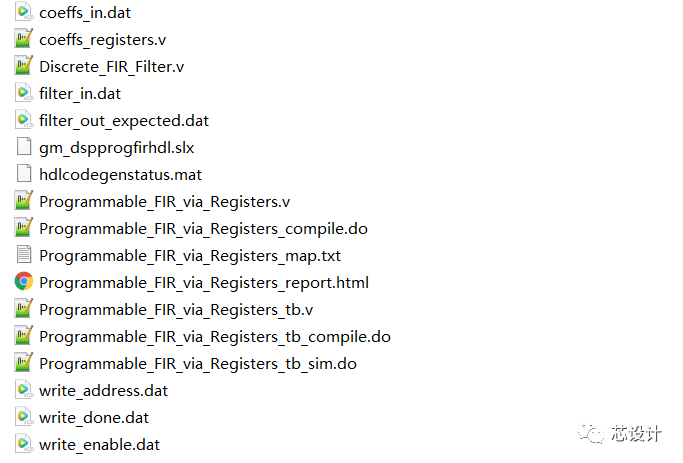

经过matlab工具生成可编程的FIR滤波器HDL代码后,在工作目录中会有如下的文件(包括:仿真用的数据.dat文件,dut和tb文件,run.do脚本):

使用modelsim仿真后的结果如下:

原文标题:matlab工具生成可编程FIR滤波器的HDL代码

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

matlab

+关注

关注

185文章

2980浏览量

230927 -

滤波器

+关注

关注

161文章

7859浏览量

178861

原文标题:matlab工具生成可编程FIR滤波器的HDL代码

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

ADS7066有可编程滤波器,请问使用该滤波器时,是否可以简化设计抗混叠滤波的截止频率?

基于FPGA实现FIR数字滤波器

如何区分IIR滤波器和FIR滤波器

iir滤波器和fir滤波器的优势和特点

基于matlab FPGA verilog的FIR滤波器设计

matlab与FPGA数字信号处理系列 Verilog 实现并行 FIR 滤波器

Vivado 使用Simulink设计FIR滤波器

Vivado经典案例:使用Simulink设计FIR滤波器

如何用matlab生成一个可编程FIR滤波器的硬件HDL代码?

如何用matlab生成一个可编程FIR滤波器的硬件HDL代码?

评论