Overview

功能与寄存器之间的关系说明

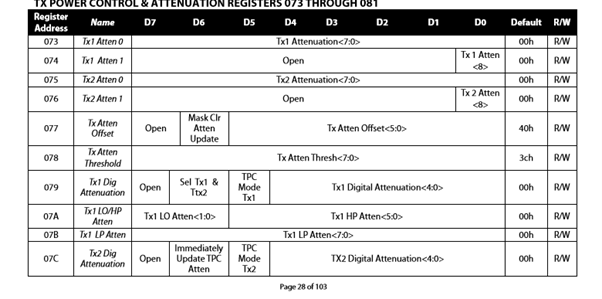

发射功率控制

TX功率由TX通路的模拟衰减值和数字衰减值控制。

模拟衰减

模拟衰减值由9bit二进制数决定,有效范围359个等级,每个等级衰减0.25dB, 模拟链路总共衰减范围是89.75dB。

TX1衰减值寄存器:0x074[D0]+0x073[D7:D0]

TX2 衰减值寄存器:0x076[D0]+0x075[D7:D0]

数字衰减

数字衰减值由寄存器0x079[D4:D0]控制,0x079[D6]=1表示TX1衰减值等于TX2,0x079[D6]=0表示TX1通道衰减生效。

接收增益控制

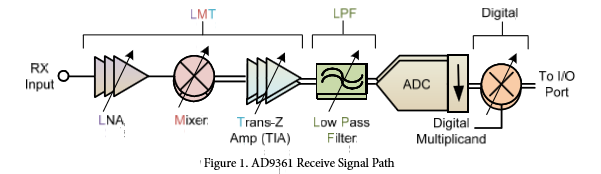

接收链路增益控制模块

AD9361接收增益的调整是由模拟增益和数字增益共同决定的,控制方式为:自动控制和手动控制,增益调整范围为90dB,数字增益最大为31dB,模拟增益最大为76dB,增益分配是由查找表决定的,查找表也有单表模式和多表模式。

低功率门限

低功率门限对两个接收通道同时有效。

门限范围:0至-63.5dBFS,控制精度0.5dBFS/LSB。

门限值寄存器地址0x114,0x114[D6:D0]=128档门限值。

低功率门限可应用于快速AGC(fast attack AGC)和手动AGC(MGC)两种模式

fast attack AGC:当检测到功率低于门限时,flag非立刻生效,只有在低功率持续一个时间段后生效。持续时间=0x11B

MGC:只要低于功率门限,flag立即生效。

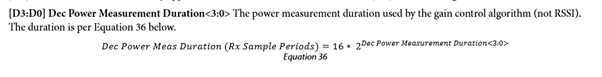

平均功率测量

平均功率测量方法使抽取一系列样本取平均,抽取样本的持续周期由寄存器设置,地址0x15c[D3:D0]

峰值功率检测时间

一般地,通过峰值超出持续时间来控制增益。通过RX的FIR滤波器时钟频率(clkRF)对信号峰值采样,峰值超出时间记录在0x0FE[D4:D0]

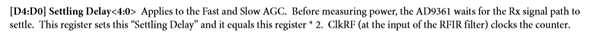

Delay设置

功率检测在RX-FIR滤波器前进行。当增益设置改变时功率测量需要维持时延,以便RX-FIR之前的模块完成准备。Delay=0x111[D4:D0]*2,时钟频率为clkRF

增益表(Gain Table)

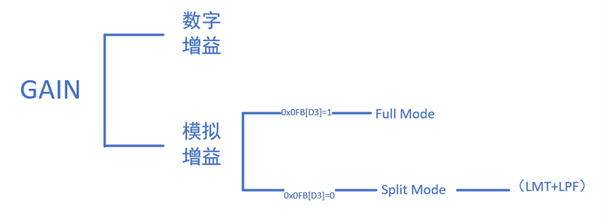

AD9361增益分为数字增益和模拟增益两部分,且两部分独立控制。

模拟增益表有两种模式:整体表(full table)和分立表(split table),两种模式选择由寄存器0x0FB[D3]控制。

Full模式指接收通道的所有增益由value来体现;

split模式将接收通道增益分为LMT(LAN、MIXER、TIA)和LPF两个独立部分。

Full table mode

在full模式下,改变总体增益值,比如由60改成59,链路中增益模块(LNA、TIA、LPF…)的参数可能都会改变。

通过SPI可读取增益值,0x2B0[D6:D0]指示RX1的增益,0x2B5[D6:D0]指示RX2的增益。

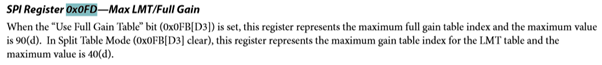

最大的full模式下的增益可在寄存器0x0FD中设置,最大值为76(十进制)。如果在split模式下该寄存器最大值是40(十进制)

Split Table Mode

Split模式下模拟总增益最大值可由寄存器0x0FD设置,最大值为40(十进制),由LMT和LPF两部分组成。

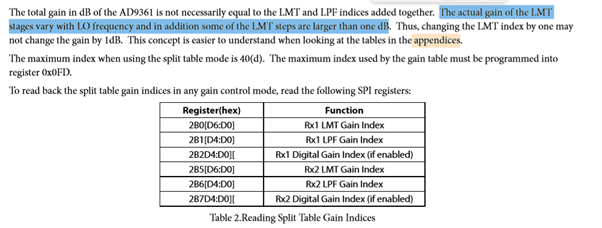

RX1的LMT增益可通过0x2B0[D6:D0]设置;LPF增益可通过0x2B1[D4:D0]设置,范围0到24(十进制)。RX2的LMT增益可通过0x2B5[D6:D0]设置;LPF增益可通过0x2B6[D4:D0]设置,范围0到24(十进制)。

注意:split模式下的增益不是简单的LMT GAIN+LPF GAIN。增加LMT增益1dB,可能不会导致整体增益增加1dB。

数字增益

数字增益使能标志位0x0FB[D2],寄存器0x100[D4:D0]可设置最大增益值,且不超过31.

由于数字增益不会恶化SNR,在链路总增益固定的情形下,可以通过增加数字增益,减小模拟增益来优化链路性能。

注意:

当寄存器0x10B[D5]=1时,无论数字增益标志位0x0FB[D2]为何值,RX1通道数字增益强制为0x10B[D4:D0];

当寄存器0x10E[D5]=1时,无论数字增益标志位0x0FB[D2]为何值,RX2通道数字增益强制为0x10E[D4:D0];

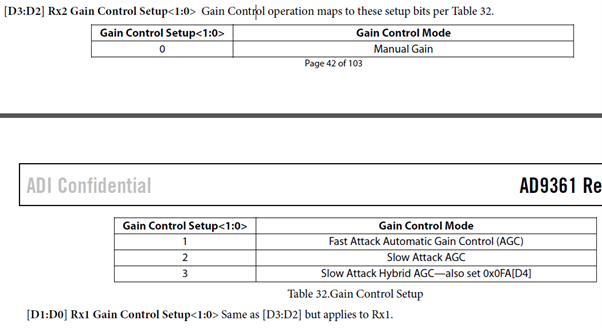

手动增益控制(MANUAL GAIN CONTROL (MGC)MODE)

MGC有两种控制方式,一种是SPI直接写入增益值,另一种是通过指针查表方式查找合适增益值。MGC模式由寄存器0x0FA后四位使能,0x0FA[D3:D2]=00,RX2进入MGC模式;0x0FA[D1:D0]=00,RX1进入MGC模式。

注意:MGC控制方法:

设置0x0FA[D3:D0],使RX1、RX2进入MGC模式;

0x0FC[D7:D5]的值是MGC增益指针查表时增加的步径,0x0FE[D7:D5]的值是MGC增益指针查表时减小的步径。

MGC方式下的full table 模式

MGC方式下的split table 模式

SPI 直接写入增益值

LMT RX1控制寄存器地址0x109,

LMT RX2=0x10C,

LPF RX1=0x10A, LPF RX2=0x10D,

Digtal RX1=0x10B, Digtal RX2=0x10E,

指针查表方式改变增益

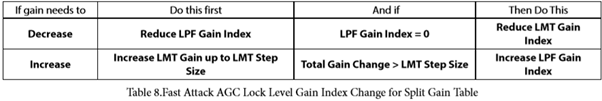

在这种模式下存在一个问题,那就是查表时首先改变哪部分(LMTLPF)的增益,这由寄存器0x0FC[D4:D3]来确定。

如果0x0FC[D3]=0,则0x0FC[D4]=1改变LMT增益,0x0FC[D4]=0改变LPF增益。

如果0x0FC[D3]=1,则0x0FC[D4]状态忽略,由峰值功率检测机制(AD9361 peak detectors)决定改变LMT还是LPF增益。在这种模式下由寄存器0x11A将 LMT增益分为Upper和Lower两部分。

AGC 慢速控制(Slow attack)

应用场景:在FDD场景下。

设置方法:

0x0FA[D4]=0,确保不进入“Slow Attack Hybrid Mode”

RX1:0x0FA[D3:D2]=10; RX2:0x0FA[D1:D0]=10

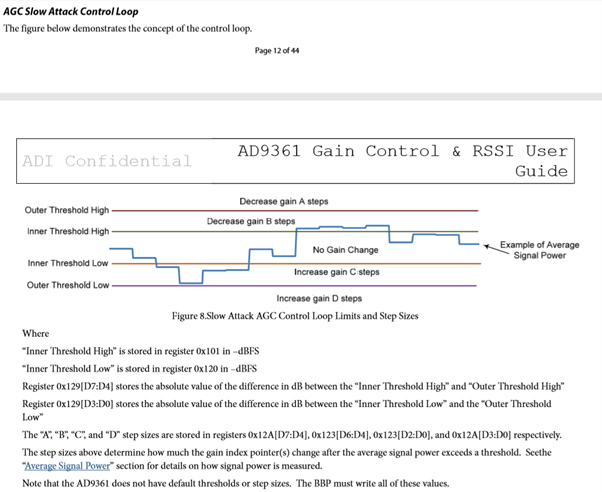

AGC Slow attack 控制环

设置增益更新时间

在0x124和0x125中设置更新时间,并以RFclk时钟计数,当达到0x124的value时,链路增益值更新。

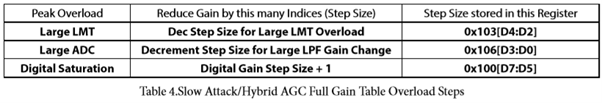

Slow attack AGC模式下的full gain table

Slow 模式功率过载时,单增益表控制增益方式如下:

Slow attack AGC模式下的split gain table

如果gain在LPF表中变化,步径=0x106[D3:D0],如果gain在LMT表中变化,步径=0x103[D4:D2]

AGC混合控制模式

该模式是slow 模式,但是增益更新不受时间限制,只要BBP 拉高 CTRL_IN2 信号,则增益表更新。

设置方法:

0x0FA[D4]=1

RX2使能0x0FA[D3:D2]=11;RX1使能0x0FA[D1:D0]=11

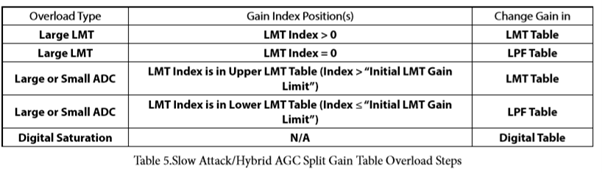

AGC快速控制模式(fast attack mode)

AGC fast attack mode对过载的响应非常快,这样当信号的数据部分到达时,AGC就能稳定到最佳增益指标。

AGC是通过状态机实现增益锁定,如果状态机几个状态完成还没有锁定增益,则返回状态机复位状态。状态机如下图:

STATE0

复位状态,当9361没有进入RX状态时,状态机停留在这一状态。

STATE1

进入RX状态,状态机做一个时延使进入gain侦查准备。时延值寄存器地址0x022

检测峰值功率是否过载,检测时间值=0x117[D4:D0],如果不过载则进入状态2

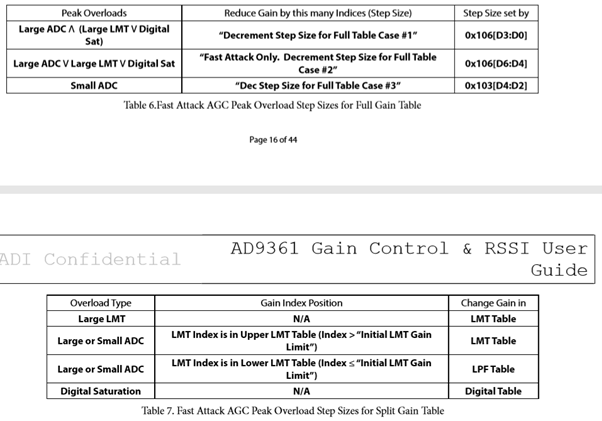

检测到峰值功率过载,调节机制如下:

STATE2

在HB1输出处测量平均功率值,打开各功率过载检测器,一旦发现过载则返回状态1;

平均功率如果低于“低功率门限值”,启动增益增加机制。完成增益增加后返回状态1;

平均功率值与0x101比较,然后调整增益使之与平均功率匹配。链路最大增益由0x118确定。

在 full table模式下,增益调整直接增益参数。Flit模式下,如果0x111[D6]=1,执行如下操作:

如果0x111[D6]=0,则只有LPF的增益值改变使之匹配平均功率值

STATE3

状态机进入增益锁定状态,功率过载检测机制继续进行。如果功率过载或者过低,增益进入非锁定状态。功率过低响应机制和state2一样。

STATE4

状态3检测到功率过载进入状态4,状态4下增益调整可以在单表(full table)和分表(split table)模式下进行。调整步径发生改变,由寄存器0x112[D7:D6],0x113[D7:D5]确定。

STATE5

在此状态下,增益是锁定状态。平均功率检测周期发生变化,由寄存器0x109[D7],0x10A[D7:D5]控制功率检测周期。

未完待续

太难了。。。原创不易,摸索更不易,如果对您有帮助,欢迎点赞,在看,转发也是对作者的支持与厚爱,感谢!

原文标题:深度解析,AD9361增益控制详解

文章出处:【微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

寄存器

+关注

关注

31文章

5394浏览量

122167 -

AD9361

+关注

关注

8文章

35浏览量

37425

原文标题:深度解析,AD9361增益控制详解

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

接口的控制与状态寄存器什么作用

ARM处理器的寄存器组织及功能

ARM寄存器的分类及功能

每个段与寄存器之间有何对应的要求

寄存器根据功能的不同分为哪两种

寄存器是什么意思?寄存器是如何构成的?

功能与寄存器之间的关系说明

功能与寄存器之间的关系说明

评论