作者:龚广伟;韩方景;陈凡国;乔佩 来源:电子产品世界

数字信号处理模块是接收机系统的核心部分,系统要求数字信号处理模块能实时处理ADC变换后的数字信号,并用软件的方法来实现大量的无线电功能,这些功能包括:多通道校准、编解码、调制解调、滤波、同步、盲均衡、检测、数据加密、传输加密纠错、跳扩频及解扩和解跳、通信环境评估、信道选择等,而单个DSP根本无法完成这些功能。目前可用的一些高速DSP的性能最快的也不超过5GIPS ,与实际需求相差巨大。这种处理资源的匮乏,被称之为DSP 瓶颈[1],因此我们在本系统中主要采用Xilinx的FPGA芯片实现后端数字信号处理。

时钟同步

FPGA硬件设计中,时钟是整个设计最重要、最特殊的信号,异步信号输入总是无法满足数据的建立保持时间,所以需要把所有异步输入都先进行同步化。时钟同步的重要性如下:

● 系统内大部分器件的动作都是在时钟的跳变沿上进行,这就要求时钟信号时延差要非常小,否则就可能造成时序逻辑状态出错;

● 时钟信号通常是系统中频率最高的信号;

● 时钟信号通常是负载最重的信号,所以要合理分配负载。出于这样的考虑在FPGA这类可编程器件内部一般都设有数量不等的专门用于系统时钟驱动的全局时钟网络。

对于一个设计项目来说,全局时钟(或同步时钟)是最简单和最可预测的时钟。只要可能就应尽量在设计项目中采用全局时钟。FPGA都具有专门的全局时钟引脚,它直接连到器件中的每一个寄存器。这种全局时钟提供器件中最短的时钟到输出的延时。

但在许多应用中会出现两个或两个以上非同源时钟,系统设计将面临复杂的时间问题,数据的建立和保持时间很难得到保证。对于需要多时钟的时序电路,最好将所有非同源时钟同步化,即选用一个频率是它们的时钟频率公倍数的高频主时钟。各个功能模块要使用统一的复位电路。在使用带时钟的触发器、计数器等有复位端的库器件时,一般应尽量使用有同步复位的器件。注意复位时应保证各个器件都能复位,以避免某些寄存器的初始状态不确定而引起系统工作不可靠。

基于以上分析,在本设计中,将64M的高频时钟作为系统时钟,输入到所有触发器的时钟端。时钟使能信号Clk_en将控制所有触发器的使能端。即原来接8M时钟的触发器,接64M时钟,同时Clk_en将控制该触发器使能;原接64M时钟的触发器,还接64M时钟,Clk_en也将控制该触发器使能。这样,就可以将任何非同源时钟同步化。

多通道校准同步算法

下面以M元阵为例来说明多通道校准过程。接收机开机时,先将选择开关S切换到位置2(见图1),进入校准状态。注入信号s(t)经功分器进入各阵元通道,阵元通道输出为基带数字信号 xm(t)。将第一条通道作为参考通道,第一条通道的输出延时τ后作为参考信号,与其他阵元通道的输出一起送入相应的自适应校正滤波器。自适应校正滤波器将会对阵元通道的传输特性进行补偿,使各个阵元通道的传输特性趋近参考通道。这里采用LMS自适应算法,待自适应算法收敛后,稳态权矢量将作为自适应校正滤波器的系数固定下来,至此阵元通道的校正结束。最后,将选择开关S切换到位置1就可进入正常通信状态。

按图1所示的模型可知,用L阶横向FIR滤波器模拟通道响应,通过在滤波器的系数上加上小的幅度扰动δ和相位扰动Φ来模拟通道间的失配,这样可得第m个待校准通道模拟滤波器的传输函数为:

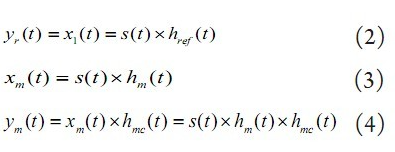

设注入的信号是s(t),href(t)和hm(t)分别为参考通道和待校准的第m条通道的冲激响应,hmc(t)为第m条通道的校准滤波器的冲激响应,那么参考通道的输出(暂不考虑延时τ)、第m条待校准通道校准前的输出和校准后的输出分别为:

自适应滤波器采用MMSE准则,其中,准则选择是否合理决定了天线阵暂态响应的速度和实现电路的复杂度。可以证明,这个准则的结果可以分解为一个相同的线性矩阵滤波器和一个不同的标量处理器的积,且都收敛于最优维纳解。因此,当自适应滤波器收敛到稳态即最优解后,最佳权值应该为:

从而通道特性得到了校准。

本文中的多通道校准算法是在FPGA中实现的,选择FPGA而不选择DSP器件的原因是FPGA的引脚众多且可以定制,这样就可以在相对较低的工作频率下做到很高的数据吞吐率,而这是DSP难以做到的。

FPGA实现

在本设计中应该综合考虑各方面因素,选择一种最佳模块结构和模块规模。本设计中的结构化层次是由一个顶层模块和若干个子模块组成,每个子模块根据需要再包含自己的子模块,以此类推,共5层,如图2所示。

本设计中,整个通道失配校准模块共需要90个乘法器。这些乘法器如果采用FPGA的逻辑资源直接构建,不仅难以保证理想的运算速度,而且硬件开销非常巨大。而FPGA芯片内部已经集成了18×18位的硬件乘法器模块,其速度快,实现简单,能有效节省FPGA的逻辑资源。由于系统设计时选用的FPGA芯片型号为Xilinx公司的xc2v8000ff1152-5,它集成了几百个硬件乘法器,因此可以全部使用硬件乘法器来完成相应的乘法运算。

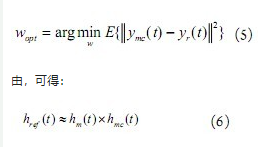

采用VHDL语言编写实现程序,开发环境为ISE 8.2i,综合工具为Synplify Pro v8.1,仿真工具为ModelSim SE 6.3f。图3所示的是程序经Synplify Pro v8.1综合后得到的LMS自适应校正滤波器顶层模块RTL视图。RTL视图即寄存器传输级视图,该图高度抽象为模块化结构,它是在对源代码编译后再现设计的寄存器传输级原理图。

所有算法模块均在全局使能信号clk_en不同状态的控制下进行工作,从而使算法运行达到8M周期,直至找到最佳权值,最终完成多通道校准的任务,实现多个通道的幅相一致性。

表1为多通道校准算法的FPGA资源占用列表,从系统资源占用情况可以看出:多通道校准算法FPGA实现过程中,如果再加上前后端处理程序一起编译,则输入输出端口将减少,资源占用也将减少,并不影响系统实现。其它各种资源占用量都较少,完全符合FPGA设计要求。

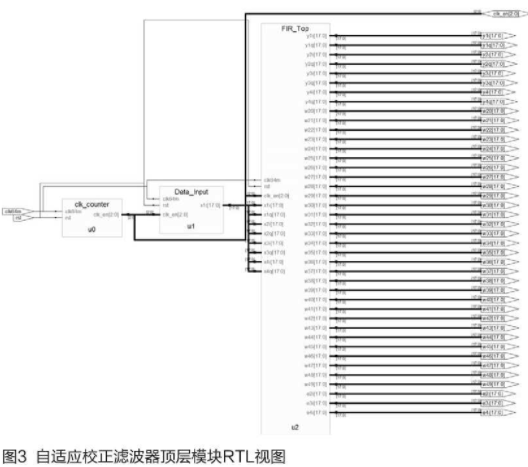

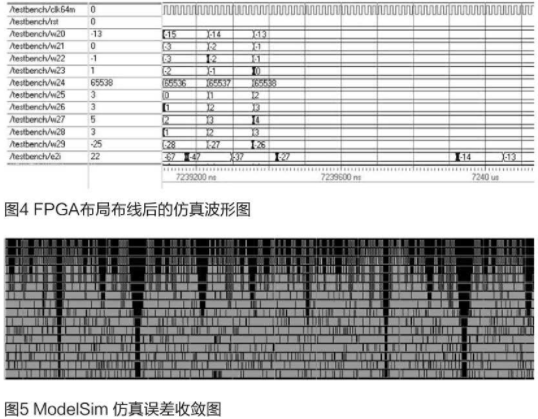

FPGA布局布线后的仿真波形如图4、图5所示。

从仿真结果(图4,图5)和ISE 8.2i的综合报告可知,该校正模块的最高时钟频率达到102.5MHz。

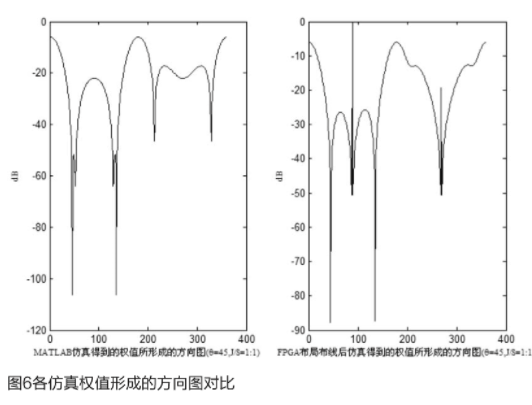

最后,由MATLAB仿真和FPGA布局布线后仿真得到的权值,经过MATLAB仿真形成新的方向图,如图6所示,可以看出,两种方向图基本一致。因此,基于FPGA的多通道校准同步算法的实现完全符合系统要求。

结语

由于数据时钟的同步是FPGA 芯片设计实现的一个常见问题,也是一个重点和难点,很多设计不稳定都是源于数据时钟的同步有问题。而本文提出了解决这一问题的时钟同步方法,并在硬件上很好地实现了多通道校准算法,极大提高了系统稳定性。

责任编辑:gt

-

FPGA

+关注

关注

1635文章

21837浏览量

608321 -

芯片

+关注

关注

459文章

51566浏览量

429752 -

触发器

+关注

关注

14文章

2024浏览量

61489

发布评论请先 登录

相关推荐

基于FPGA的帧同步系统设计方案

FPGA时钟设计方案

基于FPGA的时钟恢复以及系统同步方案设计

基于FPGA 的OFDM 宽带数据通信同步系统设计与实现

嵌入式同步时钟系统的设计方案

采用FPGA实现同步、帧同步系统的设计

低成本的采用FPGA实现SDH设备时钟芯片技术

基于FPGA芯片实现数据时钟同步设计方案

基于FPGA芯片实现数据时钟同步设计方案

评论