同步控制信号

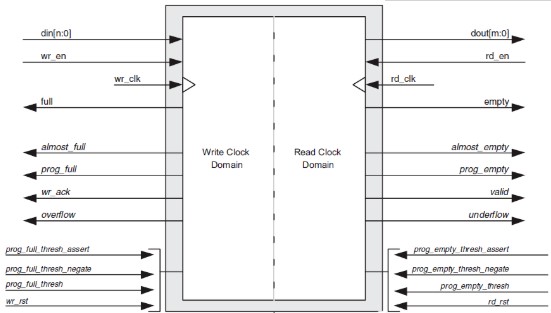

对于读/写时钟相互独立的FIFO(读/写时钟独立意味着这两个时钟是异步的,例如来自于不同的MMCM),要确保相应的控制信号只在与之对应的时钟域内被使用。如下图所示,除了rst对整个FIFO进行异步复位外,其余信号都与各自的时钟同步。例如:写使能wr_en、写数据din都与写时钟wr_clk同步;读使能rd_en、读数据dout都与读时钟rd_clk同步。和“满”相关的状态信号如full/almost_full等都与wr_clk同步;和“空”相关的状态信号如empty/almost_empty等都与rd_clk同步。

复位信号 对于读/写时钟独立的FIFO,FIFO Generator提供了复位信号,用于对所有的状态输出信号进行复位,如下图所示。这里复位信号是可选的。如果下图选项1不勾选,那么选项2和选项3则不可见,此时FIFO没有复位信号。如果勾选1,此时选项2和选项3可见,且默认均被勾选,这意味着rst尽管是异步的,但在使用时会被wr_clk和rd_clk先同步到各自的时钟域。如果勾选1,但不勾选2,此时读/写时钟域会分别有各自的复位信号wr_rst和rd_rst。当wr_rst有效时(高有效),写时钟域处于复位状态;当rd_rst有效时,读时钟域处于复位状态。由此可见,对于读/写时钟独立的FIFO,异步复位rst和同步wr_rst/rd_rst是可选的。这意味着FIFO可以没有复位信号,也可以只用一个异步复位信号rst,或者用同步复位wr_rst/rd_rst。

原文标题:你的FIFO为什么不能正常工作

文章出处:【微信公众号:Lauren的FPGA】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

fifo

+关注

关注

3文章

388浏览量

43657 -

同步控制

+关注

关注

0文章

35浏览量

12418

原文标题:你的FIFO为什么不能正常工作

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

为什么有时候FIF不能正常工作?

为什么有时候FIF不能正常工作?

评论