每一个做数字逻辑的都绕不开跨时钟域处理,谈一谈SpinalHDL里用于跨时钟域处理的一些手段方法。

打拍处理 跨时钟域信号的打拍处理往往用于单比特信号或类似于格林码这种信号的跨时钟域处理。其逻辑电路很简单。SpinalHDL提供了BufferCC用于实现这种跨时钟域打拍处理方式:

BufferCC(input: T, init: T = null, bufferDepth: Int = 2)

bufferDepth可用于指定打拍级数。input信号的时钟域为源时钟域,BUfferCC调用的地方的时钟域为目的时钟域。 在日常的电路设计里,计数器是常见的DFX信号,有些情况下需要将一个时钟域的DFX信号转换到另一个时钟域进行HPI读取,这种情况也可以通过打拍进行处理,不过前提是需转换成格林码,如此在源时钟域和目的时钟域需分别做一次转换与反转换。但如果计数器采用格林码进行计数则可以少进行一次转换。SpinalHDL有提供一个GrayCounter方法用于生成格林码计数器:

GrayCounter(width: Int, enable: Bool)

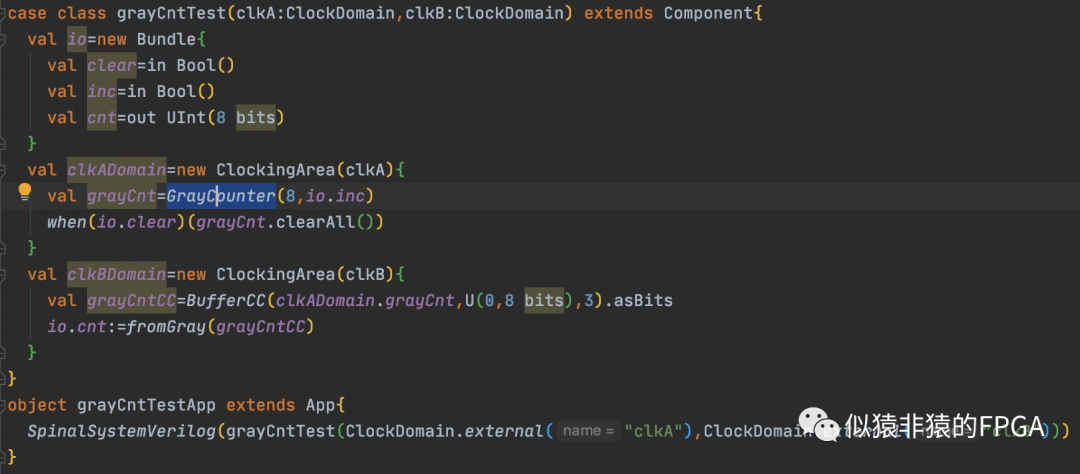

提供一个小demo,GtayCounter+BufferCC:

这里GrayCounter在时钟域clkA中实现,通过BufferCC将其跨时钟域至clkB,bufferDepth为3.Tips:BufferCC的第二个参数init数据类型是T,而T《:Data,即意味着init数据类型为“硬件”数据类型,因而上面init赋值需为U(0,8 bits)而不能直接写0》》脉冲信号处理 脉冲信号的跨时钟域处理,SpinalHDL提供了PulseCCByToggle方法:

PulseCCByToggle(input: Bool,clockIn: ClockDomain,clockOut: ClockDomain): Bool

握手处理

对于吞吐要求不是特别高的场合,跨时钟域信号采用握手形式 进行处理也是一种不错的选择。SpinalHDL有两个抽象类型个人一直很喜欢:Stream,Flow。这两种形式基本囊括了所有的信号交互行为,其也可以说是SpinalHDL lib库的基石。针对跨时钟域的握手处理,SpinalHDL有一个StreamCCByToggle可以使用:

StreamCCByToggle(input: Stream[T], inputClock: ClockDomain, outputClock: ClockDomain): Stream[T]

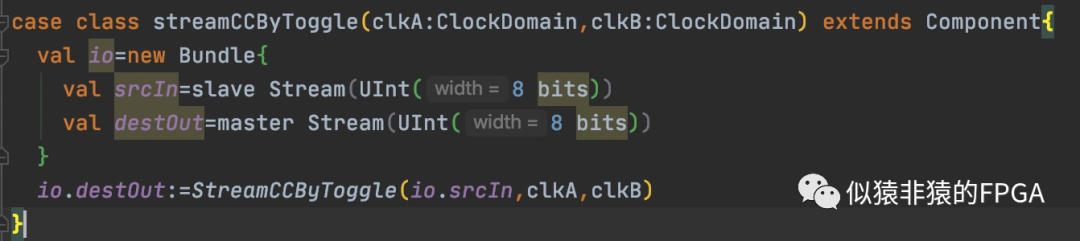

其输入参数包含源时钟域信号,源时钟域,目的时钟域,其返回一个目的时钟域的Stream信号:

这里srcIn隶属于时钟域clkA,destOut隶属于时钟域clkB。 除了StreamCCByToggle,SpinalHDL里还有一个FlowCCByToggle。由于Flow类型没有反压,因而从低时钟域向高时钟域进行传输则没什么问题,但从高时钟域向低时钟域进行转换则存在丢失数据的风险。》》FIFO跨时钟域缓存 对于高吞吐的多比特信号跨时钟域处理,则往往采用FIFO的形式进行处理。在SpinalHDL里则有StreamFifoCC供使用:

val myFifo = StreamFifoCC( dataType = Bits(8 bits), depth = 128, pushClock = clockA, popClock = clockB)myFifo.io.push 《《 streamAmyFifo.io.pop 》》 streamB

编辑:lyn

-

电路设计

+关注

关注

6678文章

2466浏览量

205634 -

计数器

+关注

关注

32文章

2276浏览量

95106 -

时钟域

+关注

关注

0文章

52浏览量

9586

原文标题:跨时钟域那点事儿

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

TSP研究:车内网联服务向跨域融合、全场景融合、舱驾融合方向拓展

混合域示波器的原理和应用

关于\"OPA615\"的SOTA的跨导大小的疑问求解

OPA376能用来做跨阻抗放大电路吗?

极限失控的大模型使电力系统面临的跨域攻击风险及应对措施

单芯片运行六个操作系统,芯驰科技交卷跨域融合

航盛与高通发布全新一代墨子舱驾跨域融合平台

利用LWIP实现的Web server,如何修改响应报文中HTTP header里面的Access-Control-Allow-Origin的值?

黑芝麻智能与斑马智行达成单芯片跨域融合平台项目合作

介绍一个IC设计错误案例:可读debug寄存器错误跨时钟

关于跨时钟域的详细解答

关于跨时钟域的详细解答

评论