现场可编程逻辑阵列(FPGA)资源丰富,结构灵活,近年来发展迅猛。针对其特点,本文设计了基于FPGA的增量式光电编码器的接口电路,实现了对增量式编码器脉冲信号的倍频、鉴相及计数等功能。最后仿真验证了设计的可行性。为进一步实现高精度的位置伺服控制提供基础。

光电编码器是目前伺服系统中应用最多的传感器,它通过光电转换将输出轴上的机械几何位移量转换成脉冲或数字量。光电编码器与电机相连,当电机转动时,带动码盘旋转,便发出转速或转角信号。

目前光电编码器已经普遍应用在雷达、光电经纬仪、地面指挥仪、机器人、数控机床和高精度闭环调速系统等诸多领域。根据其刻度方法及信号输出形式,可分为增量式、绝对式以及混合式3种。

绝对型编码器在转轴的每一个位置均可读出唯一对应的数字码,抗干扰、无需掉电记忆,但其制造工艺复杂、价格是增量型编码器的几倍到几十倍。因此在实际的应用中,增量型编码器占据了统治地位。

增量式编码器工作原理

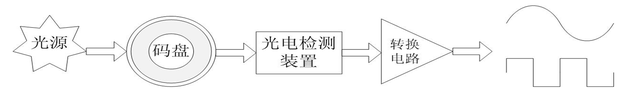

增量式编码器由光源、码盘、检测光栅、光电检测器件和光电转换电路组成,其原理如图1所示。

图1 增量式编码器原理图

当码盘随同被测转轴转动时,检测光栅保持不动。光线穿过码盘和检测光栅的缝隙照射在光电检测器件上,光电检测器件即会输出相位相差900电度角的近似于正弦波的两组差分电信号,这两组差分信号再经脉冲整形转换为普通的单端电平信号,最后对两个单端电平信号进行倍频、鉴相和计数等操作,以得到码盘旋转的方向和位置。

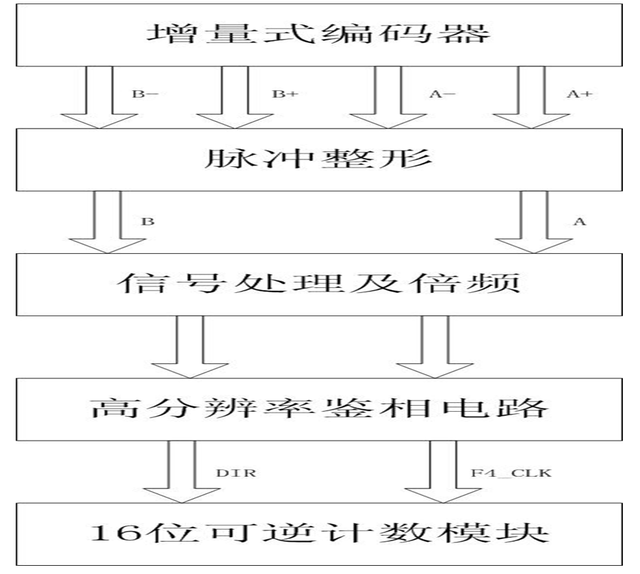

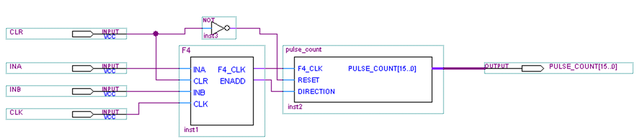

本文旨在解决增量编码器倍频、鉴相、计数的问题,充分利用FPGA丰富的逻辑模块和IO模块,设计了一种简单的接口电路,并行输出结果以供进一步操作,如图2所示。

图2 编码信号处理模块

倍频、鉴相、计数原理分析

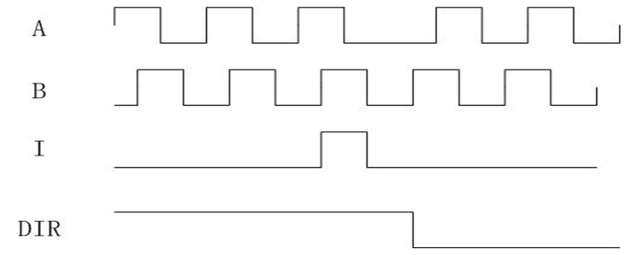

编码器码盘和检测光栅有两组对应的等间距透光缝隙,相互错开1/4节距,用于在旋转过程中对光电发送及接收装置产生通断变化,使得光电检测器件输出相位上相差90o的信号A、B。根据A和B的相位关系可判断出码盘的旋转方向。

当A相位超前B90o时,DIR(方向信号)为高电平,电机正转;当A滞后B90o时,DIR(方向信号)为低电平,电机反转。码盘信号经过计数器计数后得出码盘旋转的角度才能转换为位置信息,计数器加减以方向信号为依据。

与此同时,码盘上还有一个开孔用来判断码盘的绝对位置,即码盘每旋转一周将产生一个索引信号I,有的也用I作为对位、清零信号。如图3所示。

图3 编码器输出信号

编码器每旋转一周,A相和B相所输出的脉冲数相同,脉冲数决定了编码器的精度。

由图3可知,在一个编码脉冲输出周期中,A和B信号共产生了4个跳变沿。捕捉每个跳变并且进行计数,即:当A为高电平时,B在上升沿则加1,下降沿则减1;A为低电平时,B在下降沿则减l,上升沿则加l;B为高电平时,A在上升沿则减1,下降沿则加l;在B为低电平时,A在上升沿则加1,下降沿则减l。

如此在每个周期内,码盘正转时计数4次,反转时也计数4次,使计数脉冲数量增加了4倍。若一个编码脉冲信号量化误差为φ,则四倍频后的量化误差降为φ/4,其角位移的测量精度提高了4倍,同时光电码盘的分辨率也提高了4倍。

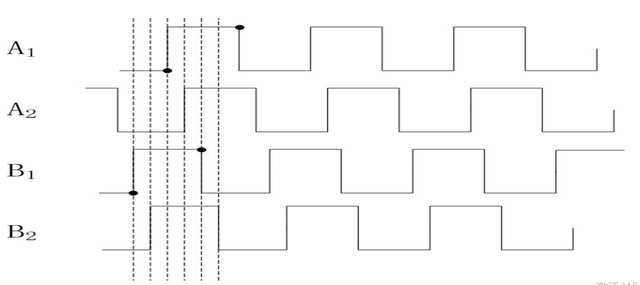

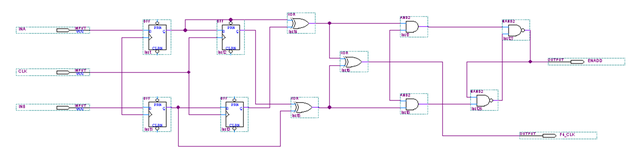

信号四倍频设计的关键在于捕捉A、B信号的上升沿和下降沿。本设计采用数字型电路即D触发器作为延迟环节来检测边沿的变化,A、B相倍频脉冲宽度和延时时间均由时钟(外部有源晶振提供)控制,倍频后的脉冲宽度一致,可以有效地克服传统RC微分型或积分型边沿检测电路的不足。

A、B信号经D触发器后的信号分别记为A1、B1。将A1、B1作为倍频的原始信号,将消除A、B信号中尖脉冲带来的影响,提高了系统的抗干扰性能。A1、B1再经过一个D触发器,延时一个时钟周期,将产生A2、B2信号。

即A2、B2分别滞后A1、B1一个时钟周期,且A1、A2的相位分别滞后B1、B290o(假定此时电机反转,B1超前A190o),为了实现预期目的,需要能够完全捕捉到一个周期内脉冲的上升沿和下降沿,即图4的圆黑点。

从图4中虚线所示的状态可知,A1和A2,B1和B2两组信号里都有一组不同的电平状态,故采用3个异或门以求得信号的4倍频信号F4_CLK。与此同时,采用两个与非门来求得方向信号。

图4 A、B信号经D触发器后的信号图

光电编码器线数为1024,四倍频后旋转一圈产生4096个脉冲,其精度为0.0879o。为满足精度要求,本设计采用的是16位可逆计数器,计数范围为-65536~65535,利用Altera公司的设计软件自带的LPM(宏功能模块)模块实现该计数模块。

接口电路的设计与实现

本设计使用的软件是Altera公司的Quartus II,选用的芯片是CycloneⅢ的EP3C16Q240。该芯片有15408个逻辑单元,56个乘法器,4个锁相环,20个全局时钟网络,存储器容量为504Kbit,最高工频率可为437.5MHz,输入输出电压3.3V[8],如此强大的资源足以实现设计预期的功能。

1 子模块的原理图设计

FPGA具有动态可系统重构和静态可重复编程的特性,使得可以像软件一样通过编程来修改硬件的功能。我们可以通过原理图输入或者HDL(硬件描述语言)来设计实现一个数字系统。根据上一节原理的介绍,生成倍频、鉴相、计数模块的顶层文件原理图,如图5所示。

图5 顶层原理图

其中,输入为正交编码信号A、B,输出为16位计数结果。该顶层原理图分为两部分,一个是倍频、鉴相模块,如图6所示;一个是使用自带的宏功能模块实现的计数模块。编码信号经倍频、鉴相后产生四倍频信号F4_CLK、方向信号ENADD,再经过pluse_count实现16位可逆计数功能。当ENADD为高电平即码盘正转时,实现加法计数;当ENADD为低电平即码盘反转时,实现减法计数。

图6 倍频、鉴相原理图

2 编译及下载

在Quartus II中依次进行如下操作:新建工程、选择目标芯片、绘制原理图、管脚分配、芯片参数及配置选项设置,即可对设计文件进行编译。

编译完成后将在工程文件夹下将生成后缀名为sof和pof的两个下载文件,这两个文件的区别在于:前者是通过JTAG口下载到FPGA芯片中(配置FPGA芯片),直接运行程序,而掉电后程序消失;后者是通过AS口下载到配置芯片中,上电后将自动完成配置,运行程序。

前者下载的速度快,一般用于FPGA的调试过程;而后者由于是烧写EPCS配置芯片(实际上是串行FLASH),速度较慢,一般用于开发后期的程序固化。本次设计也是遵循调试阶段采用JTAG模式烧写下载,待程序确定后采用AS模式烧写下载。

波形仿真及分析

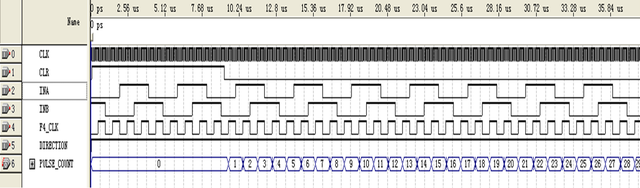

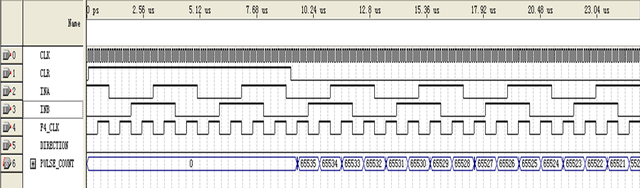

编译通过后,我们使用Quartus II自带的仿真器进行功能仿真以验证设计的逻辑是否正确。在建立矢量源文件时,首先设置编码信号A超前B 90o得到仿真结果如图7所示;然后设置编码信号B超前A 90o得到仿真结果如图8所示。

从图7、图8中可以看出,当信号A超前B 90o即电机正转时,方向信号为高电平,实现四倍频且一个周期内加法计数4次;反之,当信号B超前A 90o即电机反转时,方向信号为低电平,同样实现四倍频且一个周期内减法计数4次。由此可知,仿真结果与理论分析完全一致,本接口电路逻辑正确,具有实际意义。

在实际调试阶段中,连接好编码器和电路板,通过QuartusII的Signaltap II来捕捉和显示实时信号,所得的结果与预期也是一致的,从而进一步验证了设计的可靠性。

图7 信号A超前B 90o仿真结果

图8 信号B超前A 90o仿真结果

小结

基于FPGA的增量式编码器的接口设计实现了对编码信号数据的采集和处理,克服了使用ASIC(专用集成电路)对数据进行处理而产生的编译复杂、通用性差等缺点。该接口电路具有适用性好、集成度高、抗干扰性强、运行可靠、数据处理快等优点,适用于各种需要使用增量式编码器测量位置和速度的场合。

编辑:lyn

-

FPGA

+关注

关注

1641文章

21912浏览量

611713 -

接口电路

+关注

关注

8文章

468浏览量

57436 -

光电编码器

+关注

关注

7文章

115浏览量

31667

发布评论请先 登录

相关推荐

模块式编码器原理 精度与分辨率

基于FPGA的增量式光电编码器的接口电路设计与实现浅析

基于FPGA的增量式光电编码器的接口电路设计与实现浅析

评论