引言

软件无线电是一种基于宽带A/D、高速DSP芯片、以软件为核心的崭新体系结构。其基本思想是将宽带A/D尽可能靠近射频天线,以便将接收到的模拟信号尽可能早地数字化,尽量通过软件来实现接收机的各种功能。通过运行不同的算法,实时地配置信号,以提供多模式、多频段的功能。与传统的模拟方式相比,软件无线电具有灵活性、适应性和开放性等特点,被誉为无线电领域的又一次革命。目前软件无线电技术已在通信系统中得到广泛应用。

全数字化接收机是软件无线电中的一个重要基础,其硬件平台可以用可编程的通用DSP或者可重构的专用DSP来实现。目前,由于硬件水平的限制,直接射频数字化还有一定困难。一般是先模拟下变频至合适的中频,在中频直接数字化,然后经数字下变频至基带。模拟下变频完成初步的频率选择,中频采样后经数字下变频完成第二次频率变换。其中,数字下变频的设计是关键技术,它的实现方式有两种,一种是在FPGA内设计实现,另一种是采用专用的数字下变频芯片来实现。本文将对INTERSIL公司生产的四通道数字下变频器ISL5216的功能特点进行详细介绍,并结合自行研制的中频通用接收平台,重点介绍利用其实现数字信号的抽取滤波以降低信号速率的设计要点,并给出了设计实例。

1 ISL5216简介

1.1 ISL5216的功能特点

ISL5216是INTERSIL公司生产的可编程四通道数字下变频器(PDC),它的基本功能是从输入的宽带信号中提取窄带信号,并将其下变频为数字基带信号,以便后续DSP处理。

该芯片的主要特点如下:

一 输入信号速率达95MSPS;

一 具有四个独立可编程的下变频器通道;

一 具有四个16-bit定点或17-bit浮点模式的并行输入通道;

一 带有32-bit可编程载频数控振荡器(NCO),无杂散动态范围(SFDR)大于115dB;

一 具有110dB的带外衰减;

一 抽取因子范围为4~65 536;

一 含有24-bit内部数据通道;

一 内含增益容限可达96dB的数字AGC;

一 具有多种滤波器功能(其中包括:1到5级CIC滤波器、半带抽取与插入FIR滤波器、可编程FIR滤波器和重采样FIR滤波器);

一 可通过串联滤波获得附加带宽;

一 具有四个独立的串行输出通道;

一 采用2.5V内核电压、3.3V外围电压工作。

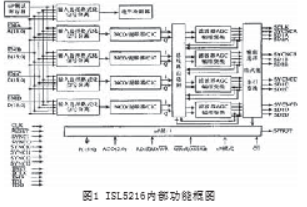

1.2 ISL5216的内部结构及工作机理

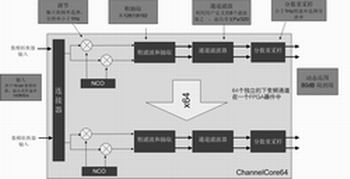

ISL5216具有很大的动态范围和灵活性。在四个通道中,每一个通道都是由前端的载频数控振荡器(NCO)、数字混频器和级联积分梳状滤波器CIC以及后端的FIR滤波器、AGC和直角坐标到极坐标转换器构成。四个通道中的每个通道的参数都可以独立通过微处理器进行编程。图1是ISL5216的内部功能框图。A(15∶0)、B(15∶0)、C(15∶0)和D(15∶0)分别为四条并行的数据输入总线。SDXA、SDXB、SDXC和SDXD为四对串行数据输出线。每一个输入都可以连接到任意一个或所有的内部信号处理通道中去,每一个通道的输出都可以接到任何一个串行输出端。如果多路通道是同步的,那么这些通道可以复用到一个共同的输出端。四个通道共用同一个输入时钟和同一个串行输出时钟。但是输出信号速率既可以是同步的也可以是异步的。位于前端和后端之间的总线多路转换器可以为后端串联的滤波器提供灵活的路由,或者为多相滤波提供从一个前端到多个后端的路由。电平检测器把每一条并行数据输入总线上的信号电平提供给监视器,从而使得微处理器增益控制优于A/D转换器。

每个通道的前端部分都包括有正交数控振荡器(NCO)、数字混频器、桶形移位寄存器和级联积分梳状滤波器(CIC)。NCO具有32-bit频率控制字,可用于信道的分选和载波跟踪,其频率分辨率可达16.3MHz(输入信号速率为70MSPS)。NCO的无虚假信号动态范围(SFDR)大于115dB。桶形移位寄存器可提供介于2-45到2-14之间的增益以防止CIC的溢出。CIC滤波器的级数介于1到5级之间,并且是可编程的,同时,CIC的抽取因子也是可编程的,第5级的抽取因子为5到512,第4级的抽取因子为4到2048,第3级的抽取因子为4到32768,第1级和第2级的抽取因子为4到 65536。

每个通道的后端部分包括有FIR处理模块、AGC和直角坐标到极坐标转换器。FIR处理模块是一个灵活的滤波器计算机,它可用于单一或一组串行抽取的滤波,单一滤波器的阶数可达256,一组串行抽取滤波器的总阶数可达384。FIR支持像抽取、重采样、内插等各种类型的滤波器。可编程的数字滤波器系数的宽度为22-bit,ROM中提供的此系数可用于几种半带滤波器响应或重采样器。而AGC部分则可提供增益高达96dB的固定或自动增益控制。自动增益控制具有两种设置模式和两组环增益。AGC环使用的直角坐标到极坐标的转换器输出也可以用于AM或FM解调。

ISL5216支持定点和浮点并行输入模式,其输出结果可在4-bit定点到32-bit浮点中选取,并可通过微处理器接口进行编程。另外,所有同步通道的输出数据也都通过微处理器接口来读取。

1.3 ISL5216的设计要点

ISL5216主要实现3个功能,即数字正交混频、数据降速率处理和数据成形滤波。其参数配置直接关系到系统的性能,主要参数选择有:总的抽取因子及其在各部分的分配、CIC中的阶数选择、可编程FTR滤波参数的选择、半带滤波器个数的选择。

总的抽取因子选择主要取决于最终的输出数据率和ADC的中频采样率。最终输出数据率是由所需基带信号的带宽决定的,根据抽样定理,输出数据率至少为信号带宽的两倍。ADC采样率的选择对于整个系统的参数设计有着十分重要的作用,适当的过采样对于提高系统的性能会有一定好处。我们从公式 SNR=6.02N+1.7dB+10log(fs/2B)即可得出结论,式中,N为ADC:的位数,fs为采样速率,B为信号带宽。可见,要获得高信噪比,可以提高系统的采样率。但采样率过高,那么最终的抽取因子必然选得很大,这对于抽取前端的抗混叠滤波器来讲,势必增加其阶数和计算量;采样率过低,会增加采样前端抗混叠滤波器的阶数,从而造成设计和制造上的困难。所以,要根据实际情况来确定ADC:采样率。

CIC滤波器是由5级积分器和梳状滤波器组成的抽取滤波器,其阶数和抽取因子可以分别在1~5和4~65 536中选择,这是根据ISL5216数据手册中抽取因子与混叠抑制比的关系来决定的。

可编程FIR滤波器是整个ISL5216中最灵活的部分,可实现抽取,也可单独进行滤波而不抽取。其阶数和系数的选择是根据ISL5216本身的系统资源和可用时钟数来决定的。

抽取链中单个FIR滤波器阶数可以达到256阶,多个FIR滤波器的总阶数可以达到384阶。半带滤波器的选择是灵活的:若抽取率较高,可用半带滤波器实现抽取,最后使用非抽取可编程FIR滤波器来进行均衡;若抽取率较低,可以通过可编程FIR滤波器直接实现抽取滤波而不选用半带滤波器,这是因为半带滤波器的阶数少,滤波幅频特性较差。

ISL5216参数的设计思路是:首先确定中频采样的采样率和最终输出的数据率,根据两者的要求来确定可用的时钟数和总抽取因子;然后进行总抽取因子的分配,包括根据CIC:抽取因子与抗混叠抑制比的关系确定CIC部分的抽取因子,同时也确定了后续可编程FIR滤波器和半带滤波器的抽取因子;最后再根据可用的时钟数和所需的抽取因子计算出FIR滤波器的阶数、系数及半带滤波器的个数;最后核算所使用的资源和时钟数是否满足要求。

2 ISL5216的设计实例

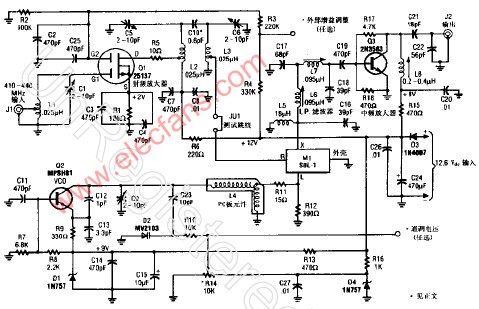

在中频通用接收平台中,接收的中频信号经A/D采样后直接进入ISL5216的输入端进行处理。ISL5216的串行输出都接入FPGA中,进行串并转换并存入FIF0,由DSP读取以进行后续的处理。通过这样一个确定的硬件平台,只需要修改QDDC的内部寄存器参数就能够实现对解调中心频率、输出速率、滤波器带宽等参数的软件控制,实现需要的解调功能。下面将根据使用中的实例来说明QDDC参数配置的主要流程。

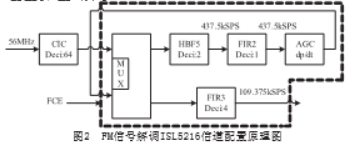

2.1 FM信号解调

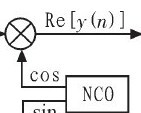

对一个采样频率为56MHz的FM信号进行解调,在鉴频器后需要再加一级滤波器,这时QDDC某一通道的配置原理图如图2所示。

信号首先通过抽取因子为64的CIC滤波器,将56MHz的信号速率降低到875kHz。然后HBF5进行抽取因子为2的抽取,接着通过抽取因子为1的 FIR2,这时信号的速率已经降为437.5kSPS。FIR2是一个带宽为260kHz的低通滤波器,用来降低带外噪声干扰。FIR2输出的信号在通过 AGC和鉴频器后并不直接输出,而是反馈回FCE(滤波器计算引擎)进入FIR3,滤波后的信号才会输出FCE。FIR3是一个带宽为20kHz的低通滤波器,抽取因子为4,其信号输出速率为109.375kHz。如有需要可以在输出之前、FIR3之后连接重采样滤波器,进行分数抽取因子的抽取,使输出的信号速率能与后续处理设备的速率相匹配。FIR滤波器的系数使用Matlab中的fdatool工具来设计,将系数按照滤波器文件格式制作成*.imp文件格式。使用ISL5216配置软件对ISL5216的内部寄存器进行设置。设置如图3所示。

FIR2的输出需要反馈回FCE以进行最后一级的滤波,但ISL5216配置软件并不支持反馈设置,必须自己修改寄存器的值。地址为*108的指令寄存器必须进行修改。FIR2对应的指令寄存器为*108~*10B,其中地址为*108的寄存器的比特位28∶18需要进行修改,由290Cxxxx改为 2A8Cxxxx,作用是使能AGCLF,Pamvth(1∶0)设为”01”,OS停止,FB设为1。最后在串行输出的时候,应将输出格式选为Q2。

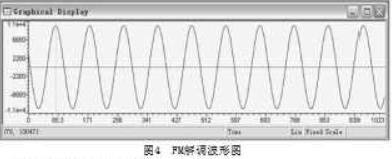

载波频率70MHz,频偏15kHz,调制信号频率1kHz的FM信号解调后的波形如图4所示。

2.2 宽带信号解调

ISL5216单通道的输出带宽可达到1MHz,更宽的带宽可通过多通道串联或多相滤波来获得。下面我将根据使用中的实例来说明这种情况下滤波器的结构及 QDDC参数配置的主要流程。例如:输入速率:56MSPS(10x),输出速率:14MSPS(2.5x),输出带宽:5.6MHz。

这种情况要使用全部四个通道才能实现。QDDC滤波器的结构如图5所示。

通常,最好是CIC滤波器的抽取因子尽可能地大,这样,向FCE中写数据所用的时钟周期就少,但是这又受到混叠衰减的限制。在本例中CIC的抽取因子为 4,混叠衰减大于60dB(fs/R=0.5/2.5=0.2)。

通道0的输出分别输入到通道l、2、3构成三个分支的脉动阵列(systolic avrray)。每个分支都要经过一个19阶的滤波器。通道0、1、2、3滤波器的输入分别延时0、1、2、3个采样时钟,使得通道3输出第一个数据而通道0输出最后一个数据。由于从输入到输出的总抽取数为4×4=16,每个通道可以输出16位的数据。在这种结构中需要一个外部的多路复用器来组合输出数据,即先读取D路数据,然后是C、B,最后是A路。

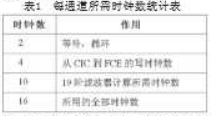

通道0、1、2、3每个输出可提供的时钟数为4×4=16,每个通道所需的时钟数如表l所示,即通道0、1、2、3使用了该通道可提供的每一个时钟。

使用ISL5216配置软件对ISL5216的内部寄存器进行设置。设置如图6所示。

其中第26项,每个通道的延时各不相同。地址为F801的寄存器低17位的设置需要注意一下,主要是各通道AGC和FIR输入输出路径的选择。

3 结束语

本文讲述了四通道数字下变频器ISL5216的功能特点及设计要点,并从工作实际出发,详细介绍了针对FM信号解调鉴频器后的滤波器设计和利用多通道串联来实现宽带信号处理的具体的设计方法。该两种设计方法在不同的实际应用中均性能良好,达到了预期的指标。

责任编辑:gt

-

dsp

+关注

关注

561文章

8276浏览量

368294 -

变频器

+关注

关注

256文章

7461浏览量

155949 -

无线电

+关注

关注

63文章

2215浏览量

119841

发布评论请先 登录

使用一个FPGA便可实现的64通道下变频器

基于FPGA的数字下变频器的设计与实现

基于FPGA的数字下变频器(DDC)的设计

数字下变频器是怎么回事

通道数字下变频器ISL5216的功能特点及应用研究

通道数字下变频器ISL5216的功能特点及应用研究

评论