引言

近年来,无线同播系统在民事和警事中的应用日益广泛,其快速搭建和空中接入等优势在512地震的救灾调度中得以充分体现。同播系统工作时,所有发射站会在同一时刻点以相同频率向外广播,由于各站的发射频率相对于标准频率有不同偏差,在功率重叠区产生频率叠加,出现同频干扰。目前,国内外通信厂家的同播发射机的发射频率偏差大都在1ppm(parts per million)以上,不通过校准,无法达到0.05ppm正常通话的最低要求。有线同播系统是利用光纤网络校准发射频率的。无线同播系统目前只能通过两种方法解决:一是设置中心站,但系统响应速度慢;二是尽量缩小功率重叠区,其建站周期长而且可靠性低。两种方法都没有从根本上解决无线同播系统的同频干扰,发射频率的校准已经成为无线同播系统发展的瓶颈。因此,本文提出一种基于FPGA技术的频率校准系统的设计方案。

1 系统总体设计

1.1 同频干扰的产生和解决方法

一个无线同播系统需要架设若干个大功率发射站点,才能满足大区域的通信需求。站点间硬件和工作环境各有差异,导致各站的频率偏差不同。例如两个发射频率为 350MHz的站点,一个的频偏为+1ppm,另一个为-1ppm,在功率重叠区就会产生700Hz的频率差,形成啸声,影响通话质量。从理论上讲,要保证同频覆盖区的通话质量,必须使各发射站的频偏保持在0.05ppm以下。校准各发射站频率的最好方法,是为其提供统一可靠的基准时钟信号。GPS定位卫星信号精度高,没有时间和地域的限制,可以作为基准时钟信号同步各站的基准振荡器,解决同频干扰的关键性问题。

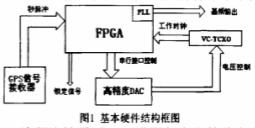

1.2 系统硬件设计

频率校准系统主要由高精度GPS信号接收器、FPGA芯片、VC-TC2XO(压控恒温晶振)、高精度DAC(数模转换器)等部分组成。VC-TCXO为 FPGA提供工作时钟,也为发射提供基准频率。FPGA通过GPS秒脉冲信号计算标准时长,记录下这段时间内VC-TCXO产生的脉冲总数,与标准的脉冲数进行对比,最后通过DAC对VC-TCXO进行电压校正。校准后的VC-TCXO频率通过FPGA内部PLL倍频,成为发射频率。基本硬件结构框图如图 1所示。

FPGA编程比较灵活,可设置任意位的片上寄存器,保证了脉冲计数的精度,适用于高精度的频率校准。本设计采用Actel公司Fusion系列的 AFS600,属于Flash架构,内部集成了60万逻辑门。以Flash为基础的FPGA将配置信息储存在片上Flash单元中,一旦完成编程,配置数据就会成为FPGA结构的固有部分,在系统上电时无需通过外部SRAM载入配置数据。AFS600可靠性高、功耗低,节省外部元件,适合开发手持设备。

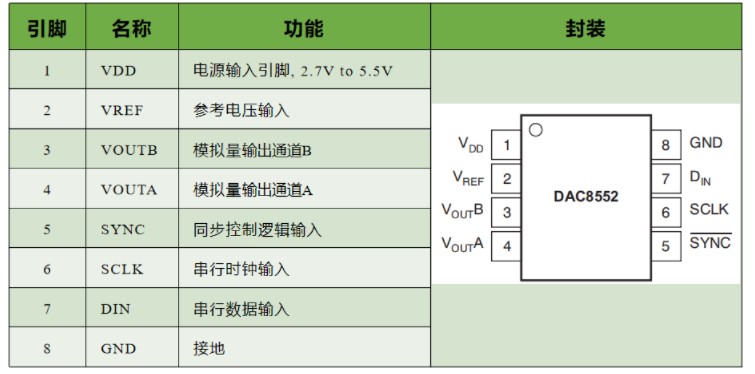

本设计采用的GPS接收机是Motorola公司生产的M12M授时型OEM模块,输出秒脉冲信号的精度±20ns。压控恒温晶振采用华晶达电子公司的 VC-TCXO(503212.8M),中心频率12.8MHz,工作电压3.3V,温度稳定度±1.0ppm,老化率±1.0ppm/年,控制电压范围 1.65±1.0v,可调节频率范围1 2.8MHz±300Hz。高精度DAC采用TI公司的。DAC8552,具有16位精度,可串行SPI控制方式,参考电压为3.3V。

1.3 分级控制方案

基于效率和精度的需要,本设计采用分级控制方案。GPS秒脉冲信号的精度误差为20ns,折算12.8MHz频率,最大频偏为20ppm。若以1秒作为时长比较脉冲数,调整的精度无法达到要求,同频干扰依然存在。由于秒脉冲信号的精度误差呈均匀分布,加长检测的时间可以提高信号精度,从而提高校准精度。但校准效率会下降,发射准备时间增加。另一方面,DAC的控制方式也影响系统的精度和效率。单次调整幅度大,效率高但精度低,幅度小则需时过长,所以不能以固定的幅度调整。根据VC-TCXO和DAC8552的参数,DAC最小的调整幅度为0.015Hz,DAC数值与VC-TCXO频率的关系是:

f(b)=12.8MHz+ (b-b)×O.015Hz

式中f(b)是当前VC-TCXO频率,b是FPGA写入DAC的数值,b’是VC-TCXO输出12.8MHz时对应的DAC数值。VC-TCXO的电压可调范围是1.65±1.0V,折算b的有效范围为12 909~52 627。

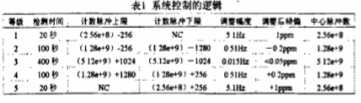

为了平衡精度和效率的需要,系统采用了分级控制的方案。如表1所示,系统控制的逻辑分为五级。等级3的频偏和调整幅度最小,检测时间最长。脉冲数上下限用于固定时长内脉冲数的比较,判断是否需要调级。VC-TCXO的温度和老化的因素使晶体频率的上下限改变,所以等级1没有计数脉冲下限,等级5没有上限。 FPGA根据当前的级别设定检测时间,再通过收到的脉冲数判断升级、降级或是调整电压值。

2 FPGA设计

2.1 FPGA顶层设计

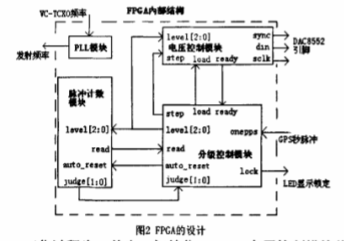

FPGA的设计采用自顶向下的设计方法,用Verilog HDL语言描述,在Actel公司的开发软件libero8.0中进行综合、优化、仿真和定时分析。顶层设计由PLL、分级控制、脉冲计数模块以及电压控制模块组成,如图2所示。

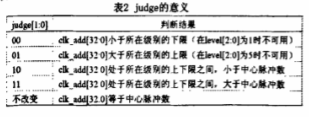

工作过程为:首先,初始化FPGA,电压控制模块将DAC8552的电压输出值置于中位(1.65V),分级控制模块的开始分级设定为3,并通过 level[2∶0]连线将级别赋给脉冲计数模块和电压控制模块;分级控制模块收到GPS秒脉冲时,通过auto reset启动脉冲计数模块,收到read信号时读入judge[1∶0],judge[1∶0]的意义如表2所示。如果 judge[1∶0]=00,level[2∶0]不为1,level[2∶0]降级;judge[1∶0]=01,level[2∶0]不为 5,level[2∶0]升级;judge[1∶0]为10或11,通过step和load引脚调整电压控制模块。

2.2 脉冲计时模块设计

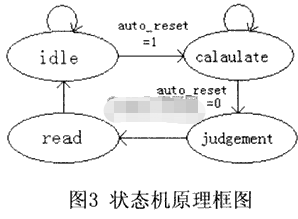

脉冲计时模块接口信号包括:级别输入level[2∶0]、开始计数输入auto_reset、判断输出judge[1∶0]、读指令输出read,还有输入时钟fre_in和复位使能reset,模块内部设寄存器clk_add[32∶0],用于脉冲计数。模块的状态包括idle、calculate、 judgment和readtime,状态机如图3所示。

其具体工作过程为:

(1)状态为idle时,read置0,clk add[32∶0]清空,读入level值。Level是计数判断的基准,必须在计数前读入。

(2)当收到auto_reset为高电平,状态从idle转至calculate开始脉冲计数。由于计数的频率同时是FPGA的工作频率,所以 clk_add[32∶0]只需在calculate状态下每个时钟累加一次。

(3)auto_reset变为低时,状态转至judgment,将clk_add[32∶0]与所在级别的上下限对比,将结果通过judge[1∶0] 输出。

(4)状态转至readtime,将read置1,read信号告知分级控制模块judge[1∶0]信号已经更新,要求读取,当clk_add [32∶0]等于中心脉冲数,read不置为1,表示无需改变电压值。

(5)状态转回idle。

2.3 电压控制模块设计

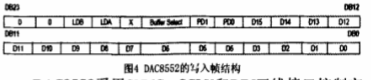

电压控制模块的接口信号包括:级别输入level[2∶0]、调整方向输入step、调整输入load、就绪输出ready、DAC接口输出(sync、 SClk和din),还有输入时fre_in和复位使能reset,模块内部设寄存器data reg[23∶0]用于生成控制DAC的帧,max_24bits[4∶0]用于记录当前是控制帧的第几位输出。每帧长度为24位,控制字包括:LDB、 LDA选择写入通道,Buffer Select选择写入的寄存器,PDl、PD0选择输出阻抗模式,D15~D0为16位的DAC数据。其帧结构如图4所示。

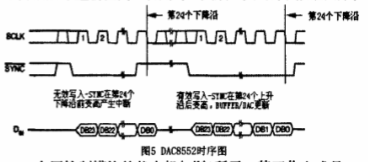

DAC8552采用SYNC、SCLK和DIN三线接口控制方式,从SYNC变低时开始写入,SCLK产生写时钟,在SCLK下降沿数据被写入 DAC8552,SYNC必须在第24个下降沿后才重新拉高,否则写入失败。其时序图如图5所示

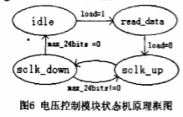

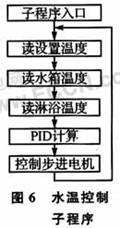

电压控制模块的状态机如图6所示,其工作方式是:

(1)idle状态时,ready输出赋为1,sclk赋为1,sync赋为1,max_24bits赋为24。

(2)当load=1时,状态转至idle,sync赋为0,data reg通过level和step引脚的值产生相应的控制帧。

(3)当load=0时,状态转至sclk_up,sclk赋为1,din赋为data_reg[max_24bits-1]。

(4)状态转至sclk down,sclk赋为0,max_24bits自减1。当max_24bits=0时,状态转至idle;否则状态转至sclk_up。

状态sclk_up和sclk_down的循环是用于产生控制DAC8552的时钟和数据,din通过max_24bits这个寄存器实现对 data_reg从高到低逐位输出。

3 实验结果

3.1 软件仿真

利用Libero 8.0开发环境集成的Modelsim软件对电压控制模块设计进行仿真。模拟写入DAC8552的A、B通道数据为1010 1111 OO10 1011,十进制为44843,折算为电压值是2.258V。仿真时序图如图7所示,满足DAC8552接口的时序要求。

3.2 板上调试

将程序烧入FPGA运行,并通过频率计实际测量,测量结果如图8所示。由于频率计的精度只达到1Hz,测量的数据会有所偏差。考虑到校准后的频偏已经接近+0.05ppm(+0.64Hz),证明系统功能已经实现。但系统的效率不够高,需时过长,算法有待改善。

4 结束语

本设计通过FPGA、高精度DAC、压控恒温晶振和GPS信号接收模块,成功实现了同播系统发射设备的频率校准。除了同播系统,本设计还可应用于卫星信号同步、跳频通信的相关领域,发展空间十分广阔。

责任编辑:gt

-

FPGA

+关注

关注

1629文章

21736浏览量

603285 -

芯片

+关注

关注

455文章

50812浏览量

423533 -

接收机

+关注

关注

8文章

1181浏览量

53469

发布评论请先 登录

相关推荐

DAC8552高精度模数转换器的驱动设计与实现

利用dac8551/dac8552芯片通过3伏基准电压芯片产生0到150mv的电压信号,可以强制让电压不超过150mv吗?

Cortex M3系列的LPC1768操作DAC8552问题

MSP430使用DAC8552的问题

如何利用AFS600设计太阳能热水器通用控制器?

DAC8552,pdf(16-Bit, Dual Chann

基于FPGA的恒温晶振频率校准系统的设计

基于AFS600芯片与8051的阳能热水器控制器的设计

基于GPS的恒温晶振频率校准系统的设计与实现

翔腾传感器信号调理芯片和校准系统市场的开拓

DAC8552双通道、电压输出数模转换器(DAC)数据表

基于AFS600和DAC8552芯片实现频率校准系统的设计

基于AFS600和DAC8552芯片实现频率校准系统的设计

评论