Dallas公司生产的集成电路中,广泛应用了1-wire总线。主机只需1根连线就可以把一个或数个1-wire总线器件连接起来,实现有效可靠的数据通信。但是,在使用1-wire总线驱动多个器件、连接电缆线较长的场合,它的驱动能力是否适应;或者说,应该如何提高1-wire总线器件的驱动能力? 本文就此问题进行分析和实验。

1 1-wire总线简介

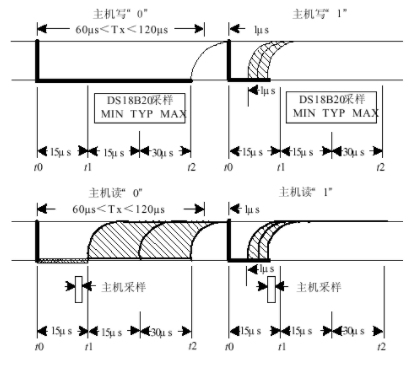

从 Dallas公司提供的图1所示读写时序图可以看出,主机读DS18B20 时,首先应该把线拉低至少1μ s,然后在15μs内读总线的逻辑状态(t0~t1)。DS18B20 则在主机拉低总线1μs内开始输出数据,如果为0,继续拉低总线,并在15~60μs(t1~t2)之间释放总线(典型值为30μs),由上拉电阻把总线拉至高电平;如果数据位为1,则在主机拉低总线1μs后,DS18B20 的DQ端呈现开漏状态,一旦主机释放总线,上拉电阻就把总线拉至高电平。在60μs(t2)之后,1-wire总线还必须继续保持高电平至少1μs,作为两个数据位之间的分隔(称之为“恢复时间”)。由此可见,为了保证所读数据的可靠性,89C2051必须在15μs前读取总线的逻辑状态。

图1 1-wire总线读写时序图

主机在对DS18B20进行写入操作时,首先应该拉低1- wire总线至少1μs 。然后,如果写入数据位是 0,则继续拉低总线至60μs结束(t2);否则就释放总线,由上拉电阻把总线拉成高电平。而DS18B20则在15~60μs之间(t1~t2)读入数据(典型值为15μs)。同样,在60μs之后(t2),1-wire总线还必须继续保持高电平至少1μs,作为两个数据位之间的分隔。

2 实验电路参数的分析与实验结果

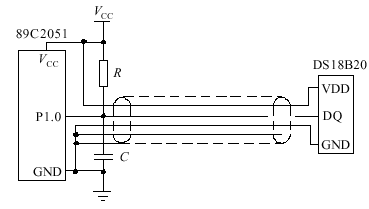

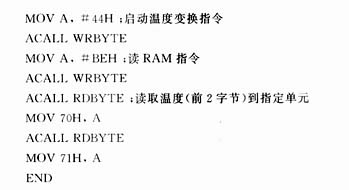

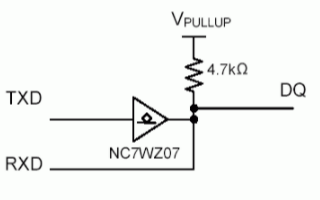

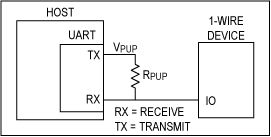

以1-wire总线的数字温度集成电路DS18B20与单片机89C2051 为例,其接口电路如图2所示,时钟频率为12MHz 。89C2051的P1.0口与DS18B20的DQ相连。1-wire总线器件的DQ口(数据口线)都为开漏结构,以便可以在1-wire总线上挂接多个DS18B20。因此,在1-wire总线上应该加接1个上拉电阻,文献推荐值为4.7kΩ。笔者使用2 m长的4芯屏蔽电缆连接89C2051 和DS18B20 ,其中一芯以及外屏蔽单端接地,其余分别为VCC、GND 和DQ 。经测试,DQ线到地的分布电容为131pF/m 。为了能够测试1-wire总线的驱动能力,在DQ线上加接电容,以便近似地模拟长电缆,等效电路如图3所示。可以通过选择上拉电阻的值,合理安排 t0~t1和t0~t2两个时间段,以提高1-wire总线器件驱动长总线的能力。自然,上拉电阻越小,其拉动1-wire总线的能力就越大,但是要受到 DS18B20的低电平吸入电流的限制。综合考虑各种因素,选取上拉电阻值为1.5kΩ。

图2 89C2051与DS18B20接口电路

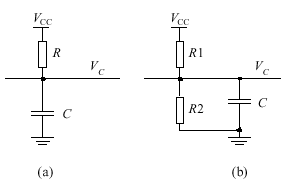

图3 1-wire总线逻辑电平转换时的等效电路

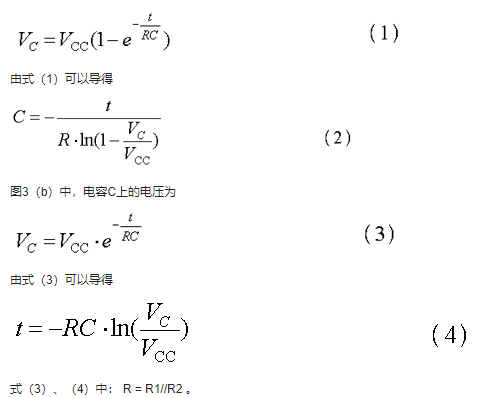

由电工学可知,图3(a)中电容C上的电压为

在t0~t1阶段,由 89C2051拉低1-wire总线并保持至少1μs。89C2051的I/O口输出低电平时可吸入20mA的电流,其内阻因是非线性特性,不会大于 50Ω。DS18B20的逻辑0输入电平最大可为0.8V;89C2051为0.9V,取 VC = 0.8V,VCC = 5V。把上述数据代入方程(4),取负载电容C = 10nF,可以得到t =0.9μs;加上SETB指令需时1μs ,稳定所需时间(至少1μs),取t0~t1 = 3μs。

在t1~t2阶段,无论是89C2051还是DS18B20输出0电平,由于总线电平已经是0电平,不存在阶跃问题,所以不必计算。

如果是逻辑1,不管是由89C2051还是由DS18B20输出, 两者的输出FET均为开漏状态(89C2051有弱上拉,可以忽略),由上拉电阻把1-wire总线从0电平上拉到高电平。可以用于把总线从0电平上拉到 1电平的时间t1-t2 = 15 - 3 - 1 = 11μs,其中1μs在读DS18B20时用于读操作,在写DS18B20时用来补偿指令MOV DQ,C所需的时间。DS18B20的逻辑高电平最低为2.2V,89C2051为1.9V,取VC = 2.2V 。

把上述数据代入方程(2),当上拉电阻为4.7kΩ时,可以算得C = 4.0nF;当上拉电阻为1.5kΩ时,C = 12.6nF,相当于96.5m长的屏蔽电缆。

3 实验结果

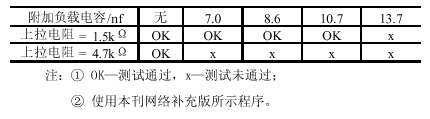

表1为实验数据,使用2m长的4芯屏蔽电缆,在总线上加接电容以模仿长电缆。

表1 1-wire总线器件驱动能力与上拉电阻的关系

从表1可以看出,实验结果与理论计算基本相符。由于实验条件的限制,测试是相当粗糙的。更细致的调节,可以使用示波器观察1-wire总线上的波形来对电路参数与程序进行微调,以求得到更好的结果。笔者曾以其它的定时关系编制了实验程序,其驱动能力均不如本程序。

责任编辑:gt

-

集成电路

+关注

关注

5396文章

11645浏览量

363762 -

单片机

+关注

关注

6044文章

44632浏览量

639488 -

总线

+关注

关注

10文章

2909浏览量

88499

发布评论请先 登录

相关推荐

基于C++模板技术的1-wire总线编程

1-wire单总线的基本原理

1-wire单总线的基本原理

1-Wire器件与8051系列单片机的软件接口

1-Wire总线主机

如何使用微处理器的UART来实现1-Wire®总线主机

通过串行接口读写1-Wire器件

使用UART实现1-Wire总线主控

通过调节上拉电阻来提高1-wire总线器件的驱动能力

通过调节上拉电阻来提高1-wire总线器件的驱动能力

评论