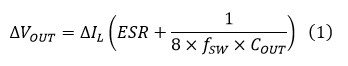

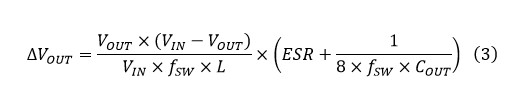

Buck 转换器的输出电压纹波峰峰值计算公式为:

其中,ESR 是输出电容的等效串联电阻,COUT 是输出电容的容量有效值,ΔIL 是电感电流纹波峰峰值,fSW 是转换器的工作频率。强调电容有效值是因为要考虑到陶瓷电容在不同电压下的容量衰减问题,这需要特别注意。

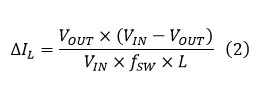

电感电流纹波峰峰值计算公式为:

其中新出现的参数有输入电压 VIN、输出电压 VOUT 和电感量 L。

将 (2) 式代入 (1) 式可得:

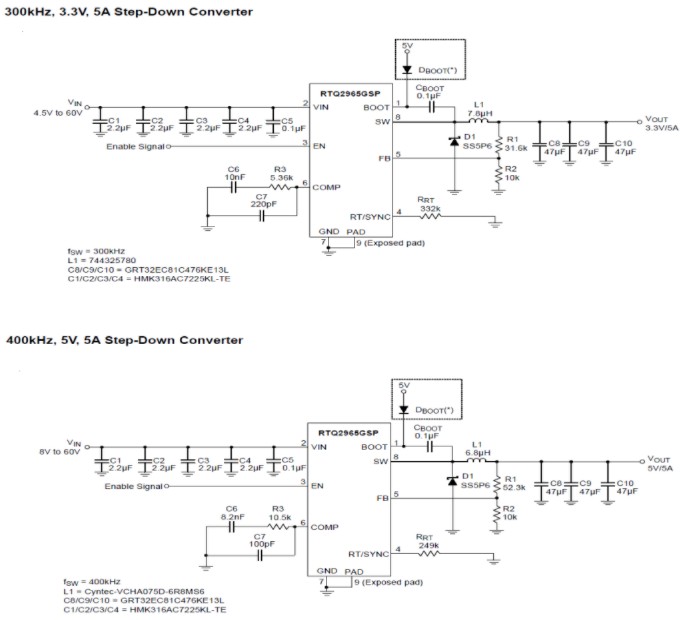

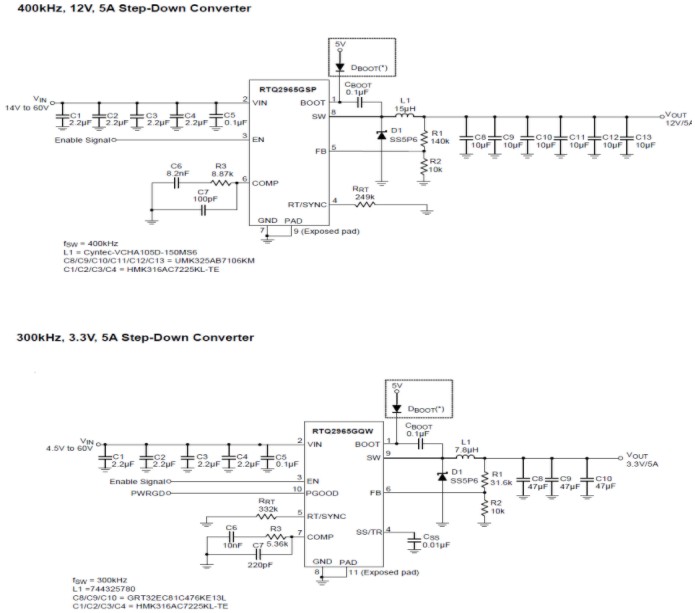

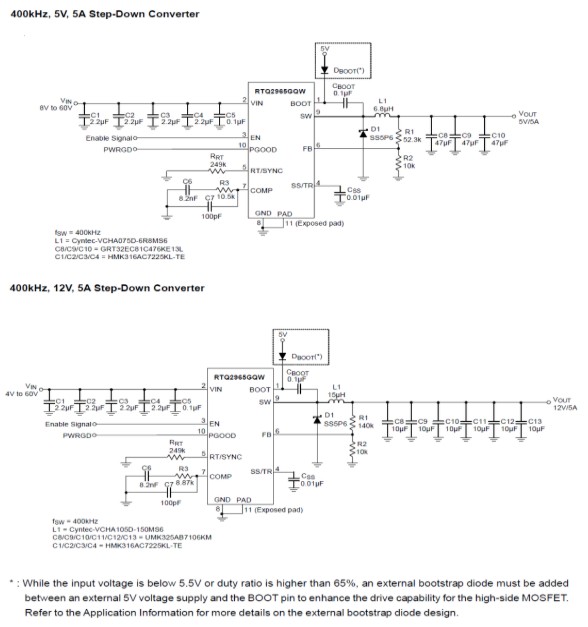

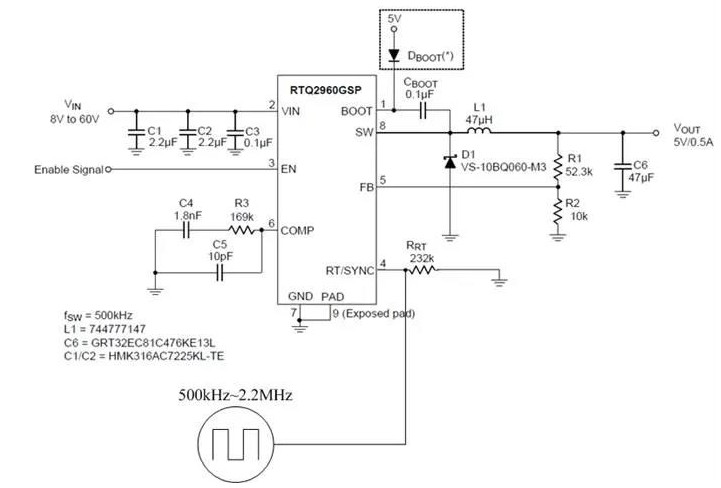

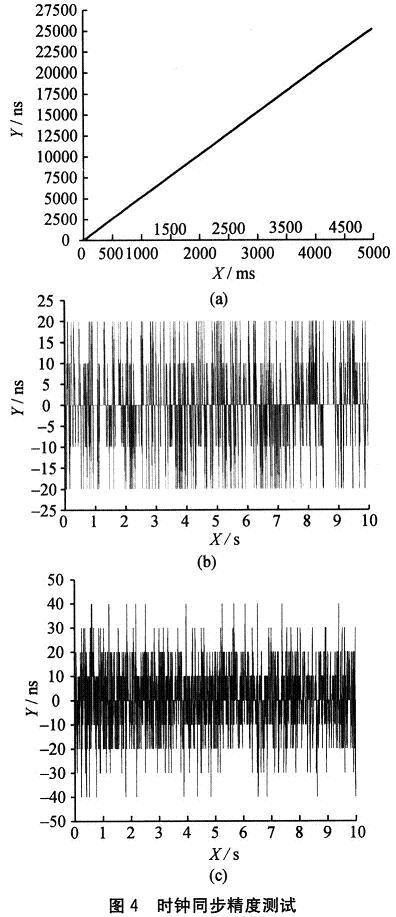

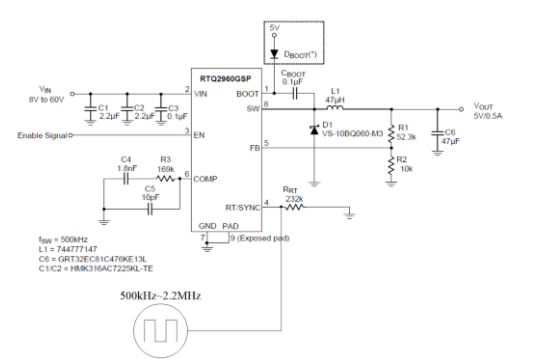

由此公式可见,Buck 转换器的工作频率 fSW 对输出电压纹波电压峰峰值的影响是巨大的,它与由输出电容 ESR 引起的纹波成反比关系,对由输出电容量引起的纹波则是平方反比关系,所以在应用中只要将工作频率提高一点点就可以带来输出纹波的大幅度下降,对保证输出电压的洁净程度有巨大的作用。由于 RT(Q)636x、RTQ296x-QA 等 60V Buck 器件都具有外同步的能力,我们又希望用户在引入外同步时钟信号时不要降低电路本身的输出电压性能,所以在规格书中规定引入外同步时钟信号的频率不能低于由 RRT 所设定的工作频率,以免在切入外同步工作模式以后出现纹波超标的问题。

本文是因为有读者留言询问为什么外同步时钟信号的频率不能高于电阻设定的工作频率而写,有读者关注这样的细节是我很高兴的事情,因为世界上怕就怕认真二字。武汉在一年前出现了一种从未见过的病毒,我们认真地对待它了,虽然有许多人借此非难,但是我们自己干自己的事,全国人民一起行动,还把火神和雷神都请出来帮忙了,让人民真正地得到了实惠,这就是认真的好处。愿我们都继续认真下去!愿以此与大家共勉!

责任编辑:pj

-

转换器

+关注

关注

27文章

8607浏览量

146753 -

电容

+关注

关注

99文章

5967浏览量

149863 -

同步时钟信号

+关注

关注

0文章

3浏览量

6416

发布评论请先 登录

相关推荐

采用DM385芯片做外同步采集,时钟,HS,VS,DE,信号的频率都对,信号质量也正常,却产生over flow这个问题是什么原因?

FPGA的时钟频率同步设计

什么是时钟频率_时钟频率详解和编程

如何提高FPGA的工作频率

为什么需要debug时钟频率 Debug时钟频率原理详解

为什么外同步时钟信号频率不能高于电阻设定的工作频率?

为什么外同步时钟信号频率不能高于电阻设定的工作频率?

评论