本文对Video out IP和Video Timing Controller IP进行简要介绍,为后文完成使用带有HDMI接口的显示器构建图像视频显示的测试工程做准备。

Video out IP

简介

AXI4-Stream to Video Out核心设计用于从实现视频协议的AXI4-Stream接口连接到视频源(并行视频数据、视频同步和空白)。该IP与Xilinx视频定时控制器(VTC)核心一起工作。该核心提供了一个具有AX14-Stream接口的视频处理核心和视频输出之间的桥梁。

特点

视频输出(带同步信号的特定时序下的并行视频数据--带有行场同步信号和消隐信号的有效视频数据)。

输入数据是通过AXI-stream的从接口。

可选择的视频时序同步模式,允许VTC发生器自由运行(主模式)或被控制(从模式)使用一个滞后机制。

自动同步视频时间到AXI4-Stream视频。

支持AXI4-Stream和视频时钟域之间的普通或独立时钟模式。

可选择的FIFO深度32-8192位。

可选择的输入数据宽度8-256位。

支持隔行操作。

组件宽度转换为8,10,12,16位。

AXI4-Stream to Video Out IP将AXI4-Stream视频协议从使用此协议的Xilinx视频处理IP转换为带有行场同步和特定时序信号的视频输出接口,从而与使用该视频时序的普通视频系统接口相互连接。

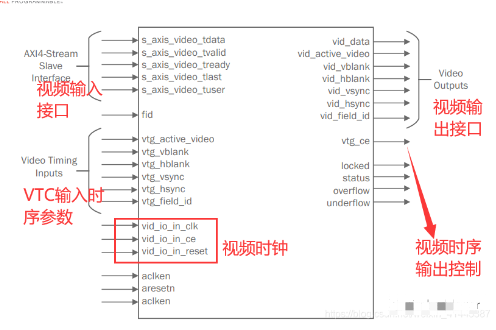

输入输出信号

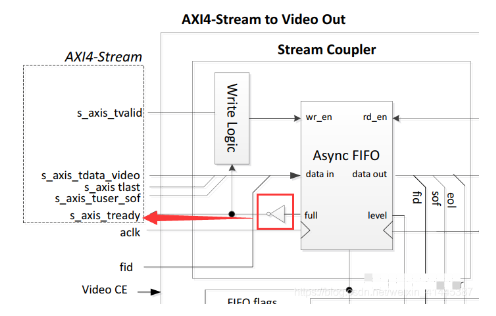

AXI4-Stream to Video Out IP的输入信号是一个AXI4-Stream从接口。该接口由并行视频数据,tdata,握手信号tvalid和ready,以及两个标志,tlast和tuser组成,用于识别视频流中的特定像素。tlast信号指定每一行的最后一个有效像素,也称为行结束(EOL)。tuser信号指定帧的第一个有效像素,称为帧的开始(SOF)。这两个标志对于标识AXI4流接口上的像素位置是必要的,因为不存在行场同步信号。只有有效的像素数据被携带在总线上。

AXI4-Stream to Video Out IP的输出信号是常用的视频接口。视频接口包含以下信号:

Parallel video data

Pixel clock

Vsync

Hsync

Vbank

Hblank

Data Valid

Field ID

IP架构图

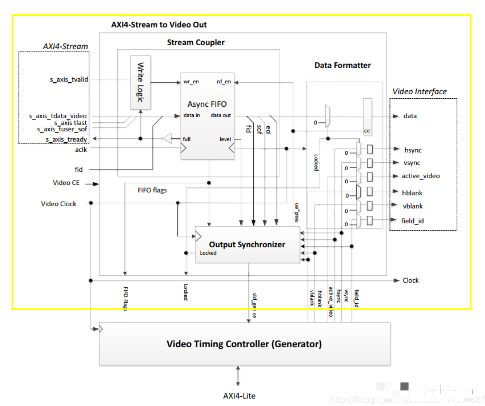

该IP设计要和VTC IP一起使用。 VTC IP核提供视频时序参数,并产生视频时序信号。下图给出的是AXI4-Stream to Video Out IP的系统架构:

在AXI4-Stream to Video Out IP的内部,通过一个异步的FIFO进行跨时钟域的数据信息的缓存处理,然后经过一个输出同步器(output synchronizer)将AXI-stream的视频数据和VTC生成的视频时序参数进行同步,最终生成输出端口的视频输出的接口。

支持时钟模式

AXI4-Stream to Video Out IP支持两种时钟模式:slave和master时钟模式。这里的主从模式是对于 VTC ip而言的。

slave模式

在slave模式下,AXI4-Stream to Video Out IP输出的视频数据的时序信号(行场同步、消隐等),将由VTC生成相对应的时序信号进行自适应,AXI4-Stream to Video Out IP通过vid_gen ce信号进行控制时序信号的输出,从而达到输出的视频信号和输出信号同步的目的。

master模式

在master模式下,VTC IP核将会不受限制地运行,相位差取决于启动条件。这时就要求AXI4-Stream to Video Out IP的视频数据尽量满足VTC IP核产生的时序信号。

通常,建议使用slave模式来最小化缓冲区域和延迟时间都需求。

FIFO深度配置

在AXI4-Stream to Video Out IP,通过一个异步的FIFO进行跨时钟域的数据信息的缓存处理,这里就要考虑FIFO的深度的具体配置,当FIFO的深度不合适时,很容易造成FIFO读空或者写满读满,得到的视频数据容易造成丢失。这里读满的时候影响不太大因

为到FIFO读满后,FULL信号会进行取反使得tready信号拉低,从而使得视频数据传输暂停。

考虑FIFO为空时,当输出的视频信号处于数据有效输出的阶段,也就是正常的显示器显示的区域,则会造成当前像素点读取错误,并且后续的像素点都可能错位。

当调用该IP时,FIFO深度可以通过GUI界面进行选择。异步FIFO的缓冲要求主要取决于上游处理器通过AXI4-Stream时钟(aclk)和视频输出时钟(vid_io_out_clk)频率之间的相对数据速率,以及正在传输的信号作为标准。如果上游AXI4-Stream来源不能提供数据以持续的速度等于或大于视频时钟频率,然后需要额外的缓冲存储传入的像素之前,当他们需要这样的像素可以生成一个连续流输出没有过早读空的FIFO。换句话来说,就是如果输入数据的时钟小于输出数据的时钟,我们可以通过提前存储数据的方式来弥补传输时的数据传输速度差异。如果从AXI4-Stream时钟(Faclk)获得的持续像素率等于或大于视频输出像素时钟(Fvclk),那么当输入的AXI4-Stream数据中没有停顿时,只需要最小缓冲区大小(32个位置)。在该情况下,FIFO在每行的EOL拉高后读空。如果Faclk小于Fvclk,可能需要额外的缓冲。FIFO必须存储足够的像素,以供应他们在整个活动线连续。这意味着输入FIFO还必须足够大,以在此期间连续提供输出像素。

可以计算出先进先出初始填充水平的一阶近似。假设R小于1,则计算最小初始填充层:FIFO Initial Fill Level = 32 + Nhactive * (1- R) + Nhstall * (1/R)

其中Nhactive是行活动周期的时钟滴答数。Nhblank是水平消隐周期的时钟滴答数。Nhstall是进入的流在水平活动期间被停止的时钟滴答数。R是计算为Faclk/Fvclk的时钟比率。当R大于等于1时,可以去掉第二项[Nhactive * (1 - R)]。Nhstall很难通过分析来确定。

总FIFO深度必须略大于初始填充水平,以防止FIFO溢出:FIFO depth min = 32 + FIFO initial Fill Level在每种情况下,这都少于一整行数据,所以如果提供了行缓冲区,就足够了。然而,在许多情况下,不需要完整的行缓冲区。

接口框图

下图描述了该IP可用的各种接口。

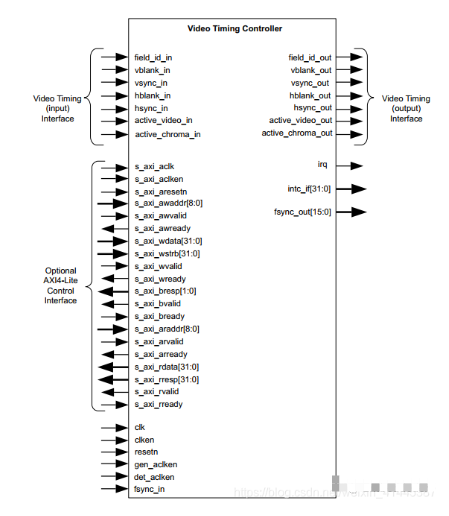

Video Timing Controller IP

简介

Video Timing Controller IP是一个通用视频时序信号发生器和检测器。所有的视频系统都需要视频时序信号的管理,这些信号用于同步传输进程。VTC IP核的功能是检测和产生这些时序信号。在该IP的输入端,自动检测水平和垂直同步脉冲,极性,消隐时间和活动视频像素相关时序参数;在输出端口,它产生水平和垂直消隐和同步脉冲使用的标准视频系统,包括支持可编程脉冲极性。该IP通常与Video in to AXI4-Stream IP一起用于检测传入视频数据的格式和时序信息,或与AXI4-Stream to Video out IP一起用于为视频输出设备(如视频监视器)生成输出视频时间。

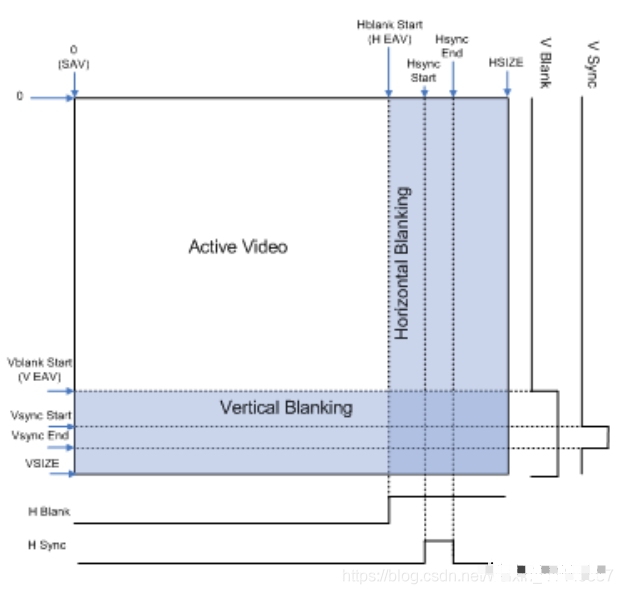

视频时序

在对视频数据输出时,要根据视频时序参数来进行时序信号的驱动从而保证视频数据的正常输出。视频系统可以利用不同极性的行场同步或消隐信号的不同组合来同步处理和控制视频数据。VTC IP通过提供一个高度可编程和灵活的核心,允许检测和生成视频系统内的各种时序信号,从而简化了视频时序信号产生的工作。

支持工作模式

Video Timing Controller IP支持AXI4-Lite接口和一个固定模式接口。

AXI4-Lite接口允许将IP轻松地合并到Vivado项目中,并且可以通过AXI4-Lite。

Constant接口利用图形用户界面(GUI)可配置的IP参数来设置固定模式操作的IP。

接口框图

下图描述了该IP可用的各种接口。

责任编辑:lq6

-

显示器

+关注

关注

21文章

5030浏览量

140740 -

发生器

+关注

关注

4文章

1372浏览量

62031 -

fifo

+关注

关注

3文章

392浏览量

44065 -

HDMI接口

+关注

关注

1文章

135浏览量

34296

原文标题:ZYNQ-Video out IP和Video Timing Controller IP简介

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Multi-Scaler IP的Linux示例以及Debug(上)

Xilinx FPGA高性能NVMe SSD主机控制器,NVMe Host Controller IP

Xilinx FPGA NVMe主机控制器IP,高性能版本介绍应用

浅谈S-VIDEO接口静电浪涌防护

关于Video out IP和Video Timing Controller IP的介绍

关于Video out IP和Video Timing Controller IP的介绍

评论