下面给出一个基于阻塞赋值和非阻塞赋值的多级触发器级联实例,要求将输入数据延迟 3 个时钟周期再输出,并给出对应的 RTL 级结构图和仿真结果。

(1)基于 D触发器的阻塞赋值语句代码如下:

module pipeb1 (q3, d, clk);

output [7:0] q3;

input [7:0] d;

input clk;

reg [7:0] q3, q2, q1;

always @(posedge clk)

begin

q1 = d;

q2 = q1;

q3 = q2;

end

endmodule

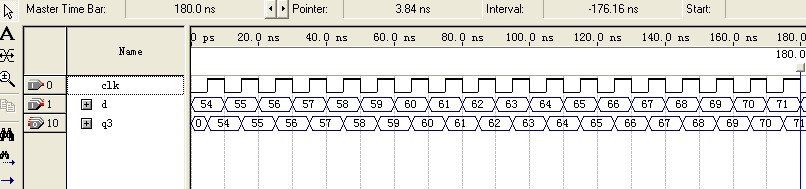

上述代码综合后能得到所期望的逻辑电路吗? 答案是否定的, 根据阻塞赋值语句的执行过程可以得到执行后的结果是 q1 = d;q2 = d。实际只会综合出一个寄存器,如图 8-33 所示,并列出下面的警告信息,而不是所期望的三个。其中的主要原因就是采用了阻塞赋值,首先将 d 的值赋给 q1,再将q1 的值赋给q2,依次到q3,但是 q1、q2、q3 的值在赋值前其数值已经全部被修改为当前时刻的 d 值,因此上述语句等效于 q3=d,这和图 8-33 所示的 RTL 结构是一致的。

(2) 如何才能得到所需要的电路呢?如果把 always 块中的两个赋值语句的次序颠倒后再进行分析:先把 q2 的值赋于 q3、再把 q1 的值赋于 q2,最后把 d 赋于q1。这样在先赋值再修改,可以使得 q2,q3 的值都不再是 d 的当前值。修改后的代码如下所列。

module pipeb2 (q3, d, clk);

output [7:0] q3;

input [7:0] d;

input clk;

reg [7:0] q3, q2, q1;

always @(posedge clk)

begin

q3 = q2;

q2 = q1;

q1 = d;

end

endmodule

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

FPGA

+关注

关注

1630文章

21759浏览量

604353 -

电路图

+关注

关注

10350文章

10721浏览量

531448 -

Verilog

+关注

关注

28文章

1351浏览量

110162

原文标题:FPGA学习:verilog中阻塞的理解与例子

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于阻塞赋值和非阻塞赋值的多级触发器级联实例

基于阻塞赋值和非阻塞赋值的多级触发器级联实例

评论