根据Yole统计,2019年全球先进封装市场规模约290亿美元,折合人民币1950亿,并且在2019年到2025年之间将以6.6%(约129亿人民币)的CAGR(Compound Annual Growth Rate / 复合年均增长率)在增长,在2025年将达到420亿美元(约2824亿人民币)。

封装领域曾经是整个半导体供应链中OSAT(Outsourced Semiconductor Assembly and Testing/外包半导体(产品)封装和测试)和IDM(Integrated Design and Manufacture / 半导体垂直整合型公司)的主要业务,而如今这一领域正在发生着范式的转变,主要来自代工厂、基板(Substrate)/PCB(Printed Circuit Board/印制电路板)供应商、EMS(Electronic Manufacturing Services/电子制造服务)/ODM(Original Design Manufacturer/原始设计制造商)等在内的不同商业模式的厂商们正在进入这一市场,并且在不断瓜分OSAT(Outsourced Semiconductor Assembly and Testing/外包半导体(产品)封装和测试)的市场份额。

先进封装正在从一个基板(Substrate)平台转向硅平台,这一重大转变同时给台积电、英特尔和三星这样的巨头们带来巨大的机遇,并且引领先进封装市场的关键技术创新。

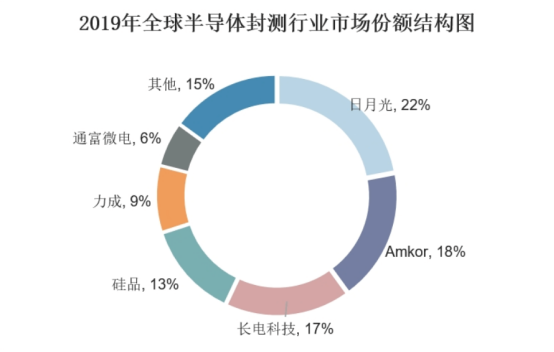

根据Yole统计,全球在先进封测领域的25家OSAT(Outsourced Semiconductor Assembly and Testing/外包半导体(产品)封装和测试)厂商中,台积电排名第 4,头号玩家诸如ASE/SPIL(日月光/矽品精密工业)、Amkor(安靠科技)和江苏长电科技都在对先进SiP(System in Package)和扇出技术进行投资,以增强自身在先进封装市场中的技术竞争力。

公开资料

根据2019年全球封测市场占有率分析,日月光、安靠、长电分别以22%、18%、17%的占比,长电科技在收购星科金鹏后一举成为全球第三大封测厂。

摩尔定律逐渐放缓,异构集成和各大应用(5G、AI、HPC、IoT等)推动着先进封装市场的快速发展,因此先进封装在整个集成电路市场中的份额在不断增加,根据Yole的报告,在2025年将接近整个市场的50%左右。

3D堆叠技术的驱动获得的营收将是最高的,2019~2025年间的CAGR(Compound Annual Growth Rate / 复合年均增长率)在21%,紧随其后的是嵌入式芯片和扇出型技术,同一时期的CAGR(Compound Annual Growth Rate / 复合年均增长率)为18%和15.9。扇出型技术进入移动设备、网络和汽车领域,3D堆叠技术进入AI(Artificial Intelligence)/ ML(Machine Learning)、HPC(High Performance Computing)、数据中心、CIS(CMOS Image Sensor)、MEMS(Micro-Electro-Mechanical System)/传感器领域;以及嵌入式芯片进入移动设备、汽车和基站领域。

从细分市场情况了解到,2019年移动设备和消费市场占到整个市场的85%,2019年~2025年将以5.5%的CAGR(Compound Annual Growth Rate / 复合年均增长率)增长,将接近先进封装市场的80%收益。

如今高速扩张的AI市场同样推动着先进封装行业的高速增长,AI芯片组需要更快的运算内核、更小的外形、更高的能效利用等不断的驱动着先进封装市场。一些重要的半导体公司也在积极的调整战略决策,推出全新的先进封装设计技术。2020年8月,Synopsys宣布与台积电达成战略合作,台积电采用其包含编译器的先进封装方案,提供通过验证设计流程,可用于多芯片封装(CoWoS)以及集成扇出型封装(InFO)等先进设计。

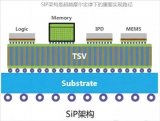

由于终端用户希望他们使用的设备更小、更快、更节能、性能更高。而在单一芯片中封装更多的功能,必然成为半导体封装未来的一个的重要趋势。SiP(System In a Package)是一种系统级别的封装,它将两个或多个异构半导体芯片和无源器件组装到一起,形成一个实现特定功能的标准封装体。

从架构上来讲,SiP(System in Package)是将多种功能芯片,包括处理器、存储器等功能芯片集成在一个封装体内,从而实现一个基本完整的功能。

与传统的系统相比,SiP(System in Package)封装突破了传统封装技术的桎梏。传统的系统,由PCB(Printed Circuit Board)板来承接芯片,通过排线将PCB板和芯片进行连接,而PCB(Printed Circuit Board)板的线宽就限制了系统性能的上限。SiP(System in Package)封装技术,将多个异构半导体芯片和无源器件封装在一个芯片内,组成一个系统级的芯片,不再使用PCB(Printed Circuit Board)板作为承接芯片连接的载体,从而解决因PCB板自身不足带来系统性能遇到瓶颈的问题。以处理器和存储芯片举例,系统级封装内部的走线密度远远高于PCB板上的走线密度,这样使得系统的性能有巨大的提升。

与SoC(System on Chip/系统级芯片)相比,SiP(System in Package)是从封装的立场出发,对不同芯片进行并排或叠加的封装方式,将多个具有不同功能的有源电子元件与无源器件组装到一起,实现一定功能的单个标准封装件。而SoC是从设计的角度出发,是将系统所需的组件高度集成到一块芯片上。

锐杰微科技(集团)有限公司是一家专业从事高端集成电路封装及测试服务的供应商,主要封装类型包括:FcBGA(Flip Chip Ball Grid Array)、WBBGA(Wire Bond Ball Grid Array)、FcCSP(Flip Chip Chip Scale Package)、FcLGA((Flip Chip Land Grid Array)、Leadframe(框架类)等,提供规模化封装制造及测试业务,以及集成电路芯片封装相关的设计、仿真与工艺开发服务。

针对不同应用场景的需求对客户提供SiP封装定制化解决方案。锐杰微在先进SiP封装方面累积了丰富的设计及工程经验,有大量的成功案例。

锐杰微科技集团在计算机产品、AI 、区块链、物联网、智慧城市、飞控,通信产品,多媒体等产品以及超算,大数据、汽车电子,医疗仪器设备等封装领域提供专业服务,主攻国内客户所对于小型化,轻量化,多功能复杂微系统开展SiP芯片业务。

依托锐杰微科技的设计研发能力以及核心关键裸芯资源,推动SiP芯片研发完成国内大部分商业客户的SiP产品定制需求。开展多种类型,多结构,多用途的SiP产品研发,并申报相关课题及专利,提升产品附加值,满足10年以内SoC无法替代的应用场景和需求。

锐杰微科技同时提供集成电路芯片封装相关的设计、仿真与工艺开发服务。在高端复杂芯片、先进工艺制程上以多应用场景芯片项目为主,积累了丰富的设计及工程经验,同时在新产品、新材料、新结构和新工艺等前沿性领域中开展研究。

公司自创立之初,已经服务了数百家高端客户,完成了几百项高端复杂芯片及SiP封装项目,锐杰微的目标会在未来三年内成为国内最先进的、大规模的专业集成电路封测平台。

锐杰微本着以“品质为本,攻坚克难,勇于创新”的理念,从客户和产品角度出发,跳出传统封装厂单一的组装业务,提供真正满足产品服务的先进封装整体解决方案。

原文标题:先进封装,看这一篇就够了!

文章出处:【微信公众号:ssdfans】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

半导体

+关注

关注

334文章

27339浏览量

218453 -

封装

+关注

关注

126文章

7892浏览量

142937

原文标题:先进封装,看这一篇就够了!

文章出处:【微信号:SSDFans,微信公众号:SSDFans】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

英锐恩科技,以实力打造国产单片机替代品牌!

高可调性材料:Haydale生物传感器油墨,打造灵活定制化印刷解决方案

微导纳米发布先进封装低温薄膜解决方案

展锐平板定制_展锐T618平板电脑国产开发方案

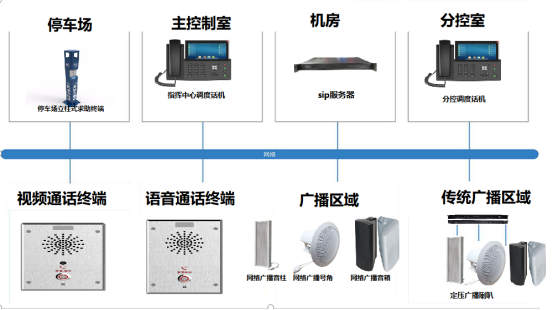

智慧园区sip可视对讲广播解决方案

ENNOVI推出全新定制化汽车以太网连接器解决方案

赛劲SEJINIGB减速机 非标摆线减速机定制化解决方案

Sip技术是什么?Sip封装技术优缺点

智慧园区综合管理系统:定制化解决方案助力工厂园区高效运转

杰华特IMVP9.1电源方案

pda手持终端定制_基于联发科|展锐平台的手持机pda解决方案

锐杰微提供SiP封装定制化解决方案

锐杰微提供SiP封装定制化解决方案

评论