一、ZYNQ基本结构

ZYNQ7000系列分为Artix-7 Kintex-7 Virtex-7,各个型号区别参考下面的博文

https://www.jianshu.com/p/005899fe6815

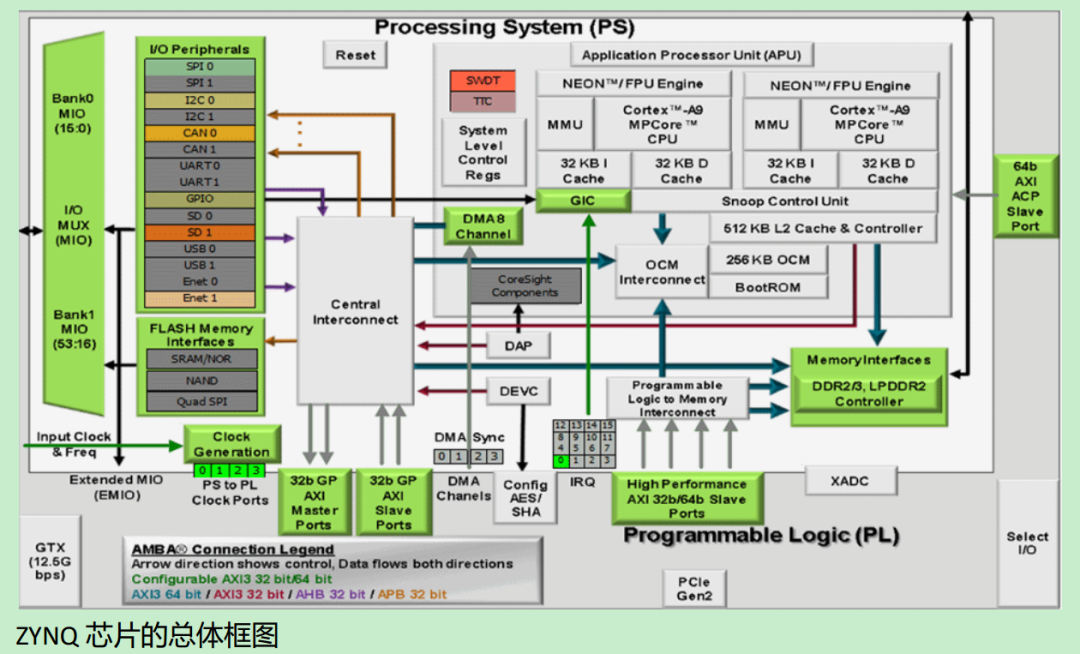

二、ZYNQ7020 分为PS端、PL端

PS: 处理系统 (Processing System) , 就是与 FPGA 无关的 ARM 的 SOC 的部分。

PL: 可编程逻辑 (Progarmmable Logic), 就是 FPGA 部分。

ZYNQ7020的整体架构如下图所示

Zynq 就是两大功能块,PS 部分和 PL 部分, 说白了,就是 ARM 的 SOC 部分,和 FPGA部分。其中,PS 集成了两个 ARM Cortex-A9 处理器,AMBA互连,内部存储器,外部储器接口和外设。这些外设主要包括 USB 总线接口,以太网接口,SD/SDIO 接口,I2C 总线接口,CAN 总线接口,UART 接口,GPIO 等。

三、PS和PL互联技术

3.1、ZYNQ作为首款将高性能ARM Cortex-A9系列处理器与高性能FPGA在单芯片内紧密结合的产品,为了实现ARM处理器和FPGA之间的高速通信和数据交互

3.2、发挥 ARM 处理器和 FPGA的性能优势,需要设计高效的片内高性能处理器与 FPGA 之间的互联通路。本节,我们就将主要介绍 PS 和 PL 的连接,让用户了解 PS 和 PL 之间连接的技术。

3.3、在具体设计中我们往往不需要在连接这个地方做太多工作,我们加入 IP 核以后,系统会自动使用 AXI 接口将我们的 IP 核与处理器连接起来,我们只需要再做一点补充就可以了。

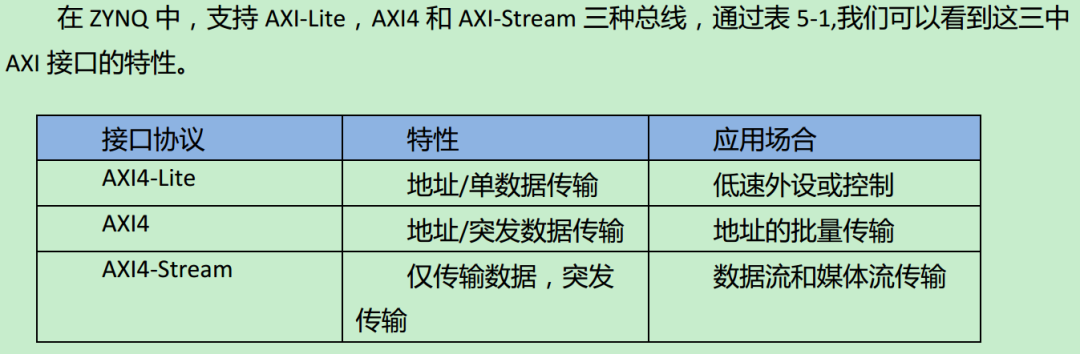

AXI 全称 Advanced eXtensible Interface,是 Xilinx 从 6 系列的 FPGA 开始引入的一个接口协议,主要描述了主设备和从设备之间的数据传输方式。在 ZYNQ 中继续使用,版本是 AXI4,所以我们经常会看到 AXI4.0,ZYNQ 内部设备都有 AXI 接口。

3.4、其实 AXI 就是 ARM 公司提出的AMBA(Advanced Microcontroller Bus Architecture)的一个部分,是一种高性能、高带宽、低延迟的片内总线,也用来替代以前的 AHB 和 APB 总线。

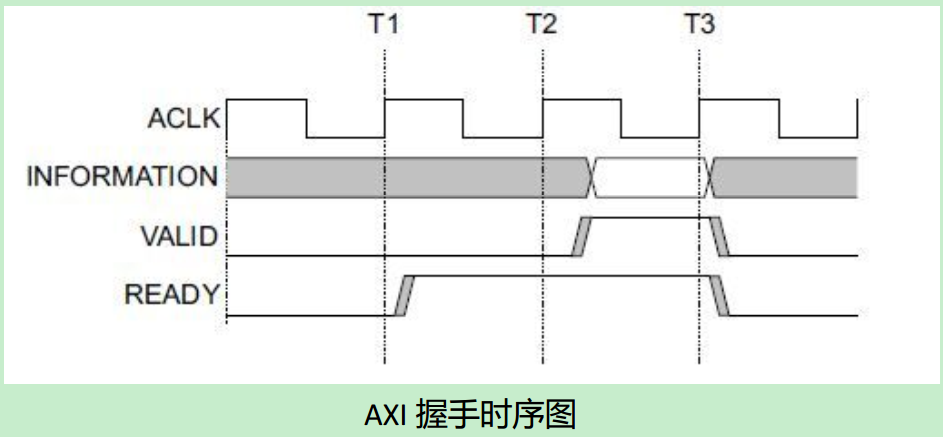

AXI 协议主要描述了主设备和从设备之间的数据传输方式,主设备和从设备之间通过握手信号建立连接。当从设备准备好接收数据时,会发出 READY 信号。当主设备的数据准备好时,会发出和维持 VALID 信号,表示数据有效。数据只有在 VALID 和 READY 信号都有效的时候才开始传输。当这两个信号持续保持有效,主设备会继续传输下一个数据。

3.5、主设备可以撤销VALID 信号,或者从设备撤销 READY 信号终止传输。AXI 的协议如图,T2 时,从设备的 READY信号有效,T3 时主设备的 VILID 信号有效,数据传输开始。

信号有效,T3 时主设备的 VILID 信号有效,数据传输开始。

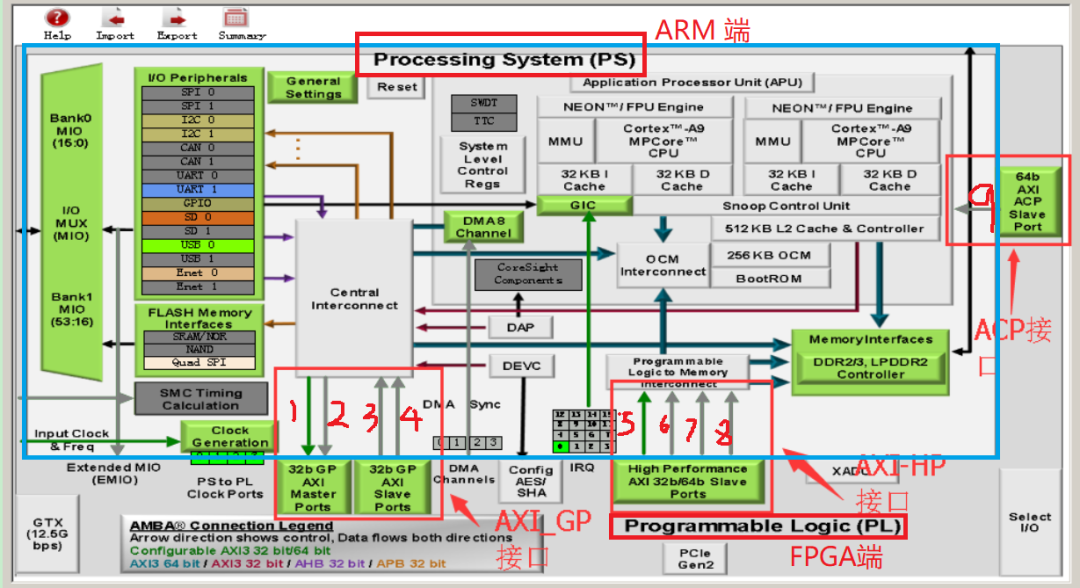

四、ZYNQ 芯片内部用硬件实现了 AXI 总线协议,包括 9 个物理接口,分别为 AXI-GP0~AXIGP3,AXI-HP0~AXI-HP3,AXI-ACP 接口。

1、AXI_ACP 接口,是 ARM 多核架构下定义的一种接口,中文翻译为加速器一致性端口,用来管理 DMA 之类的不带缓存的 AXI 外设,PS 端是 Slave 接口。2、AXI_HP 接口,是高性能/带宽的 AXI3.0 标准的接口,总共有四个,PL 模块作为主设备连接。主要用于 PL 访问 PS 上的存储器(DDR 和 On-Chip RAM)3、AXI_GP接口,是通用的AXI接口,总共有四个,包括两个32位主设备接口和两个32位从设备接口

可以看到,ARM只有两个 AXI-GP 是 Master Port,即主机接口,其余 7 个口都是 Slave Port(从机接口)。主机接口具有发起读写的权限,ARM 可以利用两个 AXI-GP 主机接口主动访问 PL 逻辑,其实就是把 PL 映射到某个地址,读写 PL 寄存器如同在读写自己的存储器。其余从机接口就属于被动接口,接受来自 PL 的读写,逆来顺受。

4.1、这 9 个 AXI 接口性能也是不同的。GP 接口是 32 位的低性能接口,理论带宽600MB/s,而 HP 和 ACP 接口为 64 位高性能接口,理论带宽 1200MB/s。

4.2、有人会问,为什么高性能接口不做成主机接口呢?这样可以由 ARM 发起高速数据传输。答案是高性能接口根本不需要 ARM CPU 来负责数据搬移,真正的搬运工是位于 PL 中的 DMA 控制器。

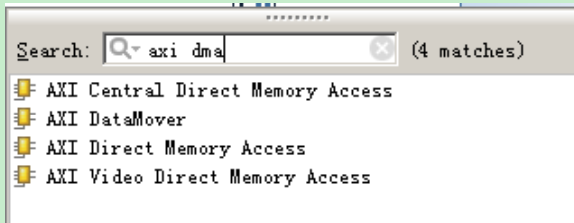

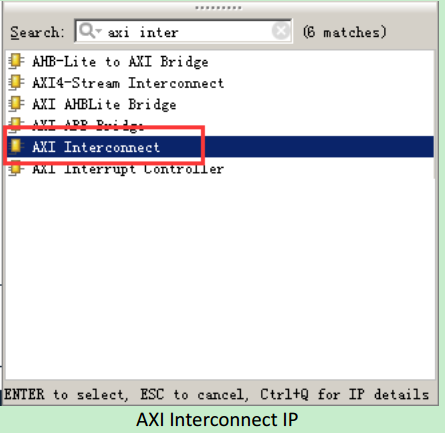

4.3、位于 PS 端的 ARM 直接有硬件支持 AXI 接口,而 PL 则需要使用逻辑实现相应的 AXI 协议。Xilinx 在 Vivado 开发环境里提供现成 IP 如 AXI-DMA,AXI-GPIO,AXI-Dataover, AXI-Stream 都实现了相应的接口,使用时直接从 Vivado 的 IP 列表中添加即可实现相应的功能。下图为 Vivado 下的各种 DMA IP:

下面为几个常用的 AXI 接口 IP 的功能介绍:

AXI-DMA:实现从 PS 内存到 PL 高速传输高速通道 AXI-HP<---->AXI-Stream 的转换AXI-FIFO-MM2S:实现从 PS 内存到 PL 通用传输通道 AXI-GP<----->AXI-Stream 的转换AXI-Datamover:实现从 PS 内存到 PL 高速传输高速通道 AXI-HP<---->AXI-Stream 的转换,只不过这次是完全由 PL 控制的,PS 是完全被动的。AXI-VDMA:实现从 PS 内存到 PL 高速传输高速通道 AXI-HP<---->AXI-Stream 的转换,只不过是专门针对视频、图像等二维数据的。AXI-CDMA:这个是由 PL 完成的将数据从内存的一个位置搬移到另一个位置,无需 CPU 来插手。

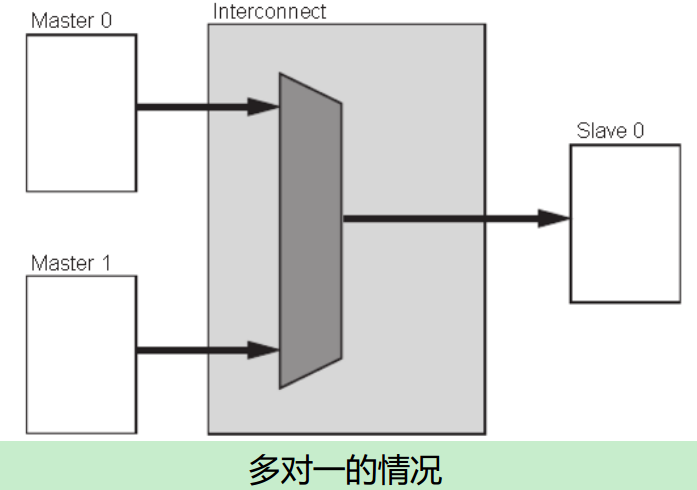

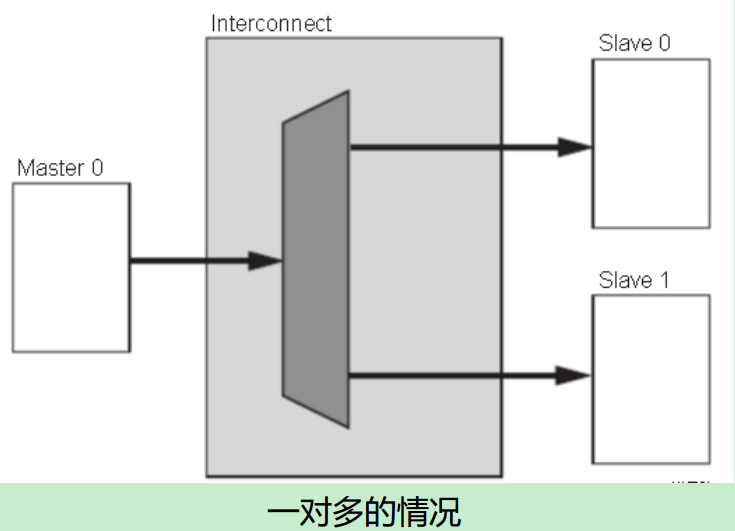

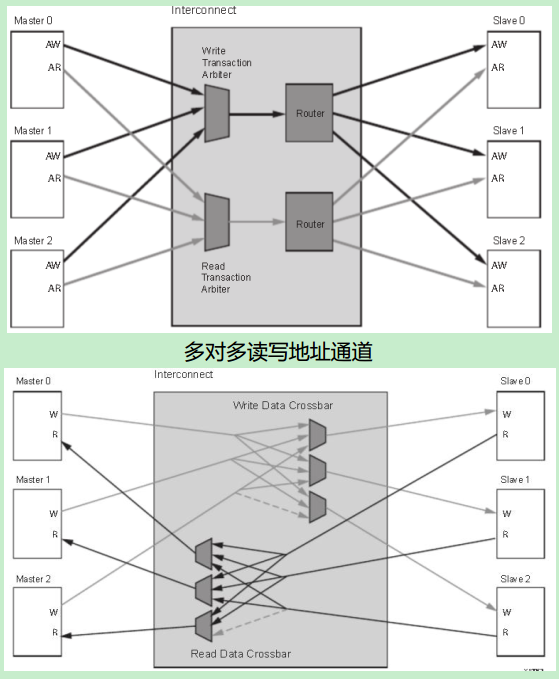

4.4、AXI协议严格的讲是一个点对点的主从接口协议,当多个外设需要互相交互数据时,我们需要加入一个AXI Interconnect模块,也就是AXI互联矩阵,

4.5、作用是提供将一个或多个 AXI 主设备连接到一个或多个 AXI 从设备的一种交换机制(有点类似于交换机里面的交换矩阵)。

4.6、这个 AXI Interconnect IP 核最多可以支持 16 个主设备、 16 个从设备,如果需要更多的接口,可以多加入几个 IP 核。

AXI Interconnect 基本连接模式有以下几种: N-to-1 Interconnect to-N Interconnect N-to-M Interconnect (Crossbar Mode) N-to-M Interconnect (Shared Access Mode)

五、内部链接

ZYNQ 内部的 AXI 接口设备就是通过互联矩阵的的方式互联起来的,既保证了传输数据的高效性,又保证了连接的灵活性。

Xilinx 在 Vivado 里我们提供了实现这种互联矩阵的 IP 核axi_interconnect,我们只要调用就可以。

六、引脚分配

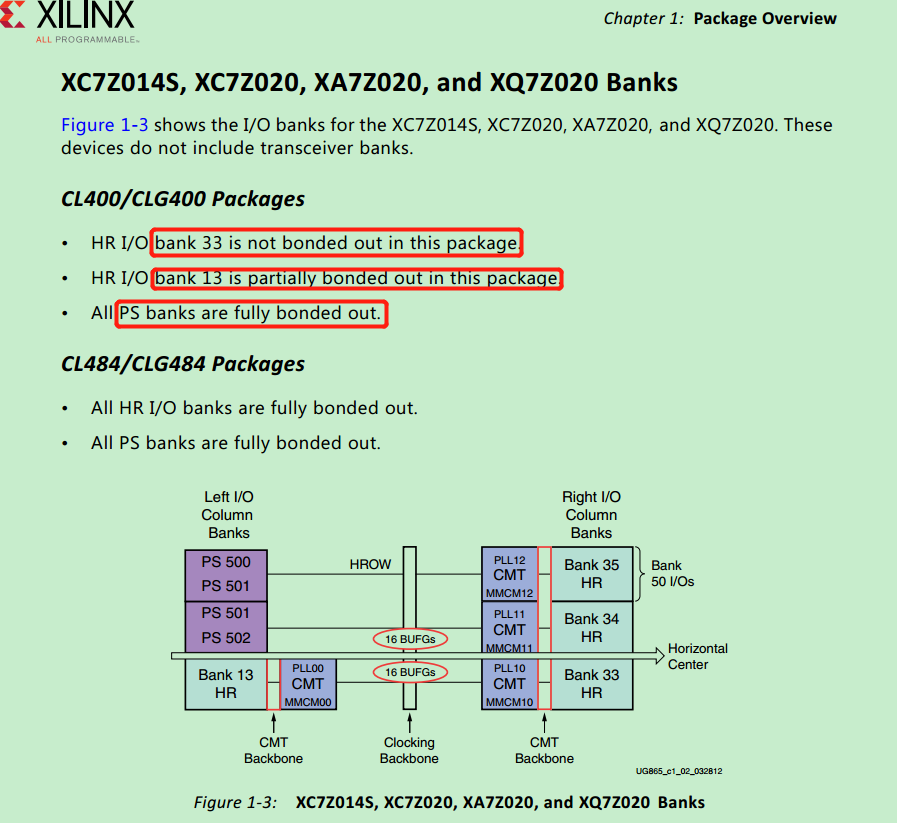

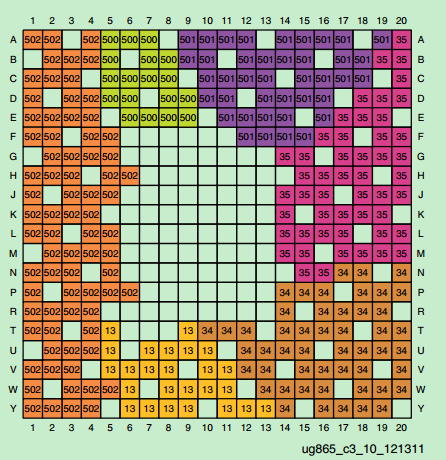

ZYNQ7020是400脚封装,从官网的文档,可以看出ZYNQ7020的引脚分配

PS端的引脚包括BANK500、BANK501、BANK502、

PL端引脚包括 BANK13(部分包含)BANK35、BANK34

下面这张图,更加形象

七、上面的部分,并没有把引脚讲的很清楚,这里看官方手册,有如下描述

意思是,PS端的引脚数量是固定的,并且不能分配给PL端使用,最多有54个引脚可以连接到PS端,

他们可以软件编程连接ps的内部外设或者静态内存控制器

八、MIO概述

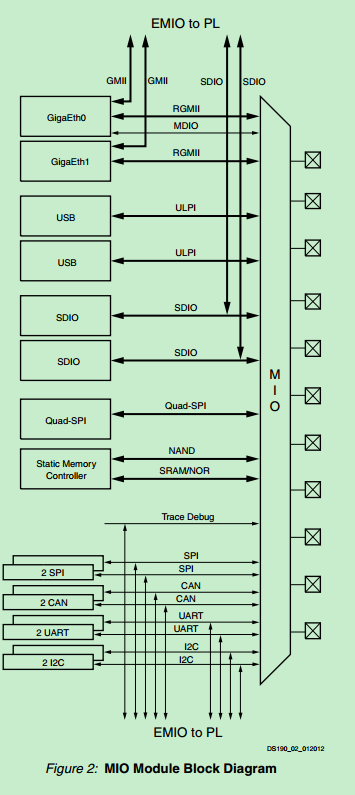

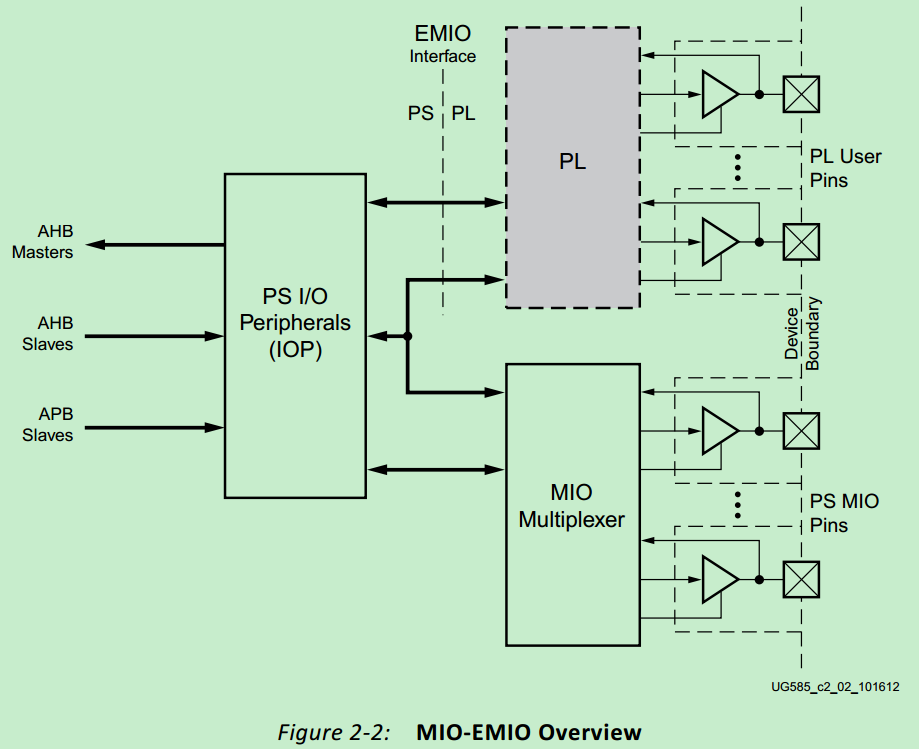

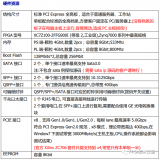

MIO的功能是将从PS外设和静态内存接口的访问,复用到配置寄存器中定义的PS引脚。在PS端最多有54针被用以IOP(I/O Peripheral )和静态内存接口下表4显示了可以映射不同外设引脚的位置。图2显示了MIO模块的框图。如果超过了54个引脚个数的其它I/O功能是设计必须的,那他可以通过PL端,路由到与这些功能相关联的I/O引脚这个特性被称为可扩展多路复用I/O (EMIO)。

九、MIO、EMIO和AXI_GPIO的关系

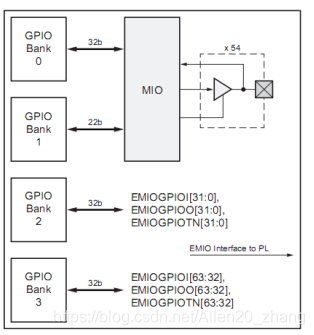

ZYNQ7000中与PS相连的引脚包含MIO、EMIO和AXI_GPIO三种类型。

1、MIO直接挂在PS上,而EMIO与PL相连,PS通过PL调用EMIO。MIO共有54bit,EMIO共有64bit。

MIO管脚是固定的,而EMIO需要通过管脚约束文件进行分配。MIO、EMIO管脚号均通过实际原理图查找。

2、AXI_GPIO是通过AXI总线挂在PS上的GPIO,一般通过调用IP核实现,如PS通过AXI_Uartlite调用PL端资源。

而EMIO在Block Design文件上表现为PS上的一个引出接口。

十、PS-PL MIO-EMIO信号和接口

由于MIO引脚的数量有限,MIO是I/O外围连接的基础。可以软件编程IO信号路由到MIO引脚。也可以通过EMIO接口将I/O外围信号路由到PL端,

这非常有用,用来PS获得更多的设备引脚(PL端引脚),或者允许一个PS端外设的一个引脚路由到PL的内部IP逻辑端口,如图2

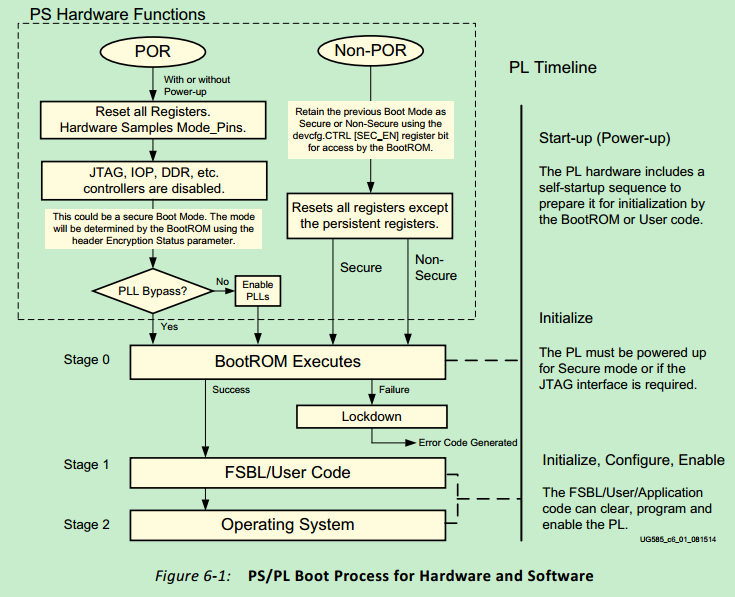

十一、启动流程

12.1、启动模式

Boot 模式3种启动模式可以使用:• PS Master Non-secure Boot• PS Master Secure Boot• JTAG/PJTAG Boot

12.2、启动阶段

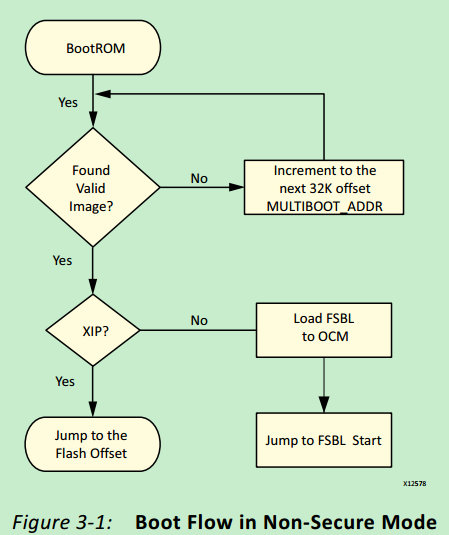

Zynq-7000 AP SoC 支持安全和非安全启动处理,启动分3个阶段 • Stage-0 Boot (BootROM) • First Stage Bootloader • Second Stage Bootloader (Optional)

12.3、阶段0:Stage-0 Boot (BootROM)

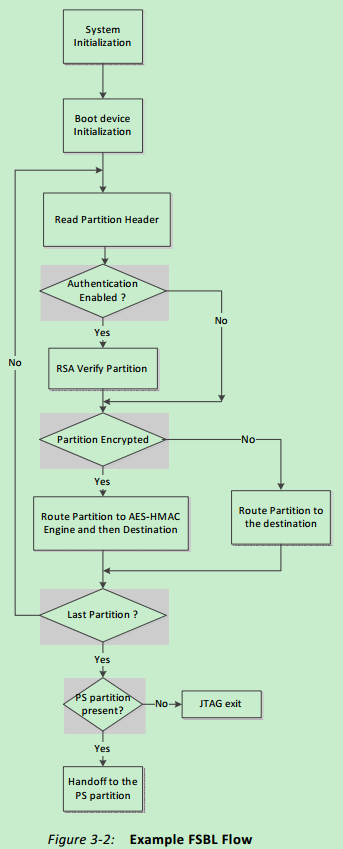

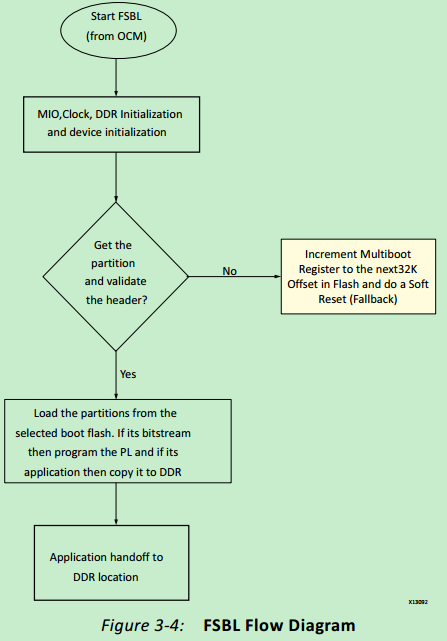

12.4、阶段1:FSBL(First Stage Bootloader )

FSBL(第一阶段引导加载程序)在BootROM之后启动,这个BootROM将FSBL加载到OCM(On-Chip Memory ),

FSBL负责下面的几项工作

1、初始化PS端的配置数据(使用xilinx硬件配置工具提供的)2、用bitstream文件烧写PL端3、加载第二阶段BootLoader或者逻辑代码到DDR内存4、却换到第二阶段BootLoader或者逻辑代码运行

FSBL流程图

下图是一个简单的FSBL流程图:

12.5、第二阶段启动流程:Second Stage Bootloader

第二阶段引导加载程序是可选的,并由用户设计。

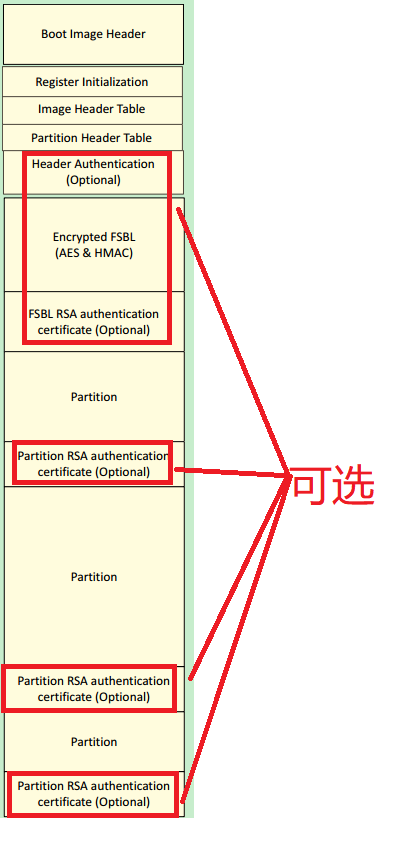

Zynq-7000 AP SoC BootROM加载程序需要引导映像头,它加载单个分区,通常是FSBL。引导映像的其余部分由FSBL加载和处理。

xilinx提供了一个名为Bootgen的实用程序(用来创建一个适合ROM或Fash的引导映像)。它通过构建所需的引导头、

附加描述以下分区的表并将输入数据文件(ELF文件、FPGA bit流和其他二进制文件)处理到分区来创建映像。

12.6、Boot Image 格式

Boot镜像格式包含下面几个方面 • BootROM header • FSBL image • One or more partition images • Unused space, if available

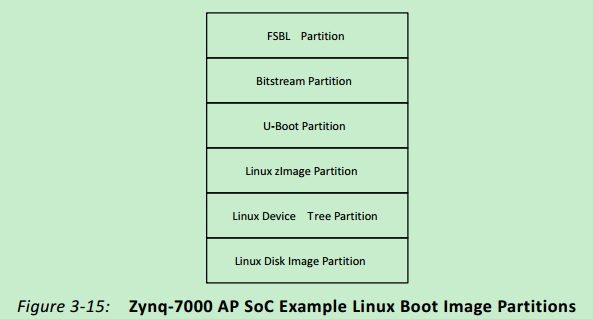

12.7、下图显示了Zynq-7000 AP SoC Linux引导映像分区的示例。

编辑:jq

-

FPGA

+关注

关注

1630文章

21796浏览量

605790 -

ARM

+关注

关注

134文章

9164浏览量

369048 -

soc

+关注

关注

38文章

4199浏览量

219013 -

可编程逻辑

+关注

关注

7文章

517浏览量

44163

原文标题:学员笔记精选 | ZYNQ7000系列 PS、PL、AXI 、启动流程基本概念篇

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

ZYNQ基础---AXI DMA使用

基于Xilinx ZYNQ7000 FPGA嵌入式开发实战指南

dac3174与xilinx zynq7000系列连接,fpga的案例参考代码有没有?

zynq7000 BSP无法在u-boot加载运行怎么解决?

正点原子ZYNQ7015开发板!ZYNQ 7000系列、双核ARM、PCIe2.0、SFPX2,性能强悍,资料丰富!

zynq7000 BSP无法在u-boot加载运行,为什么?

[XILINX] 正点原子ZYNQ7035/7045/7100开发板发布、ZYNQ 7000系列、双核ARM、PCIe2.0、SFPX2!

有关PL端利用AXI总线控制PS端DDR进行读写(从机wready信号一直不拉高)

Xilinx ZYNQ 动手实操演练

Zynq-7000为何不是FPGA?

ZYNQ7000系列 PS、PL、AXI 、启动流程基本概念

ZYNQ7000系列 PS、PL、AXI 、启动流程基本概念

评论