随着后疫情时代的来临,大多数人依然在采用线上视频会议的工作方式 但是您是否曾经想过 所有会议内容和数据的传输需要怎样的技术? 面对疫情造成的前所未有的视频流量激增 数据中心运营商也开始重新思考其当前架构并探索在本质上更便于扩展且效率更高的新配置在此背景下 一种有望大幅提升资源利用率的新架构正在兴起 这就是“可组合式基础设施”

可组合式基础设施

可组合式基础设施能够解耦资源并将资源汇集,从而实现了资源的随处调用。它还能为工作负载提供数量恰好的资源,并经由软件迅速完成重新配置。 可组合式基础设施由 CPU 池、SSD 池和加速器池构成,它们互联在一起并由基于标准的配置框架控制,能极大提高数据中心的资源利用率。在这样的架构中,不同的工作负载可能有不同的计算、存储和加速要求,而资源将进行相应分配,避免浪费硬件资源。

时延挑战

上述方法在理论上似乎很完美,但实际上存在一个严重的问题:时延。当您分解资源并将它们移得更远的时候,就会因 CPU 和 SSD 或 CPU 与加速器之间的网络流量而导致延迟增大和带宽缩小。除非您有某种方法来减少网络流量并提高资源间的互联效率,否则这会造成严重的限制。在解决时延难题方面,FPGA 能发挥三大关键作用:

将 FPGA 作为灵活应变的加速器,针对每种工作负载进行定制以实现最佳性能;

FPGA 让算力贴近数据,从而降低时延,并最大限度缩小所需带宽;

FPGA 的灵活应变智能架构能够在不产生额外延迟的情况下实现资源的高效率池化。

灵活应变的加速

基于 FPGA 的计算加速器的第一大优势就是显著提升如今亟需的工作负载的性能。在实时视频流应用的视频转码用例中,FPGA 解决方案的性能通常比 x86 CPU 高出 30 倍,这有助于数据中心运营商解决并发流大幅增加的问题。另一个示例是在基因组测序的关键领域。一位近期成为赛灵思客户的基因组研究机构发现,基于赛灵思 FPGA 的加速器能以比 CPU 快 90 倍的速度获得结果,帮助医疗研究人员以过去几分之一的时间完成 DNA 样本测试。

让算力更贴近数据

可组合式数据中心内的 FPGA 能发挥的第二大优势是,让灵活应变的算力贴近数据。在 SmartSSD 计算存储器件中使用赛灵思 FPGA,能为过去一般由 CPU 运行的高速搜索、解析、压缩和加密等功能提速。这有利于卸载 CPU,将其用于更复杂的任务,而且还有助于减少 CPU 和 SSD 之间的流量,从而减少带宽消耗并降低时延。 与之类似,赛灵思 FPGA 现在也用在 SmartNIC 中。例如赛灵思新款 Alveo SN1000,它不仅能为活动数据加速,提供线速数据包处理、压缩和加密服务,还能针对特定数据中心或客户适应定制的切换要求。

智能架构

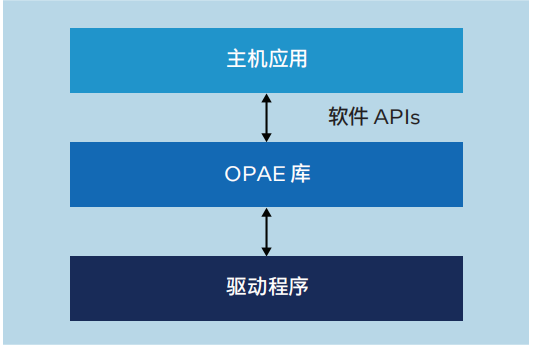

如果将 FPGA 灵活应变的计算加速与低时延连接结合,便会使得可组合式数据中心更进一步。您可以将高计算强度的工作负载分配给采用自适应智能架构互联的加速器集群,按需创建高性能计算机。 当然,如果不能以最优加速算法为计算加速器、SmartSSD 和 SmartNIC 编程,然后按正确数量将它们配置给每个工作负载,那么这些好处都是空谈。在这方面,我们已经开发出一个综合全面的软件协议栈,它利用 TensorFlow 和 FFMPEG 等特定领域行业框架,并配合赛灵思的 Vitis 开发平台运行。在智能资源分配方面, RedFish 等更高级的配置框架也有用武之地。 在可组合式数据中心掀起的激动人心的变革中 赛灵思器件和加速器卡将成为新型高效架构的关键模块依托快速的可重配置能力、低时延以及能够适应不断变化的工作负载的灵活架构赛灵思已经为在这场变革中发挥重大作用做好准备

原文标题:可组合数据中心:让算力更贴近数据

文章出处:【微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

FPGA

+关注

关注

1628文章

21723浏览量

602897 -

数据

+关注

关注

8文章

6992浏览量

88935

原文标题:可组合数据中心:让算力更贴近数据

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

2.34纳秒超低时延,满足金融市场高频交易,AMD发布新一代金融加速卡

FPGA加速深度学习模型的案例

应变片的灵敏系数是什么,它与电阻丝连接方式

FPGA在人工智能中的应用有哪些?

基于FPGA的类脑计算平台 —PYNQ 集群的无监督图像识别类脑计算系统

电阻应变片的连接方式有哪些?

借助全新 AMD Alveo™ V80 计算加速卡释放计算能力

将FPGA灵活应变的计算加速与低时延连接结合

将FPGA灵活应变的计算加速与低时延连接结合

评论