俗话说,一画胜千言;由此推算,一段视频足以洞若观火。

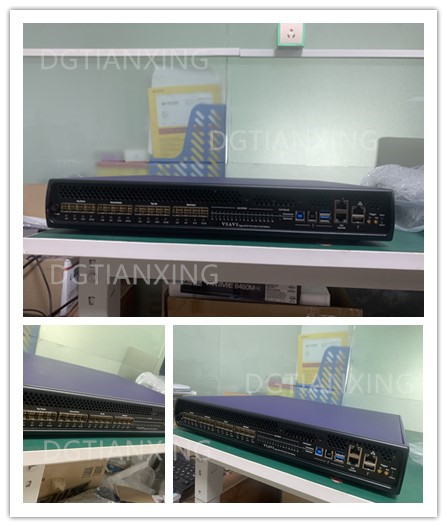

Cadence 发布了面向 PCI Express (PCIe) 5.0 系统的 SoC 硅芯片演示视频,这个视频将向您介绍我们如何把最前沿的技术应用到 TSMC 先进 FinFET 工艺上,为市场带来一款极具竞争力的低功耗解决方案,并采用业界最新的测试方案进行测试。

这一 PCIe 系统解决方案由 Cadence PCIe 5.0 的 PHY 和双模(支持 RC 和 EP)控制器组成,同时我们在硅芯片中实现和验证了高达 8-lane 的链路宽度。

在过去的 PCIe 规范下,测试由 PHY 的硅芯片和基于 FPGA 的控制器组成的 PCIe 系统是可行的。

但是,随着协议所需带宽的增加,PHY 与控制器间的 PIPE 接口速度越来越快,以及控制器本身也需要以更高的速度运行,基于 FPGA 的多通道满速运行解决方案变得越来越不切实际。

通过 SoC 硅芯片来验证完整的 PCIe 协议栈充分展示出 Cadence 作为一家 IP 提供商值得信赖的交付能力。

迄今为止,Cadence 已经为多代 PCIe 协议开发了完整的解决方案。

完整的片上子系统让我们可以轻松地在现已问世的服务器平台上进行测试,这一点对新标准的开发至关重要。

Cadence 正准备向客户与合作伙伴开放这一平台。

与业界合作伙伴共同展开硅片测试

测试服务供应商正在基于我们的 SoC 芯片来积极评估新标准下的测试方案和产品。

同时我们已经使用这一 SoC 平台在目前已经问世的先进平台上成功测试了关键参数的合规性。

我们期待在更多的服务器平台问世后,继续进行更广泛的互联互通测试。面向 PCIe 5.0 的官方合规项目将在未来一年或稍晚启动,让我们拭目以待!

原文标题:首睹真容:面向PCIe 5.0的Cadence子系统SoC演示

文章出处:【微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

芯片

+关注

关注

455文章

50738浏览量

423297 -

soc

+关注

关注

38文章

4163浏览量

218184 -

Cadence

+关注

关注

65文章

921浏览量

142092

原文标题:首睹真容:面向PCIe 5.0的Cadence子系统SoC演示

文章出处:【微信号:gh_fca7f1c2678a,微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

KeyStone设备的PCI Express (PCle)常见问题

VIAVI Xgig 4K16 PCI Express 4.0 协议分析仪平台介绍

使用TI PCI-Express Gen5.0转接驱动器进行眼图扫描

Cadence展示完整的PCIe 7.0 IP解决方案

DS50PCI401 2.5 Gbps/5.0 Gbps 4通道PCI Express中继器数据表

DS50PCI402 2.5 Gbps/5.0 Gbps 4通道PCI Express中继器数据表

Cadence扩充系统IP产品组合,推出NoC以优化电子系统连接性

DS80PCI402具有均衡和去加重功能的2.5Gbps/5.0Gbps/8.0Gbps 4通道PCI-Express中继器数据表

XIO2001 PCI Express至PCI总线转换桥接器数据表

Teledyne LeCroy扩展CrossSync PHY技术到PCI Express 6.0

M31推出PCI-SIG的官方认证PCIe5.0 PHY IP 携手SSD存储芯片公司InnoGrit推进PCIe5.0新世代

Cadence演示面向PCI Express 5.0系统的SoC硅芯片

Cadence演示面向PCI Express 5.0系统的SoC硅芯片

评论