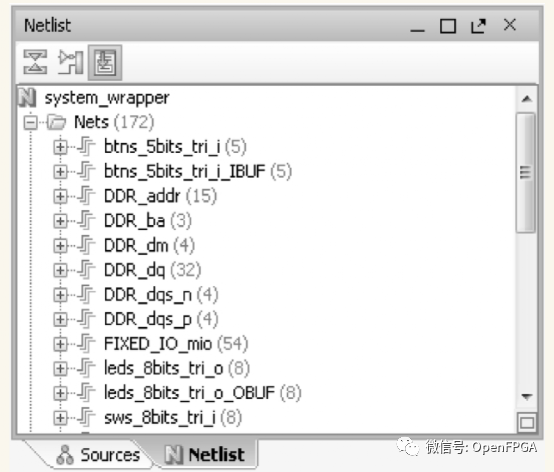

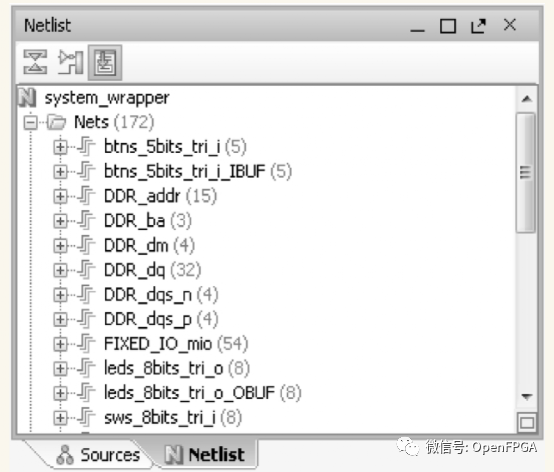

我们都知道FPGA的实现过程分为2步:分析综合与布局布线后就可以产生目标文件,这两个步骤中间有个非常重要的文件,那就是-网表。 下图是Vivado中网表列表示例:

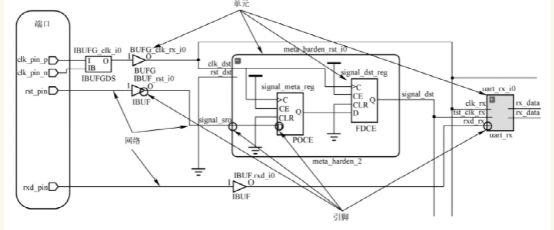

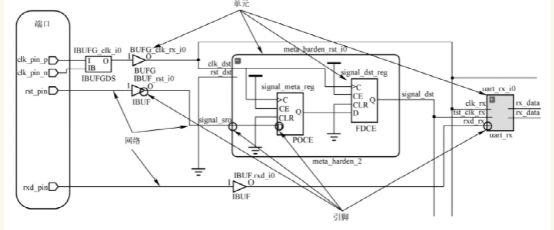

Vivado中网表列表示例 在vivado集成环境中,网表时对设计的描述,如网表由单元(cell)、引脚(pin)、端口(port)和网络(Net)构成。下图是一个电路的网表结构:

电路的网表结构

(1)单元是设计单元

1、设计模块(Verilog HDL)/实体(VHDL)。

2、元件库中的基本元素(Basic Elements ,BLEs)实例。如LUT、FF、DSP、RAM等。

3、硬件功能的类属表示。

4、黑盒。

(2)引脚是单元上的连接点

(3)端口是设计的顶层端口

(4)网络用于实现引脚之间,以及引脚到端口的连接。

编辑:jq

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

原文标题:【Vivado那些事】Vivado中电路结构的网表描述

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

相关推荐

输入图像的内容。 RNN的基本原理 RNN是一种用于处理序列数据的神经网络,它通过循环结构来处理序列中的每个元素,并保持前一个元素的信息。RNN的主要特点是它能够处理任意长度的序列,并且能够捕捉序列中的时间依赖关系。RNN的基本

![的头像]() 发表于

发表于 11-15 09:58

•298次阅读

后的约束在之前版本中已存在,那么Vivado会给出警告信息,显示这些约束会覆盖之前已有的约束;如果是新增约束,那么就会直接生效。

![的头像]() 发表于

发表于 10-24 15:08

•355次阅读

以太网帧(Ethernet Frame)是以太网(Ethernet)协议用于在局域网(LAN)中传输数据的基本单位。理解以太网帧的

![的头像]() 发表于

发表于 10-08 10:00

•1155次阅读

从综合角度看,Vivado 2024.1对SystemVerilog和VHDL-2019的一些特性开始支持。先看SystemVerilog。

![的头像]() 发表于

发表于 09-18 10:34

•933次阅读

Vivado 2024.1已正式发布,今天我们就来看看新版本带来了哪些新特性。

![的头像]() 发表于

发表于 09-18 10:30

•1394次阅读

生成PCB网表是电路设计过程中的一个重要步骤,它将电路原理图转换为PCB布局所需的连接信息。AD(Altium Designer)软件是一款

![的头像]() 发表于

发表于 09-02 16:17

•2133次阅读

时序逻辑电路是数字电路中的一种重要类型,它具有存储和处理信息的能力。时序逻辑电路的描述方法有很多种,不同的方法适用于不同的设计和分析场景。以

![的头像]() 发表于

发表于 08-28 11:39

•1426次阅读

时序逻辑电路是数字电路中的一种重要类型,它具有存储功能,能够根据输入信号和内部状态的变化来改变其输出。时序逻辑电路广泛应用于计算机、通信、控制等领域。本文将介绍时序逻辑

![的头像]() 发表于

发表于 08-28 11:37

•667次阅读

钳形电流表,又称钳表,是一种专为电气线路电流测量设计的计量仪器。其独特的结构和工作原理使得它能在不断开电路的情况下,直接测量正在运行的电气线路的电流大小。本文将从钳形电流

![的头像]() 发表于

发表于 05-14 16:14

•3093次阅读

Verilog与VHDL语法是互通且相互对应的,如何查看二者对同一硬件结构的描述,可以借助EDA工具,如Vivado,打开Vivado后它里面的语言模板后,也可以对比查看Verilog

![的头像]() 发表于

发表于 04-28 17:47

•2530次阅读

,用户可直接在simulink下综合出网表和约束文件,打包至.dcp文件中,用户可在vivado下直接加载dcp文件调用模型。

4、直接在viva

发表于 04-17 17:29

由实现组合电路的查找表,实现时序电路的触发器,以及数据选择器构成。数据选择器在存储单元 M0 的控制下决定直接输出查找表的值还是输出 FF 中

发表于 04-03 17:39

以太网的组网结构涉及多个层面和组件。首先,从网络结构的角度来看,以太网分为物理层、数据链路层和高层用户层。其中,物理层采用特定的通信媒体,如50Ω基带同轴电缆,实现数据的传输。数据链路

![的头像]() 发表于

发表于 03-08 17:19

•3373次阅读

在Vivado中禁止自动生成BUFG(Buffered Clock Gate)可以通过以下步骤实现。 首先,让我们简要了解一下什么是BUFG。BUFG是一个时钟缓冲器,用于缓冲输入时钟信号,使其更稳

![的头像]() 发表于

发表于 01-05 14:31

•2223次阅读

有些时候在写完代码之后呢,Vivado时序报红,Timing一栏有很多时序问题。

![的头像]() 发表于

发表于 01-05 10:18

•2207次阅读

Vivado中电路结构的网表描述

Vivado中电路结构的网表描述

评论