近日,台积电发布了该公司2020年年度财报。正如该公司联席CEO在致股东说明书中所说,对于台积公司而言,2020年是深具挑战的一年,但也是显著成长与进步的一年。面临全球COVID-19疫情带来的动荡与地缘政治的紧张局势,台积电与客户积极合作,并且加强技术领先、卓越制造,以及客户信任的承诺。

受惠于客户对于台积电领先业界的5纳米(N5)及7纳米(N7)技术的强劲需求,台积公司的营收连续11年缔造了历史新高的纪录,以美金计算,台积电在2020年的营收同比增长了31.4%。作为对比,全球半导体产业较前一年成长约10%。

台积电方面继续表示,,在5G及高效能运算(HPC)应用的产业大趋势驱动之下,使半导体芯片内含量得到提升,台积公司将当年度资本支出增加至172亿美元。由于台积公司进入了另一波更高的成长期,公司将会持续投资以掌握随之而来的商机。

在这份年度财报中,台积电还对公司的市场、技术和未来发展进行了深入探讨,本文摘录如下,以飨读者:

台积电的业绩表现

首先看财报方面,以美元计算,台积2020年的全年合并营收为455亿1,000万美元,税后净利为176亿美元,较前一年度的全年合并营收346亿3,000万美元增加31.4%,较前一年度的税后净利111亿8,000万美元增加了57.5%。

来到毛利率方面,据介绍,台积电在2020年获得了53.1%的利润率,而前一年这项数据为46.0%;营业利益率为42.3%,前一年则为34.8%。税后纯益率为38.7%,也较前一年的税后纯益率32.3%增加了6.4个百分点。

在客户合作方面,台积电方面表示,公司在2020年可以提供281种不同的制程技术,为510个客户生产1万1,617种不同的产品,应用范围涵括整个电子应用产业,包括于个人计算机与其周边产品、信息应用产品、有线与无线通讯系统产品、服务器与数据中心、汽车与工业用设备,以及包括数位电视、游戏机、数位相机等消费性电子、人工智能物联网及穿戴式装置,与其他许多产品与应用。

台积电继续指出,公司积极布局全球各国专利,以质量并重为核心管理原则。在专利申请数量上,截至2020年年底,台积公司在全球专利申请总数已累积超过6万2,000件,包括2020年申请6,900件专利;在美国申请数名列专利申请人排行榜第三名,创历史新高纪录;且在台湾的专利申请数亦连续五年位居全岛第一。在专利获准数量上,截至2020年年年底,台积公司在全球总数已累积超过4万5,000件,包括2020年取得超过4,500件全球专利,其中美国专利超过2,800件,名列美国专利权人第八名。

据总结,台积公司在2020年的主要成就包括:

首先,台积电在2020年的晶圆出货量等效于1,240万片十二吋晶圆,而2019年这个数字约为1,010万片十二吋晶圆。

这主要得益于台积电台湾公司的四座十二吋超大晶圆厂(GIGAFAB Facilities)、四座八吋晶圆厂和一座六吋晶圆厂,并拥有一家百分之百持有之海外子公司—台积电(南京)有限公司之十二吋晶圆厂及二家百分之百持有之海外子公司—WaferTech美国子公司、台积电(中国)有限公司之八吋晶圆厂产能支援。

台积电进一步指出,公司四座超大晶圆厂的总产能已超过900万片十二吋晶圆。晶圆十二厂、晶圆十四厂和晶圆十五厂目前提供0.13微米、90纳米、65纳米、40纳米、28纳米、20纳米、16纳米、10纳米和7纳米全世代以及其半世代设计的生产,目前5纳米正在晶圆十八厂加速量产中。

此外,为提供更先进的制造技术,公司亦在晶圆十二厂建置部分产能作为研发用途,以支援3纳米、2纳米及更先进制程的技术发展。

其次,拥有最先进的制程技术是台积公司在专业集成电路制造服务领域取得强大市场地位的重要关键。2020年,台积电有58%的晶圆营收来自先进制程技术(16纳米及以下更先进制程),高于2019年的50%。值得一提的是,台积公司占全球半导体(不含存储器)产值的24%,在2019年,这个数字为21%。

台积电逻辑技术的进展

根据财报,在2020年,台积电持续投资研究与开发,全年研发总预算约占总营收之8.2%,此一研发投资规模相当或超越了许多其他高科技领导公司的规模。台积电进一步指出,为了延续每二年半导体运算能力增加一倍之摩尔定律所面临的技术挑战日益困难,公司研发组织的努力着重于让台积公司能够提供客户率先上市且先进的技术和设计解决方案,帮助客户取得产品的成功。

台积电在财报中指出,在2020年,随着5纳米技术的移转及量产,公司的研发组织持续推动技术创新以维持业界的领导地位。当台积公司3纳米技术,作为第六代三维晶体管技术平台,持续全面开发,并与主要客户完成I设计及开始进行验证的同时,台积公司已开始全面开发领先半导体业界的2纳米技术,同时针对2纳米以下的技术进行探索性研究。

据台积电总结显示,在2020年获得的技术成果,公司在逻辑方面取得了以下多个方面的进展:

1、3纳米制程技术

台积电在2020年的研发着重于3纳米制程技术基础制程制定、良率提升、晶体管及导线效能改善,以及可靠性评估。相较于5纳米制程技术,3纳米制程技术显著地改善芯片密度,在相同的功耗下提供更好的效能,或在相同的效能下提供更低的功耗。

据台积电透露,公司主要客户已于2020年完成3纳米IP的设计,并开始进行验证。台积公司预计于2020年完成3纳米制程技术验证以进入试产。

2、2纳米制程技术

2nm方面,台积电于2020年初步研究及路径寻找之后,已进行2纳米制程技术的研发阶段,着重于测试键与测试载具之设计与实作、光罩制作以及硅试产。

3、微影技术

台积电表示,公司微影技术在2020年的研发重点在于3纳米技术、2纳米技术开发和下一世代纳米技术开发的先期准备。针对3纳米技术的开发,极紫外光(EUV)微影技术展现极佳的光学能力,与符合预期的芯片良率。研发单位正致力于极紫外光技术,以减少曝光机光罩缺陷及制程堆栈误差,并降低整体成本。

台积电表示,2020年,公司的2纳米及更先进制程上将着重于改善极紫外光技术的质量与成本。台积公司的极紫外光项目在光源功率及稳定度上有持续性的进展,光源功率的稳定与改善得以加快先进技术的学习速度与制程开发。此外,极紫外光光阻制程、光罩保护膜及相关的光罩基板也都展现显著的进步,极紫外光技术已全面量产。

4、光罩技术

光罩技术在先进微影技术中极为关键。2020年,公司研发组织成功完成3纳米制程光罩技术开发,大量导入更复杂且先进的极紫外光光罩技术,且持续精进极紫外光光罩技术,以满足2纳米微影技术在光罩上的需求。

5、导线与封装技术整合

晶圆级系统整合技术(WLSI)在日益复杂的应用领域中藉由混合与匹配不同平台而迅速发展。这些包含在晶圆级系统整合范围内的技术被命名为3DFabric,因为它能够实现精细间距的芯片到芯片连接,以及利用现有晶圆制程的统合制造理念。

在3DFabric下,先嵌入芯片再做导线互连的所有制程都称为整合型扇出(InFO)。而先做线路重布层(RDL),然后再将芯片嵌入预制的RDL上就称为CoWoS(Chip-on-Wafer-on-Substrate)。这个新的命名系统真实反映了制程的本质并指向将来的技术推进轨迹。与同级制程系统整合芯片(System on Integrated Chips, SoIC)、SoW(System on Wafer)和SoIS(System on Integrated Substrate)结合在一起,它们形成了通用的晶圆级系统整合技术家族,将推动产业界在面对更具挑战和多样化的运算系统整合需求下,满足未来的系统级微缩需求。

6、三维集成电路(3DIC)与系统整合芯片(TSMC-SoIC)

系统整合芯片(TSMC-SoIC)是创新的晶圆级前段三维芯片(3DIC)堆栈平台,具有卓越的接合密度、互连频宽、功耗效率和薄形轮廓,可透过系统级微缩来延续摩尔定律,具有持续性的效能提升和成本优势。系统整合芯片接下来可以使用传统封装或台积公司新的3DFabric技术,

例如CoWoS或整合型扇出来做封装,支援下一代高效能运算(HPC)、人工智能(AI)和行动应用产品。目前台积公司已使用微米级接合间距制程完成了芯片对晶圆(Chip on Wafer, CoW)和晶圆对晶圆(Wafer on Wafer, WoW)堆栈制程的验证,具有令人满意的电性良率和可靠性结果。

台积公司将继续追求系统整合芯片技术的微缩,以与台积公司先进的硅技术保持一致,进一步提高晶体管密度、系统功耗、性能和面积(Power, Performance, Area,PPA)与成本竞争力。

7、后芯片(Chip Last)CoWoS含有硅中介层的CoWoS是针对高端高效能运算与人工

智能产品应用的2.5D领先技术。此技术具有一个大型的硅中介层,该中介层具有次微米级的绕线层和整合电容(integrated capacitors, iCap),因此可以在其上面放置系统单芯片(SoC)和高频宽存储器(HBM)等各种小芯片。正在开发的第五代CoWoS具有创纪录的硅中介层面积,高达2,400平方毫米,相当于三个全光罩(full-reticle)尺寸。此技术预计于2021年上半年完成验证。

8、先芯片(Chip-First)整合型扇出(InFO)

2020年,台积公司持续领先全球大量生产第五代整合型扇出层叠封装技术(InFO-PoP Gen-5)以支援行动应用,并大量生产第二代整合型扇出暨基板封装技术(InFO-oS Gen-2)支援高效能运算晶粒分割的应用。

第六代InFO-PoP已成功通过认证支援行动应用和增强散热性能。如期开发完成的第三代InFO-oS提供了更多的芯片分割,整合于更大的封装尺寸和更高的频宽。为了满足HPC应用的需求,台积公司开发了超高频宽整合型扇出暨局部硅互连技术(InFO Local Silicon Interconnect, InFO_LSI),其中系统单芯片小芯片(Chiplet)藉由超高密度局部硅互连(LSI)整合到三维InFO封装中。无基板InFO使用多芯片异质整合与更细间距的芯片到芯片互连技术,已成功完成验证以满足消费性电子产品的应用。

最新一代整合式被动元件技术(Integrated Passive Device, IPD)提供高密度电容器和低有效串联电感(Effective Series Inductance, ESL)以增强电性,并已在InFO-PoP上通过认证。AI与5G行动应用将受惠于此增强的InFO-PoP技术。最新一代IPD预计于2021开始大量生产。

9、先进导线技术

台积公司提供创新的技术让互连导线可以持续微缩同时也兼顾芯片效能。2020年,公司提出全新未来互连导线的架构。在极小尺寸之下,这个新的架构可以克服铜金属回填技术上的困难,同时显著地降低导线的电阻跟电容。开发这些创新的解决方案,协助台积公司延续其制程技术的全球领先地位。

值得一提的是,台积电除了持续发展技术以外,公司还聚焦在先进技术研究方面投入。

台积电表示,元件及材料的创新,持续提升先进逻辑技术的效能并降低功耗。2020年,台积公司在二维材料及纳米碳管晶体管的研究持续走在业界前端。台积公司在完整二吋晶圆上成功展示了一个合成单原子层厚单晶的六角斜方氮化硼(hexagonal Boron Nitride, hBN)的制程,这是一个重要的成就,因为hBN已显示为二维材料元件通道的理想钝化层。此杰出的基础研究成果发表于2020年三月全球领先科学期刊之一的《自然》(Nature)。

在2020年举行的超大型集成电路技术研讨会(Symposia on VLSI Technology),台积公司展示了使用化学气相沉积二硫化钼单原子层的二维材料晶体管,在汲极壹伏特操作电压下有最高的二维材料n通道场效晶体管电流。

台积公司也在2020年举行的国际电子元件会议(International Electron Device Meeting, IEDM)介绍了一种新颖的薄膜界面介电层(ILX),它可以在纳米碳管表面成核并均匀地长出小于0.5纳米的薄膜,因而可以使用惯用的原子层沉积技术沉积纳米碳管晶体管的high-k闸极介电层(二氧化铪)。使用这个新颖的ILX,闸极长度微缩到15纳米的上方闸极控制纳米碳管晶体管,展示了接近理想的闸极控制。

台积公司持续寻找并探索支援人工智能和高效能运算应用的新兴高密度、非挥发性存储器硬件加速器。台积公司的先进技术研究处于最佳的位置,为持续一个技术制程接一个技术制程密度增加、提升效能、降低功耗铺路,如同过去所做。

台积电的特殊工艺制程

在上一个章节,我们主要介绍了台积电在逻辑电路方面的进展。但作为晶圆代工巨头,台积电其实在特殊工艺制程方面,也取得了不错的成绩。

1、混合讯号/射频

2020年,台积公司成功开发以3纳米IP及以电磁模拟为基础的LC振荡器设计解决方案,满足高速SerDes电路设计的需求,此解决方案能协助电路设计人员缩短设计周期,并针对不同金属层组合,提供LC振荡器元件及电路布局之全方位服务。

据他们介绍,2020是第一年终端使用者开始受惠于五代行动通讯技术(5G)网络的高传输速度、低延迟以及巨量物联网连结的优势,为了提升5G的成本与受益比,台积公司提供各式7纳米及6纳米的射频元件,以符合客户在收发器设计的需求。藉由增强射频切换器的效能,台积公司开发40纳米特殊制程支援频率6GHz以下应用的5G射频前端模块设计。针对较高频段的毫米波设计,台积公司亦提供28纳米高效能精简型强效版制程(28HPC+),增强功率放大器的效能,应用于5G毫米波前端模块设计。

2、电源IC/双极-互补金属氧化半导体-双重扩散金属氧化半导体(BCD)

2020年,台积公司扩大其十二吋BCD技术的制程范畴,涵盖90纳米、55纳米以及22纳米,以因应快速成长的行动电源管理芯片应用,包括不同的整合度,以及特别的功耗成长需求。90纳米BCD技术支援5伏到35伏的广泛应用,将于2021年持续扩充。

3、面板驱动

2020年,台 积 公司 开 发 晶 圆 堆 叠(WoW 28HPC/40HV)技术,相较于28HPC+,具有相似的稳定产品良率,且降低60%功耗。同时,28HV单芯片技术完成了客户IP验证以及128Mb SRAM良率验证。这些技术是支援小尺寸面板4K分辨率、有机发光二极管(OLED)和120Hz显示驱动IC的领先技术。

此外,台积公司完成OLED在硅产品验证并导入AR/VR应用的量产,具有优异的量产良率与照明均匀性。2021年,台积公司规划推出此技术的改良版,采用8伏晶体管提升晶圆堆栈效率,提高效能并降低成本,支援28HV OLED触控显示整合(TDDI)之应用。

4、微机电系统

2020年年,台积公司完成模块化微机电系统(Modular MEMS)技术的验证,以大量生产高分辨率加速度计与陀螺仪。未来计划包含开发下一世代高敏感度薄型麦克风、十二吋晶圆微机电光学影像稳定(Optical Image Stabilization, OIS)系统解决方案,以及生物微机电应用。

5、氮化镓半导体

2020年,台积公司开始量产第一代650伏和100伏增强型高电子移动率晶体管(E-HEMT),迅速拉升至全产能,公司持续扩充产能以因应客户的需求,第二代650伏和100伏E-HEMT之质量因素(FOM)较第一代改善50%,预计于2021年年投入生产。

此外,100伏空乏型高电子移动率晶体管(D-HEMT)已完成元件开发,具备优异的性能,且通过多家5G基地台模块设计公司的工程验证,预计于2021年进入试产。

6、互补式金属氧化物半导体(CMOS)影像传感器

2020年,台积公司在互补式金属氧化物半导体影像传感器技术获致数项技术创新,有四项主要成果:(1)画素尺寸的微缩较前一年减少15%,目前大量生产中,支援行动装置,高分辨率影像感测应用;(2)完成技术移转并开始量产车用规格等级,超高动态范围的影像传感器,符合高可靠度标准;(3)锗质飞时测距(TOF)传感器开始试产,提供较高的三维物件感测准确度并使用较长的光源波长,相较于硅质感测器,获致较低的系统功耗,适合行动装置与机器视觉应用;(4)成功开发第二代三维金属-介电质-金属(MiM)高密度画素内嵌式电容,电容密度较前一代高三倍,支援全域式快门与高动态范围影像传感器之应用。

7、嵌入式快闪存储器/新兴存储器

2020年,台积公司在嵌入式非挥发性存储器技术领域达成数项重要的里程碑:在40纳米制程方面,公司已成功量产分离闸(Split-Gate)反或闸式(NOR)技术,以支援消费性电子产品的应用与各种车用电子产品的应用;

在28纳米制程方面,支援高效能行动运算与高效能低漏电制程平台的嵌入式快闪存储器开发维持稳定的高良率,并已通过消费性电子与第一级车用电子技术验证,预计于2021完成最高规格第零级车用电子技术验证;

台积公司亦提供嵌入于非挥发性存储器之电阻存储器技术,作为低成本解决方案,支援对价格敏感的物联网市场;40纳米已完成技术验证,客户产品验证持续进行,28纳米已进入量产,22纳米于2020年完成技术验证。

2020年,台积公司在嵌入式磁性随机存取存储器技术取得大幅进展,22纳米已完成技术验证并成功进入量产,并荣获2020年度快闪存储器高峰会之最佳参展项目奖,支援最创新的人工智能应用;22纳米嵌入式磁性随机存取存储器预计于2021年完成技术验证,支援车用电子应用;在16纳米制程方面,维持稳定的高良率,预计于3032年完成技术验证,以因应下一世代嵌入式存储器,支援MCU、车用、物联网以及人工智能装置等多项应用。

未来的主要发力点

为了维持及强化台积公司的技术领先地位,台积公司计划持续大力投资研发。对于先进的CMOS逻辑技术,台积公司的3纳米及2纳米CMOS技术将持续进展。

此外,公司的前瞻研发工作将聚焦于2纳米以下的技术,例如三维晶体管、新存储器及低电阻导线等领域,符合进度以期为技术平台提供坚实的基础。关于三维集成电路先进封装,具有节能效益的子系统整合和微缩的创新,能够进一步增强CMOS逻辑应用。在特殊制程技术方面,台积公司更加着重于新的特殊技术,例如射频及三维智能传感器,以支援5G及智能物联网的应用。

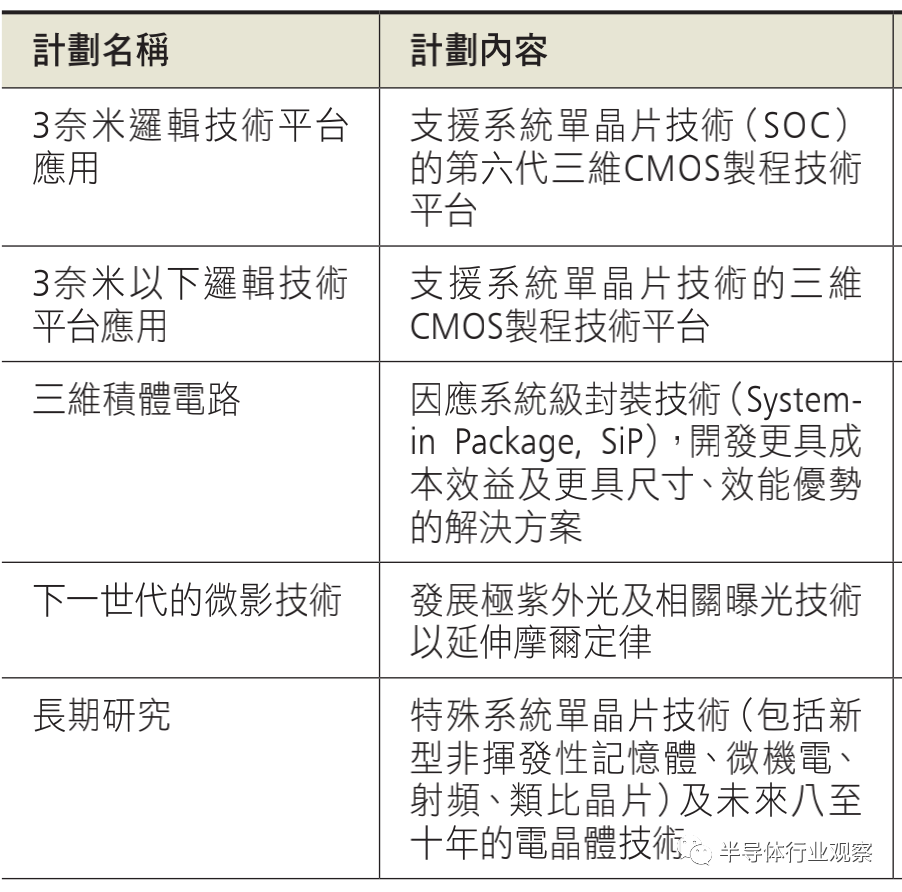

台积电主要研发计划摘要

2017年,台积公司成立先进技术研究部门,将持续专注于新材料、制程、元件、纳米线、存储器等未来八至十年后的长期研发。台积公司也持续与外部的研究组织合作,从学术界到产业联盟,以延续摩尔定律为目标,为提供客户具成本效益的技术及制造解决方案铺路。

凭借着优异、高度专注的研发团队,加上对创新的坚定承诺,台积公司对自身的能力有信心,为客户提供有竞争力的系统单芯片技术,确保公司在未来业务的成长及获利。

责任编辑:lq

-

集成电路

+关注

关注

5384文章

11425浏览量

361120 -

台积电

+关注

关注

44文章

5615浏览量

166242 -

晶圆

+关注

关注

52文章

4861浏览量

127856

原文标题:从年报看台积电,晶圆龙头比你想象中强大

文章出处:【微信号:半导体科技评论,微信公众号:半导体科技评论】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

台积电对公司的市场、技术和未来发展

台积电对公司的市场、技术和未来发展

评论