· 寄语 ·

小伙伴们,我们又见面了,上一期☞「IC手记 • 点沙成金的半导体行业」给大家介绍了芯片简史和PA测试的内容,这一期,我们继续为大家带来数字芯片的重要分支:存储器,以及DDR5技术及完整的测试方案。

存储器简史

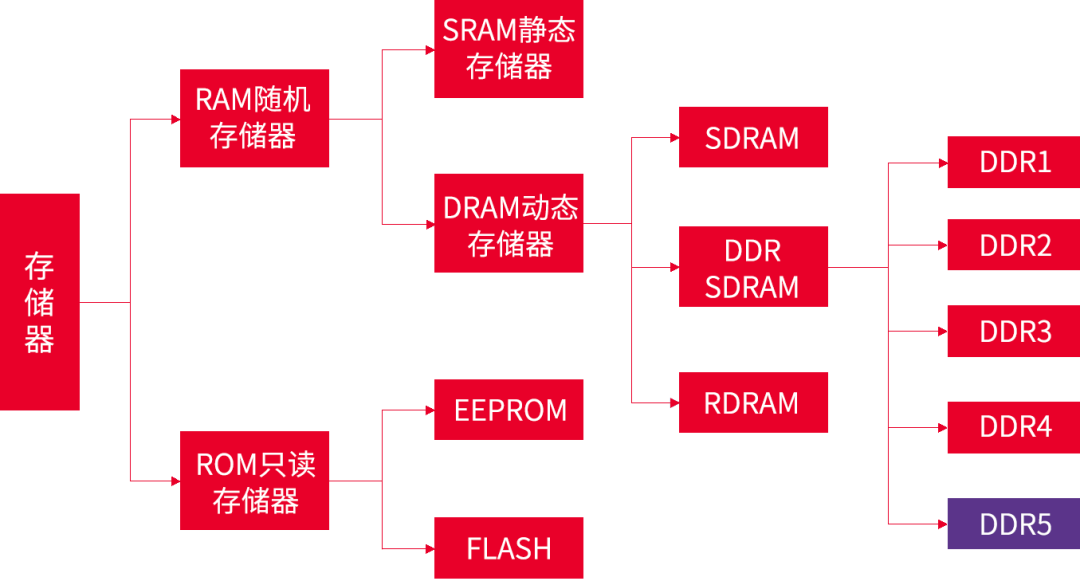

存储芯片是数字芯片的重要组成部分,能够存储程序和各种数据,并能在计算机运行过程中高速、自动地完成程序或数据的存取,如下是存储芯片的基本分类:

图:存储器基本分类

ROM:只读存储器

ROM所存数据,一般是装入整机前事先写好的,整机工作过程中只能读出,ROM所存数据稳定,断电后所存数据也不会改变。

RAM:随机存取存储器

(random access memory)

RAM是与CPU直接交换数据的内部存储器,它可以随时读写,速度快,通常作为操作系统或其他正在运行中的程序的临时数据存储媒介,当电源关闭时RAM不能保留数据。

DDR SDRAM,也是我们今天的主角,在SDRAM的基础上发展而来,这种改进型的DRAM和SDRAM是基本一样的,不同之处在于它可以在一个时钟读写两次数据,这样就使得数据传输速度加倍了,也是目前电脑中用得最多的内存,而且具有成本优势。DDR已经发展至今已经进化到DDR5,与DDR4相比,DDR5 在强大的封装中带来了全新的架构,下面我们会着重介绍DDR5技术及测试方案。

DDR5简介

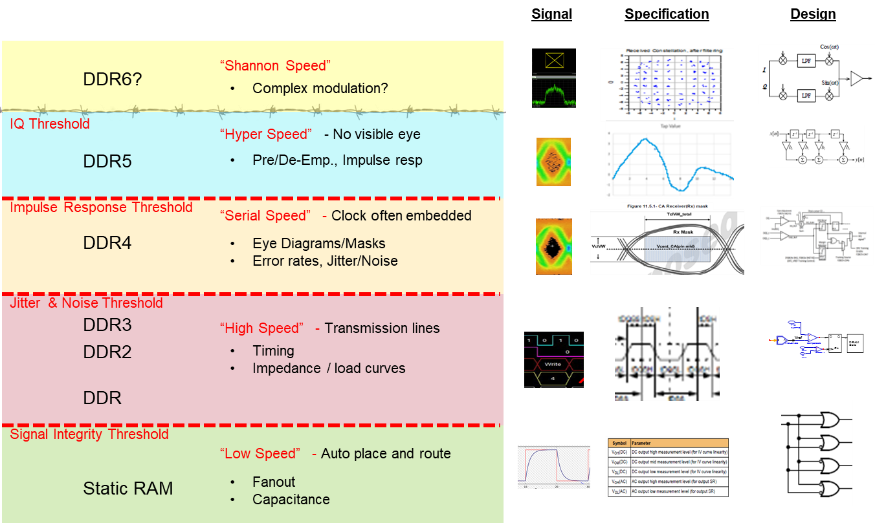

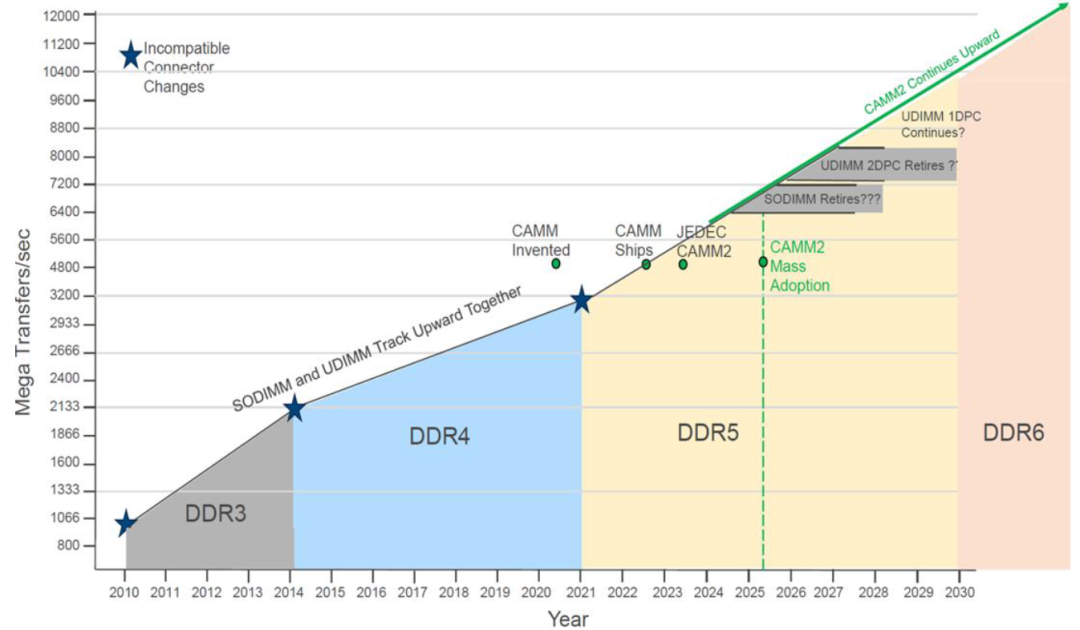

DDR总线经过演进,如今已经发展到DDR5,下图是DDR总线的演进路线:

图:DDR技术演进

无论是从移动计算、PC、服务器到图形计算等领域,总线从早期的低速简单时序特性,到DFE等技术在DDR5中被应用,内存总线在逐步引入SerDes技术,并逐渐逼近通道传输极限。随着DDR5规范的正式发布,步入2021年,DDR5已开始被服务器CPU和存储器厂商所采用,其具备更高的数据速率、更低的能耗和更高的密度。

DDR5具备如下几个特点:

· 更高的数据速率 ·

DDR5最大数据速率为 6400MT/s(百万次/秒),而 DDR4 为 3200MT/s,DDR5 的有效带宽约为 DDR4 的 2 倍。

· 更低的能耗 ·

DDR5的工作电压为1.1V,低于DDR4的1.2V,能降低单位频宽的功耗达20%以上

· 更高的密度 ·

DDR5 将突发长度增加到 BL16,约为 DDR4 的两倍,提高了命令/地址和数据总线效率。相同的读取或写入事务现在提供数据总线上两倍的数据,同时限制同一存储库内输入输出/阵列计时约束的风险。

此外,DDR5 使存储组数量翻倍,这是通过在任意给定时间打开更多页面来提高整体系统效率的关键因素。所有这些因素都意味着更快、更高效的内存以满足下一代计算的需求。

应对DDR5测试的挑战

如前文所属,DDR5具备诸多的优势,也极大增加了测试的难度及复杂度。作为测试行业的领导者,是德科技一直以来积极推动JEDEC DDR5规范测试方案的开发,与行业内的头部伙伴共同推动规范的演进和实施,从DDR总线仿真、测试夹具的定义和开发、Rx测试及Tx测试苛刻的抖动质量要求、再到协议测试方法的开发。是德科技也是唯一一家提供完整DDR5的Tx/Rx物理层到协议测试的方案提供商。

针对DDR生态链中的不同产品形态,是德科技都提供完整的解决方案,如下图,包括发射端测试、接收端测试、协议测试等等,我们在下文会分别予以介绍。

1

DDR5发送端测试

随着信号速率的提升,SerDes技术开始在DDR5中采用,如会采用DFE均衡器改善接收误码率,另外DDR总线在发展过程中引入训练机制,不再是简单的要求信号间的绝对建立保持时间,在DDR4的时代开始使用眼图的概念,在DDR5时代,引入抖动成分概念,从成因上区分解Rj,Dj等,对芯片或系统设计提供更具体的依据;在抖动的参数分析上,也增加了一些新的抖动定义参数,并有严苛的测量指标。

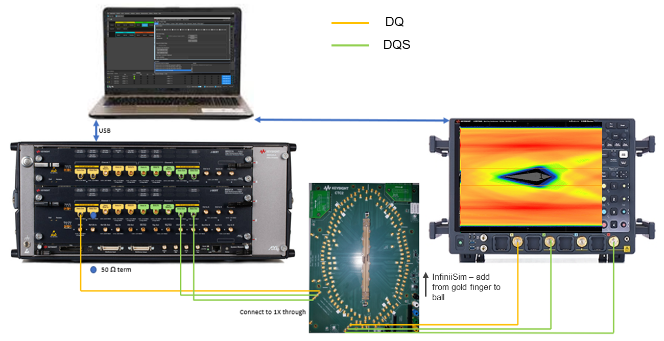

针对这些要求,是德科技提供了完整的解决方案。基于是德科技10bit ADC的UXR示波器,配合D9050DDRC软件,及高阻RC探头MX0023A,及Interposer,可以实现对DDR信号的精确表征。

2

DDR5 接收端测试

随着DDR5信号目标速率持续提升,链路的ISI和串扰问题愈发明显,在DDR芯片颗粒端信号可能已经闭合,为了保证误码率,在DDR5芯片中引入了VGA+DFE的结构,使得均衡后内部眼图重新展开。所以传统的只在DDR memory端测试眼图的方法在DDR5时代并不是一个合理的方法,是德科技针对这种情况,推动了DDR5新的测试方法,即Rx测试。

下图为基于UXR示波器及M8020A误码仪的接收端校准和测试组网:

是德科技和协会及相关公司共同定义了测试夹具,如CTC2测试基板夹具,Device芯片测试夹具卡。接收端测试包括如下测试内容:DQS Voltage Sensitivity,DQ Voltage Sensitivity,DQS Jitter Sensitivity,DQ Stressed Eye,CA Voltage Sensitivity,CA Stressed Eye,DQS2DQ,DFE Characterization等。

3

DDR5协议测试

JEDEC的规范中,定义了如下图中的参数要求,是德科技的U4164A逻辑分析仪,可用于DDR5协议测试。B4661A软件可以支持这些参数的实时和后分析功能,分析判断测试结果是否符合规范的范围要求,并且可以跟踪测量结果,对于违规的测量参数可以跟踪到波形界面,从而定位命令和操作的根源问题。

4

DDR5芯片颗粒及DIMM测试

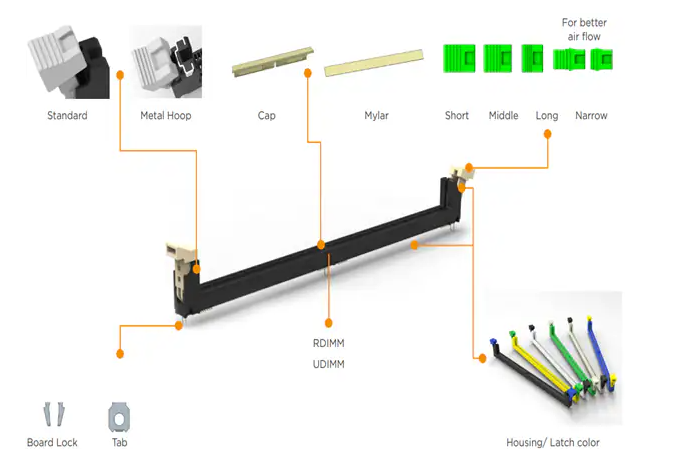

针对DDR5,基于U4164A x 4及Futureplus公司FS2600 DDR5 RDIMM/LRDIMM Interposer夹具。另外,针对芯片颗粒的测试,Keysight也提供W5643A DRAM BGA Interposer。

5

DDR5测试总结

是德科技为DDR行业提供了最完整的解决方案。

原文标题:IC手记 • 存储器芯片及DDR5

文章出处:【微信公众号:是德科技KEYSIGHT】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

芯片

+关注

关注

463文章

54441浏览量

469421 -

存储器

+关注

关注

39文章

7757浏览量

172209 -

DDR

+关注

关注

11文章

761浏览量

69566

原文标题:IC手记 • 存储器芯片及DDR5

文章出处:【微信号:是德科技KEYSIGHT,微信公众号:是德科技KEYSIGHT】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

立锜科技推出完整DDR5服务器内存电源解决方案

Altera面向DDR5与LPDDR5的FPGA解决方案现已实现量产交付

存储市场现罕见倒挂:DDR4价格涨幅十倍于DDR5涨价潮持续蔓延

Amphenol ICC DDR5 SO - DIMM连接器:高速高密度的理想之选

澜起科技推出支持9200 MT/s速率的DDR5时钟驱动器(CKD)芯片

TE Connectivity DDR5 DIMM插槽技术解析与应用指南

DDR5 暂停报价只是开始,PCB 行业的 “芯片依赖症” 正在爆发

DDR5 设计指南(一):DDR5 VS LPDDR5

紫光国芯存储芯片国产替代方案:打破DDR5/HBM芯片供应链瓶颈

涨价!部分DDR4与DDR5价差已达一倍!

Bourns 全新推出两款屏蔽功率电感器系列 专为 DDR5 电源管理电路开发

存储器以及DDR5技术及完整的测试方案

存储器以及DDR5技术及完整的测试方案

评论