最近五年来,功率性能领域(和成本)的提高主要是通过晶体管的尺寸缩放来实现的。晶体管缩放超过纳米阈值后,从16/12 nm,10 nm,7 nm,5 nm,3 nm,2 nm,1.4 nm到纳米以下,半导体行业将做什么?这些先进的逻辑技术是否会继续提供未来计算系统所需的能效?新的应用程序和计算工作负载是否需要新的设备技术并将其集成到未来的系统中?这些都是当今半导体行业面临的一些最紧迫的问题。

未来IC技术发展的道路不再是一条直线。开箱即用的解决方案的需求将迎来创新的黄金时代。未来的电子系统将需要计算架构以及设备和封装技术的共同创新。那么,全球晶圆代工龙头台积电为了将代工这活儿做到极致,又在探索哪些新技术?

无懈可击的台积电

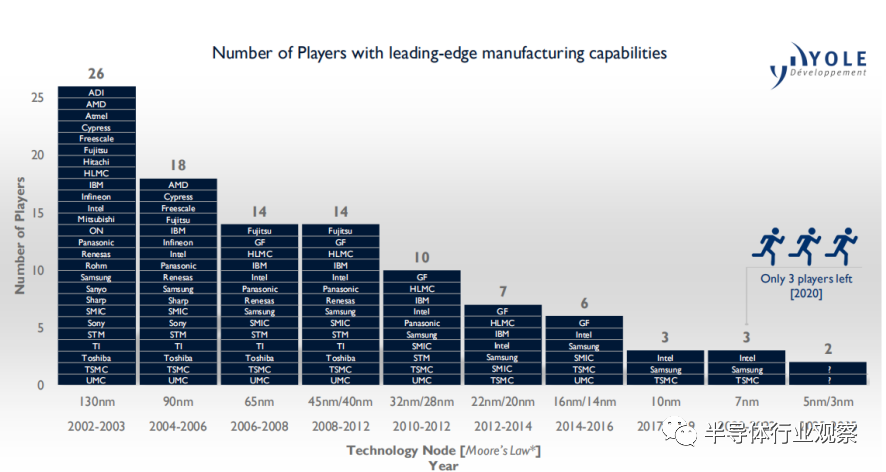

据Yole发布的一份调研报告中显示,在过去的几十年里(自1965年以来),摩尔定律一直指导着全球半导体行业,在这个演进的过程中,先进制程的发展提高了性能和成本,大浪淘沙,2002年的26家角逐的厂商最后仅剩台积电和三星两家“孤独者”。在短短的20年间,全球代工厂以放弃而闻名,先进制程玩家减少了近九成。

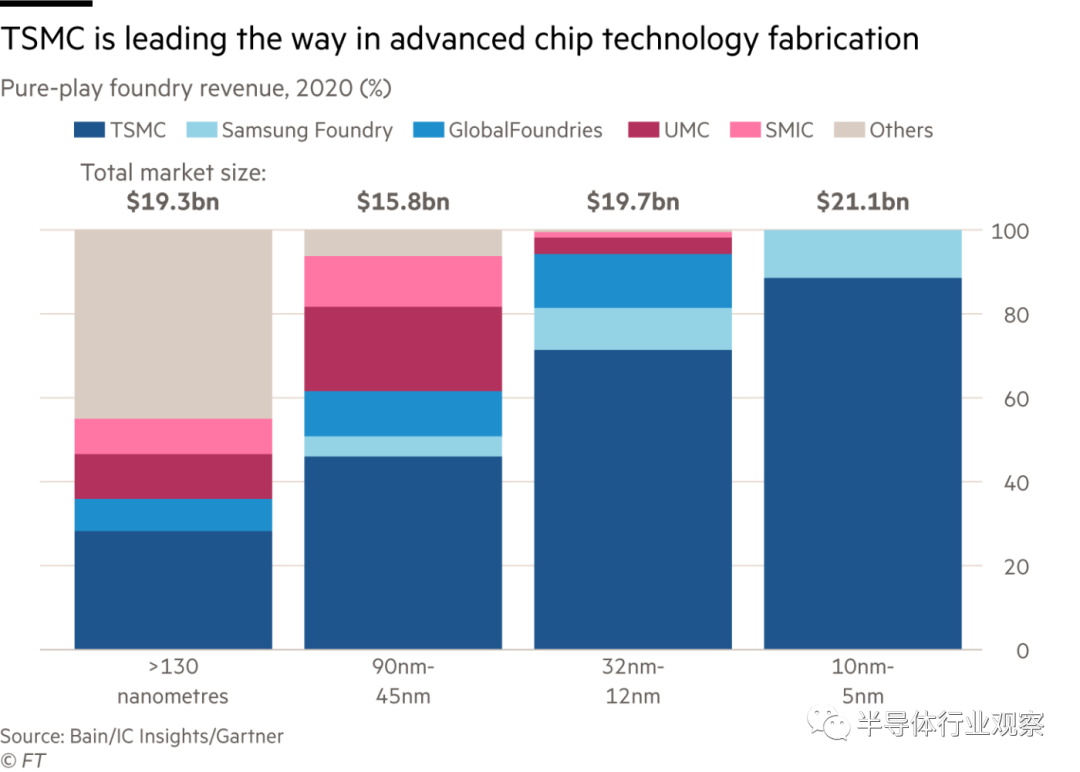

如今台积电在每个新的工艺技术节点上都变得越来越占主导地位:尽管它仅占28-65nm类别中用于生产大多数汽车芯片的节点的收入的40%至65%,但它几乎占据了市场的90%当前生产中最先进的节点。

台积电(TSMC)今年将其资本投资预期上调至高达250亿至280亿美元,可能比2020年增加63%,领先于英特尔和三星。分析人士认为,这至少包括台湾制造商向英特尔提供产品所需的产能投资。

逻辑上多管齐下

台积电一直走在先进CMOS逻辑技术的前沿,在这种技术中,密集晶体管是两个基本的构建模块之一,另一个是密集互连堆栈。给定逻辑技术的内在计算能力直接与晶体管互连的数量及其在典型负载下的开关速度有关,这些负载由晶体管或门驱动,以及相关的互连电阻和电容电路负载。在逻辑领域,台积电主要研究在晶体管结构、高迁移率通道以及低尺寸材料和器件方面的计算。

台积电CMOS逻辑技术一直依赖于平面晶体管结构,直到2014年其16纳米技术就将FinFET引入生产。FinFET结构解决了平面器件缩放的根本限制,即在较短的栅极长度下对沟道的不良静电控制。FinFET还使晶体管密度缩放与器件有效宽度缩放能够部分解耦,这是获得增加的每单位晶体管足迹的晶体管电流的重要功能。与平面晶体管相比,这些FinFET特性可显着降低电源电压。FinFET还为功率性能优化提供了新的自由度,从而极大地提高了从16nm到5nm技术节点的能效。

台积电的研发工作继续探索下一代结构,例如堆叠纳米线或堆叠纳米片,以期在未来技术节点的计算性能和能源效率方面达到新的高度。

直到其7nm节点为止,硅一直是所有CMOS技术世代中选择的晶体管通道材料。台积电(TSMC)积极探索替代晶体管沟道材料,以在高性能和低功率器件的设计中增加自由度。硅锗和锗是台积电探索性研究工作的例子,该研究工作已被广泛发表,在某些情况下被公认为国际会议的亮点。台积电的5nm技术是第一项以SiGe为p型FinFET的沟道材料的先进逻辑生产技术。

此外,台积电(TSMC)的晶体管研究团队也在研究以具有固有2D或1D载流子传输(低维传输)的材料为基础的器件。过渡金属二卤化物,石墨烯纳米带和碳纳米管等都在理论和实验上得到了研究。

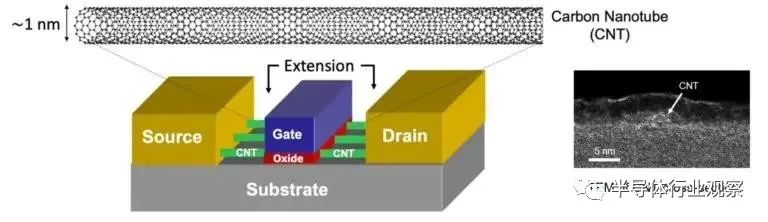

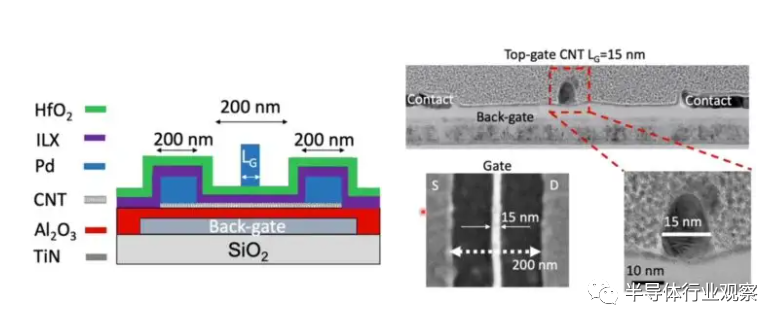

如在最近的IEDM会议上,台积电提供了有关谈纳米管器件制造进展的更新。台积电开发了独特的工艺流程来为CNT器件提供“高K”电介质等效栅极氧化物,类似于当前硅FET的HKMG处理。随后,添加高K HfO2膜的原子级沉积(ALD),采用了独特的“顶栅加背栅”拓扑。

上面的TEM图说明了CNT的横截面。为了与独特的碳表面兼容,需要沉积初始界面电介质(Al2O3)–即,需要在碳上对该薄层进行适当的成核和整合

采用了独特的“顶栅加背栅”拓扑

使用2D和1D材料的好处包括原子厚度的高迁移率,出色的栅极控制以及低功率和高性能器件的潜在应用。因此,可以扩大晶体管的缩放比例。在最近的报道中,台积电成功地证明了晶圆级h-氮化硼单层膜的生长,该膜层能够有效地保护通道2D半导体免受工艺损伤以及相邻电介质中电荷杂质的扩散。一维半导体碳纳米管具有与生产线后端(BOEL)制造温度(《400℃)兼容的工艺,是实现单片3D IC的潜在组件。在台积电的28nm CMOS技术芯片上,碳纳米管晶体管的概念验证整体集成也得到了验证。

在互连上的探索

互连对于系统性能至关重要。它们是将两个或多个电路元件(例如晶体管)电连接在一起的结构。在过去,互连通常被称为集成电路的片上互连。如今,互连通常既包括集成电路的片上互连又包括异构系统集成中的片外互连。在互连设计中,几何尺寸(宽度,厚度,间距,长宽比,间距),材料,过程控制和设计布局对于适当的互连功能,性能,功率效率,可靠性和制造良率都是至关重要的。

首先来看片上互连,当今的片上互连基于铜线/低k布线,在当今的芯片中,铜线可能超过100公里。台积电使用新颖的铜间隙填充解决方案来制造更小的导线。新开发的材料和工艺可以大大减少线路和通孔电阻,从而改善芯片性能。集成方案,低k材料和具有选择性沉积的低k工艺的全面创新套件进一步提高了性能(通过减小电容)和可靠性。除了铜互连之外,台积电内部以及其学术合作伙伴也正在探索单一金属元素,二元和三元合金以及用于未来互连材料的2D材料。

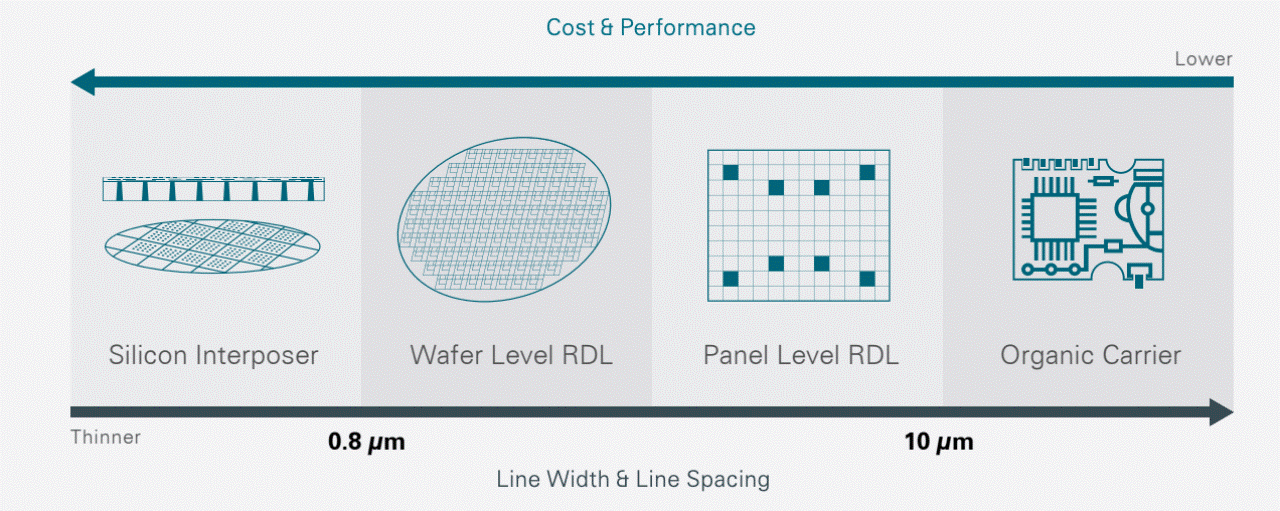

然后是片外互连技术。要知道,硅中介层,高密度细间距扇出RDL和无凸点键合是创新的先进异构集成技术(HIT)上芯片间互连的三大支柱。每种互连技术在AI和5G网络各自的领域中提供最佳的PPACC(PPACC:功耗,性能,面积(尺寸),成本,上市周期),并且与晶圆级异构集成技术(即HPC和移动应用系统中的CoWoS,InFO和SoIC)紧密相关。

台积电也在片外互联技术上不断努力以实现更好的PPACC:硅中介层具有高互连密度,高比电容密度和大标线片尺寸,可用于百亿分之一的HPC / AI;扇出时具有较高的互连密度和较大的光罩尺寸,可在HPC /网络AI中实现成本和性能;在SoIC上,高3D互连密度和超低键合延迟,适用于节能计算系统。

对新兴存储技术的探索

内存也是台积电发展的一大重点,现代社会,每天生成的数据超过2.5亿字节,需要处理的数据非常多,而内存在数据流中起着关键作用。逻辑与内存之间的差距是系统性能的瓶颈。为了优化成本和性能之间的权衡,市面上已开始采用分层存储系统。

最近出现的新技术正在迅速发展,以将处理任务带到内存附近或内存中,以提高计算效率并启用新功能。新兴的NVM使用新型的材料和机制来存储数据。它们有望用于混合内存层次结构以提高整体性能。此外,它们的独特特性为启用新应用程序(例如神经形态计算)和新颖的体系结构(例如3D集成)提供了巨大的潜力。

台积电这些年正在积极探索新兴存储技术。台积电的非易失性存储器解决方案包括闪存,自旋转移力矩磁性随机存取存储器(STT-MRAM)和电阻式随机存取存储器(RRAM)。台积电还积极探索相变随机存取存储器(PCRAM)和自旋轨道扭矩MRAM(SOT-MRAM)元件,以及支持更高密度交叉点阵列架构必不可少的选择器设备。

台积电已经开发并提供STT-MRAM解决方案,以克服嵌入式Flash技术的扩展限制。台积公司正在积极探索SOT-MRAM和VC-MRAM,并与外部研究实验室、财团和学术合作伙伴合作。台积电的SOT-MRAM的探索是由高速(《2ns)二进制存储器解决方案驱动的,这种解决方案比传统的6T-SRAM解决方案密度大得多,同时也更节能。

MRAM之外,台积电与技术伙伴合作,在40nm CMOS逻辑主干上开发了RRAM内存技术,以支持特定应用需求。台积电还在继续探索新颖的RRAM材料组合及其密度驱动的集成,以及可变感知电路设计和程序设计,以实现高密度内嵌RRAM的解决方案,以供AIoT应用。

相变随机存储器(PCRAM)是一种基于硫族玻璃的非易失性存储器。PCRAM电阻通过控制焦耳加热和淬火在非晶态(高电阻)和结晶态(低电阻)之间过渡。存储器的电阻状态与非晶区大小及其可控性和稳定性有很大关系。这使得PCRAM细胞具有独特的存储多种状态(电阻)的能力,因此比传统的二进制存储器具有更高的有效细胞密度的潜力。PCRAM可以支持阵列配置,包括一个晶体管与一个存储器(1T1R)阵列和一个选择器与一个存储器(1S1R)阵列。台积电一直在探索PCRAM材料、细胞结构和专用电路设计,以实现AI和ML的近内存和内存计算。

结语

在新技术短缺和超级大国竞争的时候,台积电在芯片生产中的主导地位凸显。而观看其对先进技术的不懈探索,不由发问,代工厂的秘诀在哪里?想要追赶台积电的英特尔前面又有多少拦路虎?三星估计也在想,我与台积电究竟差哪了?

责任编辑:lq

-

台积电

+关注

关注

44文章

5630浏览量

166385 -

晶圆代工

+关注

关注

6文章

859浏览量

48576 -

汽车芯片

+关注

关注

10文章

853浏览量

43381

原文标题:台积电正在研究的先进技术

文章出处:【微信号:半导体科技评论,微信公众号:半导体科技评论】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

字节跳动否认与台积电合作AI芯片

台积电CoWoS产能将提升4倍

台积电布局FOPLP技术,推动芯片封装新变革

台积电开始探索面板级封装,但三星更早?

台积电又在探索哪些新技术?

台积电又在探索哪些新技术?

评论