作者:汪一鸣,徐清源,翁桂荣,胡子涟,王莲莲

1 问题的提出

自二十世纪80年代以来,可编程逻辑器件(PLD)技术发展非常迅速。由于PLD是作为一种通用器件生产的,而它的逻辑功能是由用户通过对器件编程实现的,随着PLD的集成度越来越高,速度越来越快,设计越来越方便灵活,因而日益成为专用集成电路ASIC设计的主流方法。特别是二十世纪90年代新一代在系统编程技术isp的推出,取消了专用编程设备,器件本身也不必从系统电路板上取下,便可以使用硬件描述语言和电路图方法在系统内编程。这一创举使现代电子系统设计的方法前进了一大步,设计周期大大缩短,效率大为提高,并且十分有利于产品的升级和更新换代。

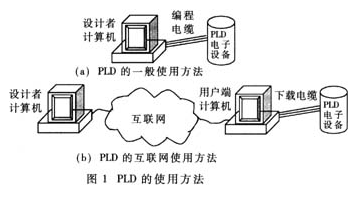

一个数字系统的自动设计流程,可以分为四个阶段。首先是对系统的功能进行分析,利用原理图或硬件描述语言表达设计者的意图;第二是步利用仿真工具对设计者的想法进行测试仿真,以便发现设计中的缺陷和错误;第三步是将前两步生成的文件进行编译并和具体器件相适配,生成具体芯片的融丝图文件;最后一步就是将融丝图文件通过编程电缆下载到包含有PLD的设备中,从而实现一个物理的数字系统,如图1(a)所示。

在这四个阶段中,前三步都可以在计算机上使用不同软件工具实现,而最后一步必须和具体的设备进行连接,这意味着需要设计者亲临现场操作。设想如果产品发往外地,或是远涉重洋出口海外,就需要生成一个庞大的全球性售后服务网络对产品跟踪或更新,这对中小企业来说根本不可想象。如何解决这个问题呢?我们想到了无所不能的互联网。既然中小企业的原材料供应、成品销售等可以受益于互联网,那么他们的技术性服务为什么不可以通过互联网进行呢?为此,我们利用互联网及其TCP/IP协议开发研制了一个远程在系统编程工具,使工程技术人员足不出户就可以对他们利用PLD研制生产的远在千里之外的电子系统、电子设备进行升级和维护,如图1(b)所示。

2 系统结构

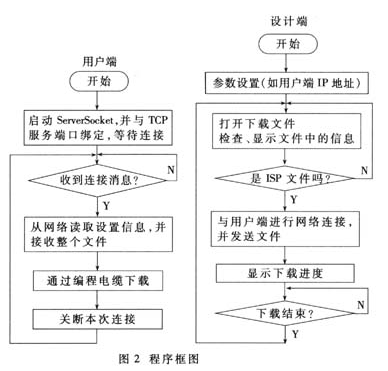

本工具采用了客户服务器模式,由两个部分组成。一个在用户计算机上执行,称之为用户端;另一个在设计者计算机上运行,称之为设计端。软件编制使用C++语言,在C Builder环境下设计。程序中使用C Builder中提供的网络通信控件,实现客户和服务器之间的通信。本工具程序框图见图2。

首先由用户端将设备和计算机通过下载电缆(使用并行口)连接在一起,并启动计算机运行用户端程序。用户要做的就是这些,这些操作不需要任何专业知识。用户端程序也不需要什么配置,只要它自动扫描并发现接有设备的端口,并对之操作即可。

用户端程序一旦运行,设计端程序就可以启动。设计端首先输入用户端的IP地址,输入不同的IP地址,就可以对不同的用户端设备进行操作。然后调入设计好的融丝图文件,对文件的格式进行检查,显示文件中的信息。文件中的信息指示该文件对哪些芯片编程,以及它们在设备中的排列顺序。

检查正确后,就可以进行网络连接,并把文件内容发送给用户端。在用户端将融丝图下载到PLD芯片的过程中,用户端应用程序回送下载进度给设计端,设计端就可以显示下载进度。如果一切正常,下载完毕后就关闭连接,结束通信。

3 技术实现

3.1 设计端

设计端界面为一窗体,窗体上有一个命令菜单、一个编辑控制(输入或显示打开的文件路径和文件名)、一个组合框(让用户选择下载模式)、两个显示下载进度和文件信息的备注控件,还有一个用于通信的客户端套接字控件。

设置IP地址,点击“命令/设置”时会显示一个模式对话框。用户可以在 “IP地址”编辑控制中输入用户端的IP地址,按“确定”该值将赋给客户端套接字控件的属性“Address”,进行网络连接时,将与拥有该IP地址的主机通信。在 “端口”编辑控制中输入用户端下载服务的TCP端口号,按“确定”将该值赋给套接字控件的属性“Port”,进行网络连接时,将与指定主机的服务端口通信。

下载文件,直接在编辑控制中输入文件名或点击“打开文件”,通过对话框得到下载文件的路径。每次选择一个isp文件, 所谓isp文件,是将标准的融丝图JED文件采用一定的压缩算法生成的。它比标准的JED文件要小,这样下载时速度要快些。为了能够下载成功,要对文件格式和内容进行检查。检查依据的是isp文件的头格式,包括文件类型、芯片链中芯片的个数、擦除脉冲宽度、编程脉冲宽度、编程行数、每行长度、芯片ID列表等。文件的第一个字节只要是(0Xf8 0x0B 0x0F 0x0A中的一个,则该文件就是isp文件,不同数值分别代表不同类型的芯片和压缩类型。

下载模式,文件选定后,必须选择下载模式。共设四种模式:编程并校验、仅校验、仅校验UES、校验并显示UES。其中UES是指存放在芯片中的用户自定义信息,根据需要可以是设备的序列号或设备的唯一标识等信息,而与芯片的功能没有关系。

编程并校验,是指将文件内容下载到芯片中,并在下载过程中从芯片读出下载内容,检验是否下载正确。

仅校验,是指读出芯片中的内容,并与文件内容进行比较,检验两者是否一致。

仅校验UES,是指检验文件中的UES信息与芯片中的是否一致。

校验并显示UES,是指把文件中的UES信息与芯片中的UES内容进行比较,检验两者是否一致。若一致,则显示UES内容,否则提示校验错误。

下载模式选定后,就可以进行网络连接了。选择菜单“命令\连接”,调用网络连接的代码。一旦连接成功,系统会发连接成功“CONNECTED”消息。收到此消息后,程序会在此连接上发送一个双字。若该值为1,则表示将发送一个文件,否则表示双方可以用键盘进行对话。如果没有选择下载文件,将自动进入对话状态。若是对话状态,双方可在窗体右边的备注控件中输入对话内容,按回车键就会发送输入内容。若是下载状态,紧接着会发送一个双字,表示下载模式。然后会再发送一个双字,表示文件的长度,最后发送整个文件内容。

用户端收到全部内容后,开始下载。下载过程中用户端把下载进度发送给设计端,设计端收到后,将显示收到的内容。这样,设计者就会看到下载进度。

下载结束后,自动进入对话状态。如果用户端有人,双方可以进行简短对话,讨论一些技术问题。

运行“命令\断开”,则关断网络连接,结束本次下载过程。新的下载过程只要重新运行“命令\连接”即可。

3.2 用户端

用户端窗体上有一个进度条(显示下载进度)和两个备注控件(显示当前用户的工作状态,以及交谈时的输入输出)。用户端需要完成的功能比设计端复杂。主要有数据的接收、设备的自动识别、具体的下载过程等。

程序运行后,在收到窗体创建消息时,将激活服务器套接字,并和TCP端口绑定,等待设计端进程的连接。

只要运行设计端“命令\连接”,就会在用户端产生网络连接的消息。连接成功后,与设计端对应,收到的第一个双字,代表本次连接是下载状态还是对话状态。若是1,则为下载,否则进入对话状态。若是对话状态,直接在备注控件中输入对话内容,按回车键即可。对方的谈话会在另一个备注控件中显示出来。

若是下载文件(这是最常用的状态),紧接着会收到一个双字,代表下载模式(具体含义见前)。然后会再收到一个双字,代表将要下载的文件长度。若该值小于等于零,或等于0Xffffffff计算机中的-1,则提示发送方有错,并关闭本次连接,否则将会接收全部文件内容。文件的结束是靠文件长度与收到字节数进行比较,相等表示全部收到。全部收到后,即进行下载。

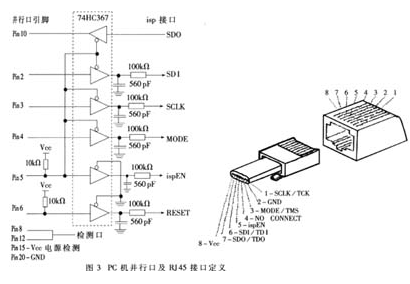

编程电缆,下载过程与硬件密切相关,我们使用编程电缆(共8根线?使用其中的7根)与并行口连接。每个并行口有三个端口:数据、状态、控制端口,每个端口占一个字节。具体定义如下:

在电缆内部将并行口的8脚与12脚直接连接,用于检测电缆是否已插到并行口上。向数据端口的第6位写数据,再从状态端口第5位读入数据,比较两者是否一致,即可得知下载电缆是否连接。图3给出了编程电缆及接插件的端口定义。

其它信号的含义及作用如下:

out_SDI 将isp数据从此脚串行输出到芯片上;

out_SCLK 控制下载过程的时钟信号;

out_MODE 将isp命令从此脚串行输出到芯片上;

out_ISP 控制芯片在正常工作模式和编程模式

之间切换;

in_SDO 从芯片上串行读出isp数据;

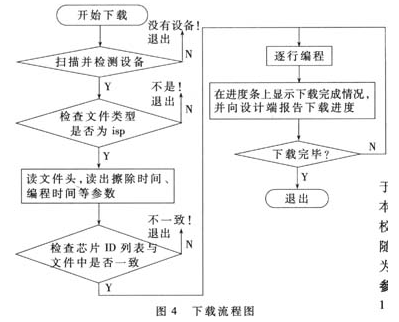

in_VCC_OK 用于检测设备电源是否打开。 下载的流程图见图4。

下载开始首先扫描三个并行口端口。利用信号in_CABLE_SENSE_IN和in_VCC_OK检测设备是否和计算机连接以及电源是否打开,两个信号同时有,则表示该端口连接有设备。如果找不到设备,就给出提示并中断这次下载过程。再检查文件的类型,看设计端发送来的文件是否为合法的isp文件。否则给出提示并中断这次下载过程。若合法,则接着读出被编程芯片的编程、擦除时间以及编程行数等信息。其中编程和擦除时间的控制,是利用多媒体定时器实现的,可以实现准确的脉冲延迟,保证擦除、编程的可靠性。随后从芯片中读出该设备中含有的芯片ID列表(ID列表与芯片型号有关),并与设计端的值进行比较。若一致可以继续下载;否则给出提示并中断本次下载过程。因为芯片列表不一致,将导致设备根本不能工作。

下载时,通过out_SDI端将数据一个比特一个比特地串行输出到芯片中,并从SDO端读出刚写入芯片的数据,与文件中应写入的数据进行比较校验,以保证数据准确地写入到芯片中。

4 出错处理

错误的处理是软件设计中十分重要的一个方面,本软件同样充分考虑各种意外和错误,使得错误的影响得到很好控制。本软件中最主要的出错处理就是对网络错误的处理,如设计端用户输入的IP地址或端口号不正确等。

C Builder中的网络控件提供了出错的消息,对于因网络连接、连接中断或网络超时等引起的问题,该消息都会被触发。消息被触发时,在消息处理函数中将一些变量重新初始化,并关断网络连接。值得一提的是,因计算机IP地址的设置而产生的网络错误消息将不会发给控件,例如:计算机的子网掩码为255.255.255.0,本机地址为202.195.168.1,不设置网关。在这样的配置下,如果与IP地址为202.195.200.1的主机进行连接,将会产生网络错误“子网不可到达”?而控件却收不到这个消息。此时必须调用SetErrorProc,指定自己定义的网络意外处理过程来替代默认过程。新过程将捕获所有网络意外,从而避免该消息的遗漏。

另外对下载过程中出现的各种不正常情况都做了检测,例如:下载电缆没有连接、设备电源没有打开、器件列表不符和校验错误等。当检测到这些错误时,由于用户端无人值守,因此将错误信息回送设计端,并用适当的形式显示给设计者,以便设计人员做进一步处理。

5 应用范围及前景

该工具可供所有使用PLD器件进行设计和开发电子产品及系统设备的公司或厂家使用。对于他们拓展业务范围、提升产品价值、增加产品的信息技术含量、降低生产成本、争取更多用户、以信息化带动工业化等都具有深刻意义。

该工具也可供开设数字逻辑电路和数字系统设计课程的相关学校使用,为教师在局域网上指导和批改学生的实验提供了方便,并可以把学生从都做同样的单一实验这种传统模式中解放出来,有利于针对不同学生给出不同要求,同时也降低了教学成本。特别对远程教学而言,该工具为一直困扰工科院校的网上教学等问题提供了一种具有开拓意义的方法。随着信息技术的进一步发展,我们相信类似的应用将成为互联网应用的一个新领域。

责任编辑:gt

-

集成电路

+关注

关注

5396文章

11643浏览量

363700 -

计算机

+关注

关注

19文章

7553浏览量

88797 -

PLD

+关注

关注

6文章

230浏览量

59540

发布评论请先 登录

相关推荐

Verilog硬件描述语言描述.

基于Verilog硬件描述语言的IEEE标准硬件描述语言资料合集免费下载

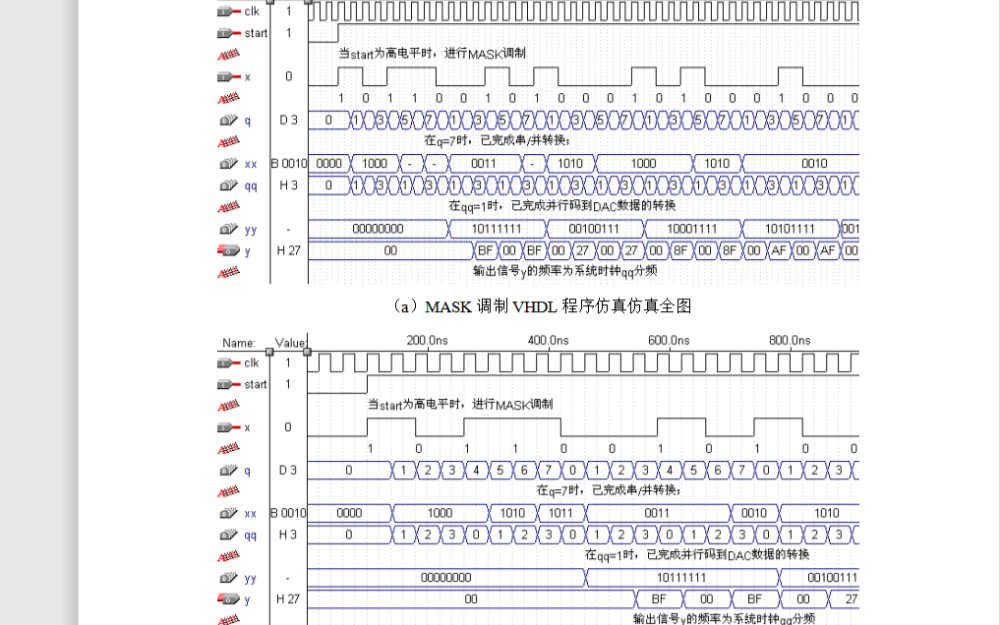

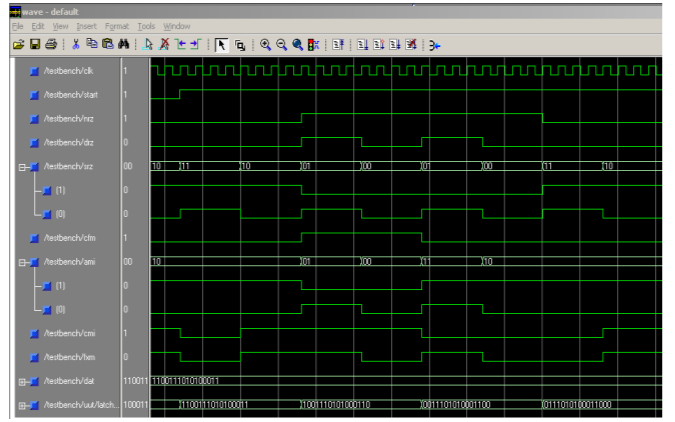

使用VHDL硬件描述语言实现基带信号的MASK调制的程序与仿真

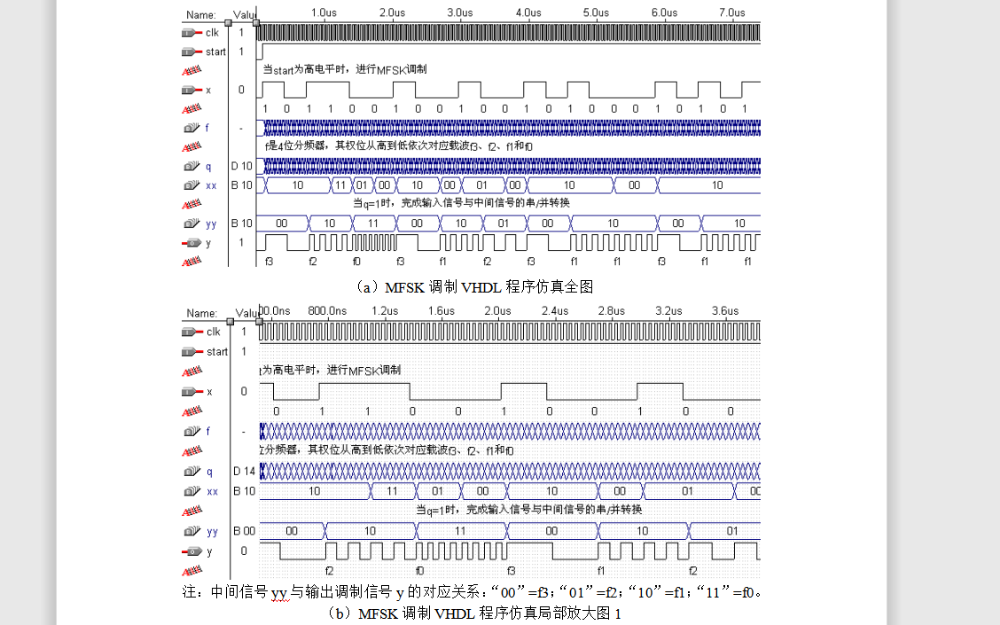

使用VHDL硬件描述语言实现基带信号的MFSK调制的程序与仿真

基于PLD和硬件描述语言实现系统在内编程

基于PLD和硬件描述语言实现系统在内编程

评论