前言

无线通信是通信领域的一大分支,随着数字信号处理能力的提高,数字无线通信逐渐成为无线通信的主流。数字无线通信系统设计的重要目标之一是要系统具有很强的抗多径干扰能力。通常,设计人员需要在实验室对无线信道可能存在的各种干扰(多径、噪声、同频信号等)进行虚拟实现,以便对所设计系统进行调测。多径信道模拟器是进行数字无线通信系统硬件调测不可或缺的仪器之一。无线移动信道复杂多变,目前已有多种数学模型可供参考,本文针对无线移动信道的基本模型,提出一种多径信道模拟器的设计方法,给出了其基本结构框图,并对数字信号处理部分的FPGA实现进行了详细阐述。

信道模型

在无线信道中,由于反射、散射和衍射等的存在,除了直射波之外,还会有信号通过不同的路径沿不同的方向到达接收端,从而使信号产生时延扩展;若接收终端处于移动状态,各条信号支路还会具有不同的多普勒频移,从而使信号产生频率域弥散。典型的无线移动信道二维冲击响应可表示如下[参考1]。

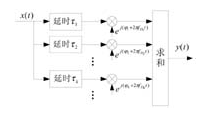

上式中,αk、 k、fdk和τk分别为第k条支路的归一化幅度(衰减因子)、初始相位、多普勒频移和传播时延,τk》0,,各条支路相互独立,如图1所示。设发射信号为x(t)ej2πfct,x(t)为基带信号,fc为载波频率,则接收信号y(t)为发射信号与信道冲击响应的线性卷积。

信道模拟器的设计与实现

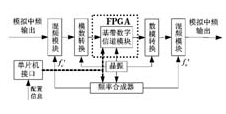

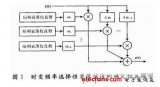

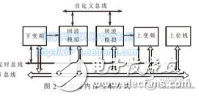

从上可知,要实现信号通过多径信道的模拟,需要对信号进行时延、(多普勒)频移和衰减,并将各支路信号相加。因此多径信道模拟器需要包含延时器、多普勒波产生器、衰减器、乘法器和混合器等单元。对射频信号进行处理时,衰减较容易实现,而延时和乘法运算则实现难度大且精度不易保证。而数字电路在这方面却有其独到之处。因此,信道模拟器通常对信号进行频谱下搬移到基带,然后对基带信号进行采样,在数字域对信号进行信道畸变处理,之后再经过上变频恢复成射频信号,如图2所示。

图2中,晶体振荡器产生的正弦波通过频率合成得到与输入信号载波频率基本一致的本地载波,混频器对信号进行上下变频(正交解调和调制)。由于上下变频用同样的本地载频,故可以保证输出信号与输入信号不存在频率偏差。模数转换器对信号进行采样,因为数字部分实现容易,通常以几倍的Nyquist速率进行采样。虚线框内部分则完成对数字基带信号进行通过信道的运算,也就是下一节所要讨论的内容。

一个好的信道模拟器,其信道冲击响应的时间分辨率一定要足够高。信号的大延时在数字电路中通常用存储器(RAM或FIFO)来实现,而存储器的读写是与时钟同步的,所以信道冲击响应的时间分辨率与数字信号处理单元的时钟周期相等。为提高时间分辨率,需要对输入信号进行上采样处理。上采样后的信号在信道模块与信道冲击响应进行卷积得到经过信道畸变的高采样率信号,运算结果再经下采样滤波以适当的采样率输出,数模转换电路将其恢复成模拟信号。

为方便信道参数设置,可通过单片机对频率合成器和数字电路进行配置。通过RS232串口电缆连接单片机和计算机,可获得良好的界面,通过计算机对信道模拟器进行监控。

数字部分的FPGA设计与实现

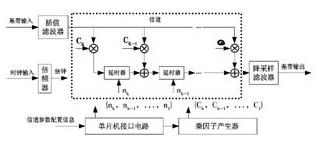

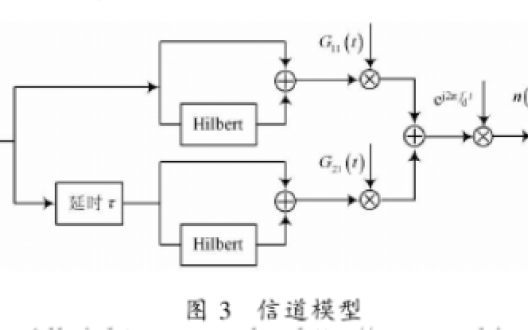

前已述及,信道模拟器数字部分需要对信号进行上采样、信道模拟和下采样等,这几部分运算都需要大量乘法和加减法器,而且电路要工作在较高频率的时钟上,用通用的DSP难以实时完成。FPGA基于硬件实现,能满足高速的要求,同时内置锁相环能提供灵活的时钟倍频功能[参考3],因此易于实现信道模拟功能。信道运算的FPGA实现如图3所示。

图3中,插值滤波、降采样滤波和中间的信道部分都可视为有限序列与无限序列的线性卷积,宜采用FIR(有限冲击响应)滤波器直接型转置结构来实现[参考4]。其中延时器用来对信号进行不同的延时,乘因子产生器用来产生式(2)中各条支路的乘性项。接口电路用来完成FPGA与单片机的通信,可用I2C结构或其他简单通信协议来实现。FPGA中主要模块实现如下。

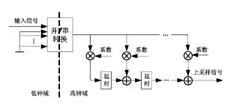

插值滤波器由并串转换电路(用来对输入序列进行插零)和一个FIR低通滤波两部分组成,如图4。

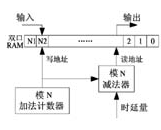

信道模拟器各条支路延时应能灵活变化,因此图3中延时器的时延量必须以时钟周期为步长可调,这可采用双口RAM来实现。由于系统设计时并不太关心信号到达绝对时间,因此可令τ1=0对信道模型简化以节约存储器资源,相应地τk为第k条支路与第一条支路的相对时延差。

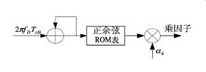

各信号支路的乘因子包括衰减因子和多普勒频移因子两部分。多普勒频移因子由地址产生器(下图的模2π加法器构成)和查找表(ROM)来实现,查找表的输出与衰减因子相乘得支路乘因子。

ROM表的数据格式如下。

而整个ROM表的大小可由实际所需(如FFT长度等)而定。当然,ROM表中的数据是被放大了215倍。如果所需ROM表的存储量很大,则可以只存储(0,π/4)的数据,而在(π/4,2π)范围的则可以通过换算得到。

降采样滤波器由低通滤波器和脉冲抽取电路组成。低通滤波器与插值器中的低通滤波器结构相同,主要用来防止由于抽取带来的频谱混叠。脉冲抽取电路结构和功能与插值滤波中的并串转换相逆。

总结

针对典型的无线移动信道模型,本文提出一种简单多径信道模拟器的设计方法,给出了系统结构原理图和数字信号处理部分FPGA电路实现框图,并给出了FPGA主要模块的实现方法。在Altera Quartus平台上的仿真表明,当信号带宽为10MHz、A/D转换器工作在20MHz时,一块ALTERA APEX20K1000EBC652-1X单片FPGA可以完成6径的多径运算,时钟频率为40MHz,电路工作稳定。若采用更大的FPGA或专用集成电路,则可实现更复杂的信道模型。进行数字调制器设计时,若在数模转换前插入一片适当规模的FPGA,将上述信道模拟器数字处理部分嵌入其中,就可以在没有昂贵的信道模拟器的情况下对所设计系统进行信道实验。在Altera APEX20K600EBC652-1X上实现了对DVB-T调制器进行恒参数信道模拟,测试表明其效果与专用信道模拟器相当。

责任编辑:gt

-

FPGA

+关注

关注

1628文章

21725浏览量

602915 -

射频

+关注

关注

104文章

5572浏览量

167693 -

无线通信

+关注

关注

58文章

4562浏览量

143494

发布评论请先 登录

相关推荐

基于FPGA的飞行模拟器通信接口设计

宽带短波信道模拟器设计

IMT-2000基带实时信道模拟器设计

一种雷达回波信号模拟器的设计与实现

采用FPGA的振动模拟器设计

基于DSP和FPGA的多波形雷达回波中频模拟器实现

基于FPGA的无线信道模拟器的设计

一种基于FPGA嵌入式系统的雷达信号模拟器的实现

如何实现短波信道模拟器和实现计算机仿真的资料说明

基于APEX20K600EBC652-1X FPGA实现多径信道模拟器的设计

基于APEX20K600EBC652-1X FPGA实现多径信道模拟器的设计

评论