从20世纪30年代开始频率合成技术被人们认识,70多年来,频率合成技术有了较大的发展。频率合成是以一个或几个频率为基础,进行加、减、乘、除四则算术运算,合成出新的频率的一门技术。随着现代通信技术的迅速发展,雷达、宇航和遥控遥测技术的不断前进,越来越需要高频率稳定度、高频谱纯度、频率范围大的频率源,同时对频率合成的输出频率的个数等都有了越来越高的要求。

1 频率合成技术原理

频率合成的方法很多,最常用的频率合成技术有3种:直接频率合成、直接数字频率合成、锁相频率合成。

直接频率合成法是直接通过倍频器、分频器、混频器对基准频率进行加、减、乘、除等运算,以得到各种所需频率。其优点是频率转换速度快,并能产生任意小的频率增量。但他也存在一些不可克服的缺点,要求基准信号的功率较大,由于大量的倍频、混频、滤波等电路,合成器的设备十分复杂,而且输出端的谐波、噪声及寄生频率难以抑制。

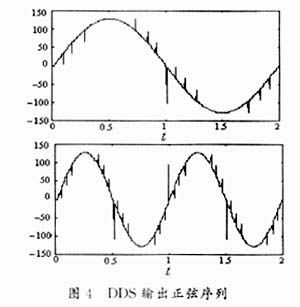

直接数字频率合成随着超高速数字电路的发展而兴起,主要是通过微处理器求解数学递推方程或者直接查正弦表得来,其输出波形是部分合成。其优点主要是分辨率高、控制灵活、容易做到比较低的频率,但是由于受器件的时钟频率控制,输出频率上限不能太高,而且总的输出噪声电平可能比较高。

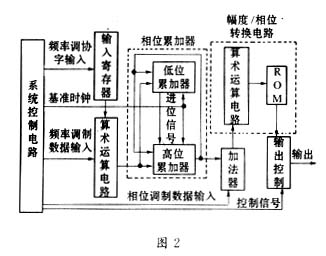

锁相频率合成技术是基于锁相环的同步原理,利用锁相环路的窄带跟踪特性得到不同的频率。锁相频率合成又有直接锁相和数字锁相2种。倍频器实际上就是直接锁相的一种,而数字锁相是在锁相环路中插入一个分频比可变的分频器,通过CPU控制可获得不同的频点。如图1所示是一个典型的直接式锁相环频率合成器的原理图。他由参考振荡源、参考分频器、锁相环3部分组成。

其中的锁相环与普通锁相环不同的是,他在VCO的输出端和鉴频器的输入端之间的反馈回路中加入了一个可变分频器。如图1所示,高稳定度的参考振荡源信号经R次分频后,得到频率为fR的参考脉冲信号。同时压控振荡器的输出经N次分频后得到频率为fN的脉冲信号,2个脉冲信号在鉴相器进行相位比较。当环路处于锁定状态时,则有输出信号:fo=N·fN=N·fR。

2 SystemView软件介绍

SystemView软件是美国ELANIX公司开发的用于视图化系统模型的设计、仿真、分析和评估的开发工具软件,采用了Windows环境下的图形化编程方式,具有友好、功能强大的调试环境,是真正信号级系统设计仿真的有力工具。

在SystemView环境下的操作比较简明,根据系统设计要求利用SystemView本身提供的各种函数图符建立仿真模型,并对其进行参数设置,在设定系统运行时间等参数后就可进行仿真分析。

3 数字频率合成器的设计与仿真

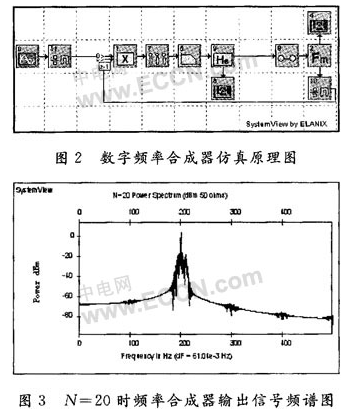

基于以上对数字频率合成器的分析,在SystemView设计环境下,建立了典型的数字频率合成器的模型,如图2所示。在此模型中,锁相环的VCO用FM图符(图符2)代替,其载波频率设置为195 Hz,增益为20 Hz/V,环路低通滤波器使用了一个8极点的贝塞尔低通滤波器,带通为5 Hz,分频器使用通信图符中的N倍分频器,根据锁相环的输出特性,若分频比N=20,则锁相环的输出频率fo应该锁定在fo=N·fR=20·fR频率上。

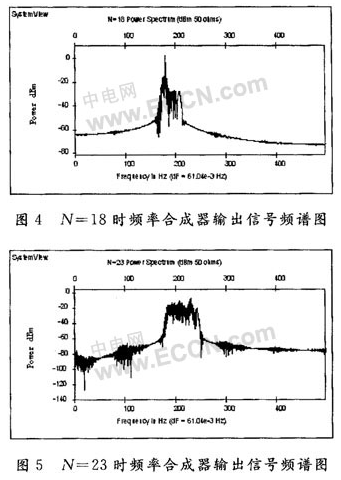

假设输人参考振荡器1 kHz,进行100分频后作为基准频率进入到数字频率合成器中,也即基准频率为fR=10 Hz,在系统时间参数设定为1 000 Hz,采样点数为16 384点情况下,对构建的系统进行仿真,当N=20时,由图3输出信号的频谱图可以看出,在频率为200 Hz处出现了较高的频谱能量峰值,这说明输出信号的频率被锁定在200 Hz。当把N改为18时,输出信号的频谱在频率为180 Hz附近处出现了能量高峰值,如图4所示,同理说明此时输出信号的频率处于锁定状态。

由以上仿真分析可以看出,改变N的值,输出信号的频率将变为基准频率10 Hz的整数倍。但事实上由于锁相环的锁定范围限制(与滤波器带宽和VCO的载波最大变化范围有关),只能输出VCO载波频率附近的几个整数倍的频率。当N=23时,输出信号频谱如图5所示,图中频谱能量高峰值并不像以上图示那么清晰,而是存在能量高峰区,由此说明输出信号频率比较平均地分布在180~240 Hz频带内,此时的锁相环处于失锁状态,频率合成器也失去了作用。因此,在进行分频比设置时,N值不能设置太高。在实际应用中,特别在超高频工作情况下,为获得较大范围的频率选择(较多的频率数)和较小的步进频率,多采用吞食脉冲式锁相环频率合成器。

4 结 语

通过运用SystemView仿真软件,构建了典型的数字频率合成器,仿真分析结果表明在滤波器带宽和VCO的载波最大变化范围内,可产生多个频率稳定的输出信号,目前在各种无线电台中使用的频率合成器普遍采用可变数字式锁相环频率合成器。

责任编辑:gt

-

频率合成器

+关注

关注

5文章

373浏览量

33991 -

微处理器

+关注

关注

11文章

2440浏览量

86266 -

分频器

+关注

关注

43文章

544浏览量

53854

发布评论请先 登录

AD9914BCPZ直接数字频率合成器

基于DDS的频率合成器设计介绍

什么是频率合成器

怎么设计直接数字频率合成器?

DDS直接数字频率合成器、信号发生器、函数发生器

直接数字频率合成器设计方法

FPGA实现的直接数字频率合成器

基于FPGA的直接数字频率合成器的设计和实现

基于FPGA的直接数字频率合成器的设计和实现

数字频率合成器的FPGA实现

直接数字频率合成器的实现设计方案

AD9910: 1 GSPS、14位、3.3 V CMOS直接数字频率合成器

基于开发工具软件实现数字频率合成器的设计与仿真

基于开发工具软件实现数字频率合成器的设计与仿真

评论