作者:Altera, ATEME, Mathworks

HDTV视频内容创作的繁荣以及在带宽受限的广播信道环境中传送这些视频内容的方法,不断催生新的视频压缩标准和相关视频图像处理设备。以前只有有线电视和卫星电视运营商提供视频传送业务,现在电信公司也对这一领域产生了兴趣,他们采用最新的视频编码/解码器(CODEC)和视频处理技术,并通过IPTV将数字视频发送给用户。

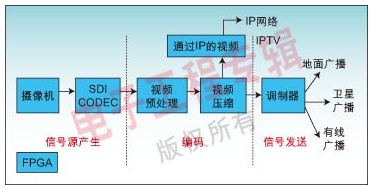

整个数字广播基础架构开始于电视工作室或摄影制作室的视频内容创作。创作过程接口使用串行数据接口(SDI)将原始视频发送到存储设备或某些类型的非线性编辑器(NLE),用于视频编辑和性能增强。编辑好的视频在编码时再用MPEG-2、JPEG2000或H.264进行压缩,然后通过电缆、卫星、地面广播或最新的IPTV技术网络发送给用户。图1给出了一个广播系统基础架构的组成框图。

视频和图像处理趋势

许多令人兴奋的新技术,如HDTV和数字影院都与视频和图像处理技术有关,并且这些技术还在飞速发展。图像捕获和显示器分辨率的跃升、高级压缩技术和视频智能都是这些技术发展的源动力。

先进的压缩技术正在全面替代以前的技术,它们有更好的流处理能力,在给定质量下有更高的压缩率,并且延迟更短。JPEG2000在存储和数字影院中也获得了很好的发展,在这些新的压缩解决方案得到实际应用之际,标准委员会还在不断增强H.264和JPEG2000的性能。

在过去十年中,数字电视广播中的标准清晰度电视(SDTV)一直采用的是MPEG-2标准。H.264-AVC(MPEG-4-Part10)和微软版的VC1将最终替代MPEG-2而成为SDTV和HDTV的最佳视频编码方法。为了满足目前和未来需要,广播设备制造商必须支持各种编码标准。除了各种核心视频CODEC标准外,还有一些不同类型的视频预处理和后处理算法可以用来增强整体图像质量。

随着分辨率和压缩率的不断提高,业界要求高性能同时保持架构的灵活性以实现快速升级。此外,随着技术的成熟和用量的上升,要求不断降低成本。由于可编程逻辑器件(PLD)可以为这些需求提供解决方案,因此可以在新兴的数字视频广播基础系统设备中发挥重要的作用。

图1:广播基础系统架构示意图

视频内容的产生

视频广播链的第一环是用专业数字视频摄像机捕捉音视频内容。视频可以是标清或高清。这种数字摄像机一般都有一个摄影与电视工程师协会(SMPTE)定义的SDI输出。SDI是一种未经压缩的视频流,速度可以是270Mbps(标清)、1.485Gbps(高清)或2.97Gbps(1,080p高清)。Altera公司的Stratix II GX FPGA自带串行/解串器(SERDES)和时钟/数据恢复(CDR)电路,可以用来处理摄像机SDI输出口上的视频流。

视频预处理/后处理

北美地区使用的电视广播标准NTSC中每个信道的带宽为固定的6MHz,欧洲和其他地区用的PAL标准中每个信道带宽为8MHz。这种带宽的限制规定远早于数字电视的出现时间,这种模拟带宽限制也影响到目前数字电视的广播标准。数字视频质量要比传统的模拟视频好得多,数字分辨率越高,传送或发送视频数据所需的带宽也越大。发送高质量视频需要对视频源进行预处理。

将视频压缩得太厉害会产生马赛克噪声或马赛克效应,这是由于基于块的CODEC的DCT引起的。视频经过预处理/后处理后,编码器压缩起来会更轻松,从而进一步提高图像质量,降低发送带宽要求。这一功能对有线、卫星、电信和IPTV广播商业模式来说特别重要,因为满足高质量要求必须在很窄的带宽约束下实现。一些预处理可能包括在视频进入编码器之前使用二维滤波技术削除某些高频分量,从而有效地减少马赛克噪声。Altera公司的视频与图像处理套件包括二维的有限脉冲响应(FIR)和中值滤波器功能。它们提供了一种灵活高效的方法,可以利用3×3、5×5或7×7恒定系数矩阵执行二维FIR滤波操作。因此,为了在带宽受限环境中获得最佳性能,预/后处理对任何视频压缩方法来说都是很关键的差异点。

视频压缩

下一步是在送往最终用户之前对经过预处理的原始视频数据进行压缩。从MPEG-1到MPEG-2,至今已经有了多代压缩标准,共有四种压缩方法:离散余弦变换(DCT)、矢量量化(VQ)、分形压缩(fractal compression)和离散小波变换(DWT)。

就数字电视而言,MPEG-2标准在全球范围内占据着主导地位,数字有线、卫星和地面广播都在使用这种标准。随着广播行业趋向于更高清晰度的内容,给定的传送带宽在适应规定的模拟带宽上承受着越来越大的压力。随着IPTV在传统电信有线系统上的兴起,用MPEG-2标准向用户传送视频节目无疑不再经济可行。

ITU-T视频编码专家组(VCEG)和ISO/IEC运动图像专家组(MPEG)开始力推MPEG4-Part 10(也称为H.264)标准。H.264可以比先前标准低得多的比特速率提供高品质的图像质量,在复杂性方面也不会有太大的提高。另外一个目标是让标准具有足够的灵活性,以适应各种应用场合(包括低比特率和高比特率以及低分辨率和高分辨率视频),并能在各种网络和系统上良好地工作。还有另外一些压缩标准(如JPEG2000),它们采用基于小波算法的状态技术。

视频发送

压缩后的视频可以在广播室内用ASI标准进行短距离的传送。业界的趋势是使用IP视频技术长距离发送视频数据。Altera公司提供的IP视频参考设计具有在IP网络上发送MPEG-2传输流(TS)的功能。该参考设计将一个或一个以上的压缩视频流桥接到100Mbps或1Gbps以太网上的IP包。同时,Altera还提供了ASI编码和译码参考设计。数字视频广播异步串口(DVB-ASI)是一种串行数据传输协议,用于在铜缆或光纤网络上传送MPEG-2数据包。

视频缩放和去隔行

创作室和前端设备通常需要为标清与高清之间相互转换等应用执行视频缩放和去隔行。其它应用还包括用于边缘检测处理的滤波器、垂直运动滤波器和场间运动滤波器等。

对许多专业影视室来说,最常见的要求之一是使用单个或多个显示器设备显示各种标准的SDTV或HDTV信号。利用遥控功能方便地在这些不同的视频源之间切换对创建专业、易用的系统来说至关重要,因此视频缩放和去隔行对视频切换设备/路由器(swticher/router)来说是很重要的,它能让切换设备/路由器处理不同类型的视频分辨率,方便进行视频切换、路由和本地显示。

色度空间转换和视频格式

由于广播商必须根据最终用户所处的不同地理位置提供不同的视频格式,因此广播创作室必须能够完成不同的色度空间和视频格式之间的转换。颜色一般用不同的色度空间域(color space domain)表示,每个空间域根据系统要求关联到不同的应用。颜色信息由两个独立的色度信号Cb和Cr决定,这两个信号还是第三个信号-亮度或照度信号Y的函数。RGB色度空间则由三个颜色分量-红、绿和蓝决定。当在使用不同色度空间模型的器件之间传送数据时,就需要进行色度空间转换。例如,将电视图像传送给计算机显示器,就需要将图像从YCbCr色度空间模型转换到RGB色度空间。相反,将图像从计算机显示器传送到电视机时就要求从RGB色度空间转换成YCbCr色度空间。Altera公司的色度空间转换器MegaCore功能就可以用来在各种应用场合下实现这些颜色转换。

视频和图像处理系统架构

系统架构可以选择标准单元ASIC、ASSP和可编程解决方案,如DSP或媒体处理器和FPGA。每种方法各有优缺点,最终取决于最终设备要求和解决方案的可用性。从上面讨论的趋势来看,理想架构需要具有以下一些特征:高性能、灵活性、易升级、低开发成本,以及随着应用的成熟和用量的增加,成本逐渐降低。

1. 高性能

性能不仅涉及压缩,而且与预处理和后处理功能有关。在许多实际应用中这些功能都比压缩算法本身占用更多的资源。这些功能包括缩放、去隔行、滤波和色度空间转换。广播市场对高性能的需求排除了只有处理器的架构方案,因为它们无法依靠单个器件满足性能要求。工作频率达1GHz的最先进DSP也无法完成H.264高清图像解码,而H.264高清编码的复杂度比解码要高出约10倍。FPGA是唯一可以解决这个问题的可编程解决方案。在某些情况下,最佳解决方案是FPGA和外部DSP处理器的组合。

2. 灵活性可以加快上市时间,方便升级

在技术飞速发展的同时,架构必须具有相当大的灵活性和易升级能力。由于标准单元ASIC和ASSP都没有这方面的特性,因此不能满足这种用途。通常针对批量非常大的消费类市场设计的ASSP很快会过时,因此对大多数应用来说使用ASSP的风险太大。

3. 低开发成本

算上掩模和晶圆、软件、设计验证和版图的成本,一个典型的90nm标准单元ASIC的开发成本将达到3,000万美元。只有最大批量的消费市场才能消化如此高的开发成本。在设计小批量设备时最好考虑FPGA,因为它不像ASSP那样需要固定确切的功能,即使最好的现成解决方案也存在很快过时的高风险。

Altera视频和图像处理解决方案

基于以上原因,FPGA特别适合许多视频和图像处理设备使用。Altera公司FPGA具有的以下一些特点:高性能、灵活性、低开发成本、防止过时、向低成本发展的结构化ASIC转变路径,以及Altera的视频和图像处理解决方案(包括DSP设计流程、Altera的视频和图像处理套件、接口和第三方视频压缩知识产权,以及视频参考设计)。

1. 在FPGA/结构化ASIC上实现类似ASSP的功能

随着解决方案数量的增加,Altera和合作伙伴已经可以在FPGA或结构化ASIC上提供ASSP功能。ATEME的H.264主类标准清晰度编码器产品就是一个很好的例子。通过这种产品用户可以像使用ASSP那样使用FPGA。与传统ASSP方法相比,FPGA解决方案可以快速更新,不存在过时的风险。

2. DSP设计流程

Altera公司针对定制开发提供了一个最优化的DSP设计流程,该流程允许用多种不同的方式表达设计,包括VHDL/Verilog、模型化设计和基于C语言的设计。Altera公司的视频与图像处理功能套件可以与这些设计流程选项中的任一种结合起来使用。

Altera和MathWorks合作创建了一个全面的DSP开发流程,能让设计师充分发挥MathWork公司模型化设计工具Simulink的作用。Altera的DSP Builder是一款DSP开发工具,用于连接Simulink和Altera公司先进的Quartus II开发软件。DSP Builder提供了一个无缝的设计流程,设计师可以在MATLAB软件中做算法开发,同时在Simulink软件中做系统级设计,然后将设计输出为硬件描述语言(HDL)文件供Quartus II软件使用。DSP Builder工具与SOPC Builder工具紧密集成在一起,可以帮助用户建立集Simulink设计、Altera的嵌入式处理器和知识产权内核于一身的系统。对在使用可编程逻辑设计软件方面没有很多经验的设计人员来说这种开发流程很直观,并且容易上手。

3. 视频和图像处理套件

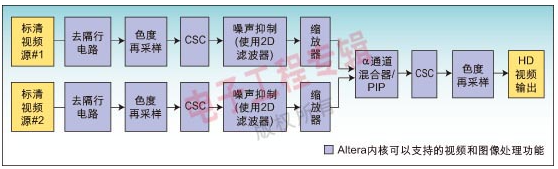

视频和图像处理套件由参数可以静态改变,某些情况下甚至可以动态改变的九大功能组成。采用视频与图像处理套件的一个典型视频系统如图2所示。

图2:采用视频与图像处理套件的一个典型视频系统框图

4. 视频开发套件

Altera公司有两个新的视频开发套件:一个是音视频开发套件Stratix II GX Edition,提供2个通道的复合视频输出、VGA输出口、96kHz的音频I/O、256MB的DDRII DRAM和Cyclone II器件;另外一个是视频开发套件Stratix II GX Edition,支持4通道的高清SDI、ASI、DVI、HDMI、USB、千兆以太网、1394和DDRII SDRAM。开发套件中还包含采用视频与图像处理套件、DSP Builder和SOPC Builder开发工具做的一个视频参考设计。除了这些套件外,还有多个用于视频解决方案的Altera第三方开发套件。

责任编辑:gt

-

FPGA

+关注

关注

1631文章

21808浏览量

606804 -

接口

+关注

关注

33文章

8742浏览量

152141 -

摄像机

+关注

关注

3文章

1629浏览量

60411

发布评论请先 登录

相关推荐

英特尔发布全球最大容量的全新Stratix 10 GX 10M FPGA

Altera Stratix V GX FPGA实现了与PCIe Gen3的兼容

国微思尔芯推采用Stratix 10 GX 10M FPGA的3亿门原型验证系统

Altera Stratix V GX FPGA开发板电路图

Stratix V GX FPGA开发套件,配置问题求助

Altera 40-nm Arria II GX FPGA转

Nios II处理器-世界上最通用的处理器

Altera率先实现Stratix V GX FPGA与PCIe Gen3交换机互操作

Stratix II GX FPGA的特点性能

如何设计Stratix II FPGA系统电源的详细资料概述

锆石FPGA A4_Nano开发板视频:NiOS II硬件框架结构深入剖析2

锆石FPGA A4_Nano开发板视频:NiOS II硬件框架结构深入剖析(2)

基于Stratix II GX FPGA实现广播系统的设计

基于Stratix II GX FPGA实现广播系统的设计

评论