引言

便携产品电源设计需要系统级思维,在开发由电池供电的设备时,诸如手机、MP3、PDA、PMP、DSC等低功耗产品,如果电源系统设计不合理,则会影响到整个系统的架构、产品的特性组合、元件的选择、软件的设计和功率分配架构等。同样,在系统设计中,也要从节省电池能量的角度出发多加考虑。

例如现在便携产品的处理器,一般都设有几个不同的工作状态,通过一系列不同的节能模式(空闲、睡眠、深度睡眠等)可减少对电池容量的消耗。即当用户的系统不需要最大处理能力时,处理器就会进入电源消耗较少的低功耗模式。带有使能控制的低压差线性稳压器(LDO)是不错的选择。

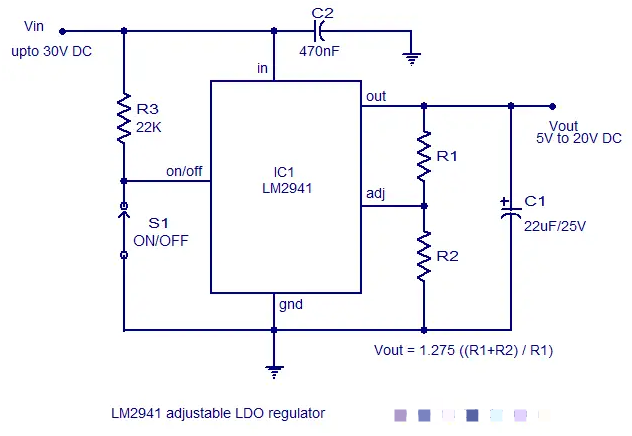

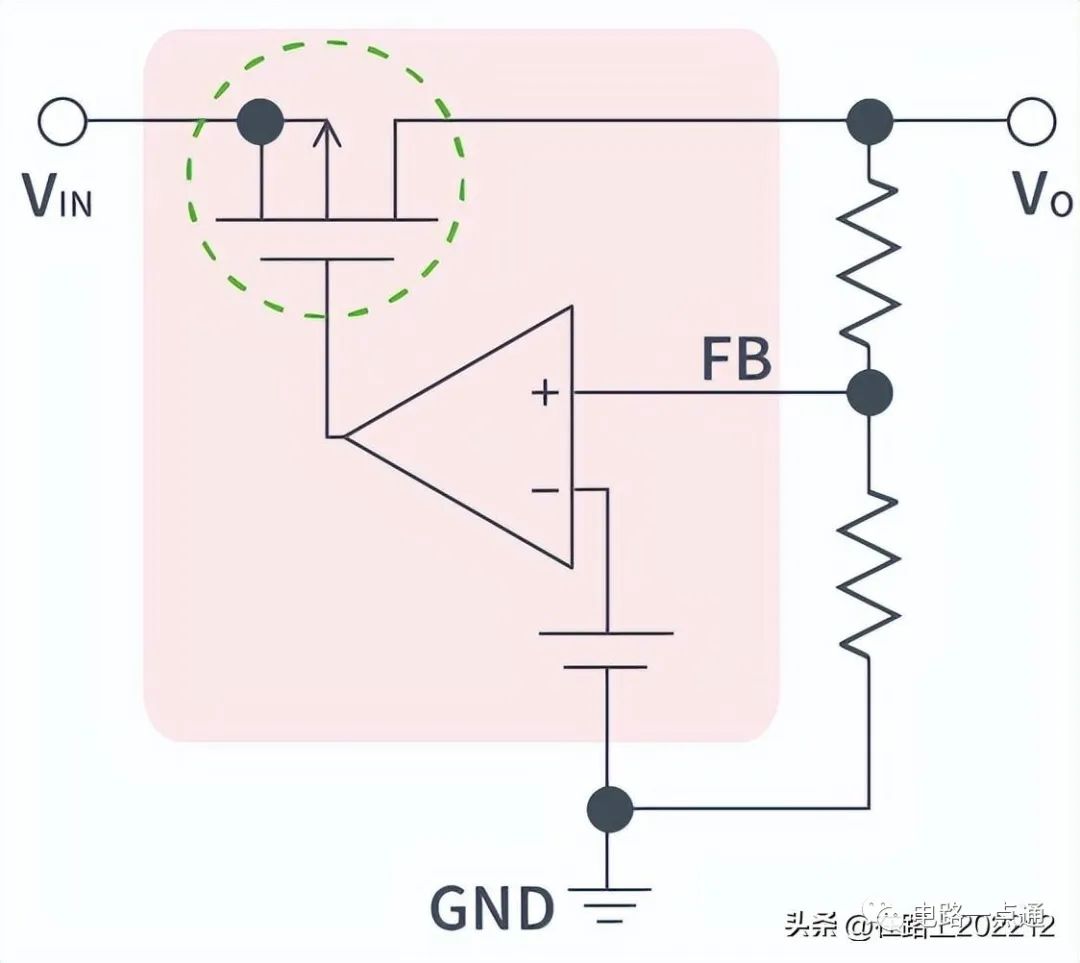

图1 LDO低压差线性稳压器的结构

LDO的基本原理

LDO是一种微功耗的低压差线性稳压器,它通常具有极低的自有噪声和较高的电源抑制比PSRR( Power Supply Rejection Ratio )。

LDO低压差线性稳压器的结构如图1,主要包括启动电路、恒流源偏置单元、使能电路、调整元件、基准源、误差放大器、反馈电阻网络,保护电路等,基本工作原理是这样的:系统加电,如果使能脚处于高电平时,电路开始启动,恒流源电路给整个电路提供偏置,基准源电压快速建立,输出随着输入不断上升,当输出即将达到规定值时,由反馈网络得到的输出反馈电压也接近于基准电压值,此时误差放大器将输出反馈电压和基准电压之间的误差小信号进行放大,再经调整管放大到输出,从而形成负反馈,保证了输出电压稳定在规定值上,同理如果输入电压变化或输出电流变化,这个闭环回路将使输出电压保持不变,即:

Vout=(R1+R2)/R2 * Vref

实际的低压差线性稳压器还具有如负载短路保护、过压关断、过热关断、反接保护等其它的功能。

电源抑制比(PSRR)

电源抑制比是反应LDO输出对输入纹波抑制能力的一个交流参数,一般输出和输入的频率是一样的,PSRR的值越大说明LDO的纹波能力越强,也就是说输入对输出的影响很小。和噪声(Noise)不同,噪声一般为在10Hz至100kHz频率范围内一定输入电压下其输出噪声电压的均方值(RMS),PSRR的单位是dB,公式如下。

PSRR=20 log(△vin/△vout)

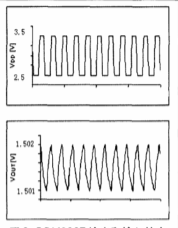

图2 为SGM2007在CBP = 0.1F, ILOAD = 50mA,COUT = 1F f = 10KHz,的输出和输入的电压曲线。

图2 SGM2007输出和输入的电压曲线

由公式PSRR=20 log(△vin/△vout)=60(dB),当输入变化了1V的时候,输出才变化了1mV.可见纹波抑制能力还是很强的。

圣邦微电子的SGM2007高性能低压差线性稳压器LDO在10Hz至100kHz频率范围内的输出噪声为30 V(RMS),在 1 kHz 的频率下电源抑制比(PSRR)高达73dB,它能够为诸如射频(RF)接收器和发送器、压控振荡器(VCO)和音频放大器等对噪声敏感的模拟电路的供电提供低噪声、高电源抑制比(PSRR)和快速瞬态响应,使能电路兼容TTL电平,适合数字于电路供电。SGM2007的输入电压在2.5V至5.5V之间,适合蓝牙数码相机和个人数字助理(PDA),以及诸如无线和高端音频产品等单个锂电池供电或固定3.3V和5V的系统。

提高PSRR的方法

BP 端加旁路电容

为降低基准噪声,提高LDO的PSRR,需要在LDO基准的输出端增加一路低通滤波器,滤波器可以集成在线性稳压器内部或由外部电路实现。内置滤波器占用了较大的管芯尺寸,增加芯片的设计和生产成本,有些低噪声LDO芯片只是提供一个基准的引脚BP(Bypass),用于连接基准旁路电容。

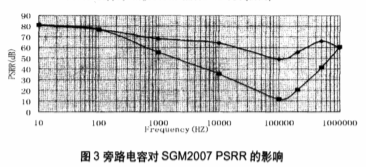

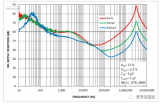

增大旁路电容,有利于减小输出噪声,提高LDO的PSRR。建议使用陶瓷电容的典型值为 470 pF 到 0.01 F 。也可使用此范围以外的电容,但会对输入电源上电时LDO 输出电压上升的速度产生影响,旁路电容值越大,输出电压上升速率越慢。在使用时这点要注意。如图3为旁路电容对SGM2007 PSRR影响,可见增大旁路电容会在一定频率上提高PSRR的值。

图3 旁路电容对SGM2007 PSRR的影响

增大LDO的输出电容

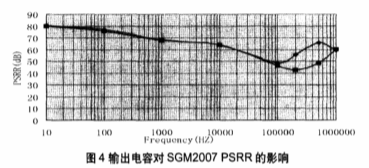

LDO需要增加外部输入和输出电容器。利用较低ESR的大电容器一般可以全面提高电源抑制比(PSRR)、噪声以及瞬态性能。 陶瓷电容器通常是首选,因为它们价格低而且故障模式是断路,相比之下钽电容器比较昂贵且其故障模式是短路。输出电容器的等效串联电阻(ESR)会影响其稳定性,陶瓷电容器具有较低的ESR,大概为10mΩ量级 采用陶瓷电容时,建议使用X5R 和X7R电介质材料,这是因为它们具有较好的温度稳定性。

如图4为输出电容对SGM2007 PSRR的影响。大电容器一般在一定频率范围内会提高电源抑制比(PSRR)减小LDO的负载电流。

图4 输出电容对SGM2007 PSRR的影响

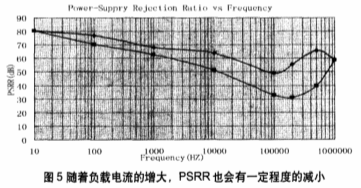

负载电流也会在一定程度上影响LDO的PSRR。如图为负载电流对SGM2007 PSRR影响,由图5可见随着负载电流的增大,PSRR也会有一定程度的减小。为了减小负载电流对LDO的PSRR影响,要尽量选择输出电流大的LDO。

图5 随着负载电流的增大,PSRR也会有一定程度的减小

大多数蜂窝电话基带芯片组需要三组电源:内部数字电路、模拟电路和外设接口电路。基带处理器(BB)的数字电路供电电压的典型值为1.8V至2.6V,一般情况下,Li+电池电压降至3.2V-3.3V时电话将被关闭,对于为基带处理器供电的LDO来说至少有500至600mV的压差,因此对压差要求不高。另外,数字电路本身对LDO的输出噪声和PSRR的要求也不高,而是要求LDO在轻载条件下具有极低的静态电流。

基带处理器内部模拟电路供电电压典型值是2.4V至3.0V,压差在200mV至600mV。要求LDO具有较高的低频(GSM电话为217Hz)纹波抑制能力,消除由RF功率放大器产生的电池电压纹波。

RF电路分为接收和发送两部分,供电电压典型值为2.6V至3.0V,其中低噪声放大器(LNA)、混频器、锁相环(PLL)、压控振荡器(VCO)和中频(IF)电路需要低噪声、高PSRR的LDO。

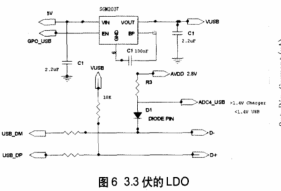

在USB电路中的应用

LDO广泛应用于诸如手机、MP3、PDA、PMP、DSC等便携设备中,当为便携设备的USB供电设计时,一般都是用到3.3伏的LDO如图6。很多便携设备在连接USB接口时,都要判断是为便携设备充电,还是连接USB设备进行数据传输,一般的设计方法是在LDO的Vout通过一个10K上拉电阻接到USB的D+.由另一部分电路判断当前的状态是充电(Charge)还是连接USB设备进行数据传输(Data)。如果LDO的Vout倒罐电流很大,也就是说,LDO的输出阻抗很小,那么LDO的Vout就会被强制拉低,那么便携设备就会判断不出是充电(Charge)还是连接USB设备进行数据传输(Data)。

图6 3.3伏的LDO

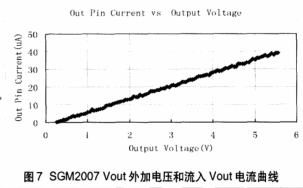

工程师在为便携设备USB供电选择时LDO要特别注意LDO Vout倒罐电流对电路的影响。有些LDO的Vout倒罐电流很大约为10mA,有些很小约为几十uA.如图7为圣邦微电子的SGM2007 在Vin=5V, En=0V, Vout外加电压和流入Vout电流的曲线。由曲线可见流入Vout的电流很小,在外加电压为5.5伏时,流入的电流才40uA。

图7 SGM2007 Vout外加电压和流入Vout电流曲线

结语

新型音频电路,如免提电话、游戏机、MP3及蜂窝电话中的多媒体电路,可能需要300mA-500mA的大电流LDO,LDO要在音频范围(20Hz至20kHz)应具有低噪声、高PSRR特性,以保证良好的音质。在为射频电路选择LDO时要慎重比较噪声指标,和电源抑制比(PSRR),确保旁路电容、输出电容和负载条件一致。

在为手机、MP3、PDA、PMP、DSC等便携设备的USB接口供电选择LDO时,一定要选择输出阻抗大,倒罐电流小的LDO。

编辑:jq

-

电流

+关注

关注

40文章

6882浏览量

132304 -

ldo

+关注

关注

35文章

1942浏览量

153494 -

DSC

+关注

关注

3文章

282浏览量

33630

发布评论请先 登录

相关推荐

超低噪声、高 PSRR、低压降线性稳压器 (LDO)TPS7H1111-SP和TPS111-SEP数据表

超低噪声、高PSRR、快速RF 200 mA 低压差线性稳压器系列数据表

1.5A 超低噪声、高PSRR耐辐射加固型低压降 (LDO) 线性稳压器数据表

超低噪声、高PSRR、快速、射频、500毫安 低压差线性稳压器数据表

关于低压差线性稳压器(LDO)的PSRR和在USB电路中的应用

关于低压差线性稳压器(LDO)的PSRR和在USB电路中的应用

评论