引言

目前国内数控机床中的伺服电机一般都是配套增量式编码器,而增量式编码器的精度并不太高且输出的是并行信号,欲提高其精度就必然要增大编码器的设计难度和增多并行信号的输出,这样就不利于伺服单元与编码器的长距离通信。而采用绝对式编码器,除了其精度比增量式编码器高几倍以外,其信号的输入输出都采用高速串行通信,节省了通信线路便于长距离的通信。在编码器的另一端,采用CPLD与绝对式编码器进行高速串行通信,CPLD再把收到的编码器信息转变为并行数据转送给伺服单元中的DSP进行运算控制。本文将给出CPLD与绝对式编码器高速串行通信的软硬件设计方案。

硬件设计

硬件主要由电源、CPLD及其外围电路和绝对式编码器接口电路三个模块组成。

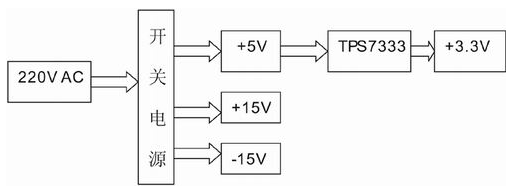

电源模块由开关电源电路和DC/DC电源芯片组成,如图1所示。

图1 电源结构框图

图中的开关电源将220V交流电网电压转变成+5V,+15V,-15V,开关电源可滤除电网中存在的各种干扰,并且开关电源中的变压器将220VAC与输出的+5V,+15V,-15V隔离开,内部电路还采用了TL431调节开关管的导通脉冲宽度,因此开关电源的抗干扰、安全性、稳定性及稳压程度都比较好。

TPS7333是DC/DC芯片,它将+5V的直流电压转变成+3.3V稳定直流电压供给CPLD使用,TPS7333转换效率、可靠性和稳压性都比较好,它在输入电压为+3.77V~+10V的电压范围内都能转换出+3.3V,使CPLD不受输入电压过高导致其烧坏。

CPLD及其外围电路模块

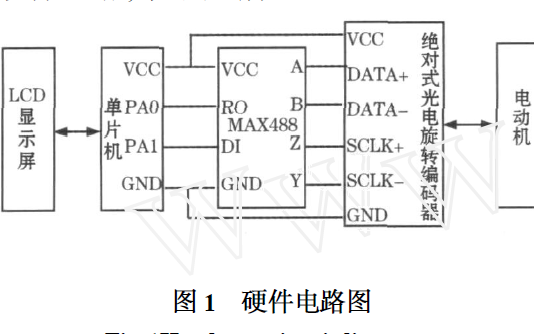

CPLD及其外围电路模块主要由CPLD、CPLD编程下载接口电路(JTAG接口)、DSP接口电路、有源晶振、电平转换电路和ADM485及其外围电路(负责与编码器通信的接口电路)组成(图2)。

图2 硬件整体结构框图

本设计CPLD采用Altera公司的EPM570T144C5,此芯片属于Altera公司的MAX II,MAX II相对MAX I成本更加低,功耗更加小,而器件的宏单元数更加多,且器件延时控制在6nS以内,具有很高的性价比。EPM570T144C5有570个宏单元数,芯片的引脚数目为144个,其中可用的I/O口有116个,因此此芯片的资源已经足够用。CPLD主要负责与绝对式编码器的高速串行通信,并受控于DSP的命令把接收到编码器数据和其他信息并行的转送给DSP。

JTAG接口主要用于下载可执行文件到CPLD,在PC机安装Altera公司的开发环境—QUARTUS II,并在此开发环境中将编写好的VHDL程序进行编译,保证编译不出错并且保证功能已实现后,连接好下载电缆到JTAG接口,通过QUARTUS II提供的编程下载工具,对CPLD电路板进行下载。

DSP接口就是由8根数据线、3根地址线和1根控制线组成的,8根数据线负责转送编码器数据及其其他信息,3根地址线负责转送DSP命令,在CPLD终端进行译码,CPLD根据译码得出的命令将编码器数据或其他信息通过8根数据线转送DSP,控制线主要是完成CPLD与DSP同步控制。

20M有源晶振主要是为CPLD提供基准时钟,在时钟信号的驱动下,供CPLD产生2.5Mb/s的波特率与编码器进行通信,和产生10MHz时钟供一些逻辑控制信号使用,此晶振提供20MHz的时钟频率,需要电源提供3.3V的直流电压。

电平转换电路主要负责将3.3V电压转换成5V或将5V电压转换成3.3V,因为CPLD的核和I/O口需要的供电电压都是3.3V,而ADM485和绝对式编码器所需要的供电电压和I/O口驱动电压都为5V,所以需要用电平转换芯片LVC4245A将3.3V转换成5V电压或将5V转换成3.3V。

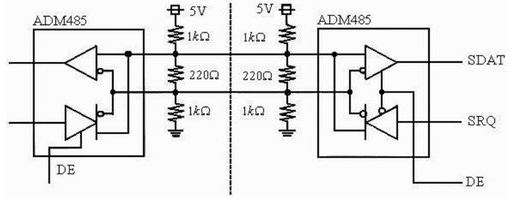

ADM485及其外围电路是CPLD与绝对式编码器高速通信的硬件衔接。ADM485工作电压为5V,其最大通信速率为5Mb/s,采用2个ADM485芯片进行对接通信可提高通信线路上的抗干扰能力,最长的转输距离可达1.2km。其外围电路如图3所示,虚线的右半部属于绝对式编码器的外部电路,上拉和下拉电阻都是1K欧姆,限流电阻则是220Ω,ADM485的SDAT是数据输出引脚,ADM485的SRQ是数据输入引脚,ADM485的DE是外部控制引脚,该脚受CPLD控制,由于RS-485通信协议属于半双工,所以ADM485只能处在发送数据或接收数据的状态,当ADM485的DE为高电平时,ADM485处于数据输出状态(即CPLD接收数据),当ADM485的DE为低电平时,ADM485处于数据输入状态(即CPLD发送数据)。

图3 绝对式编码器接口电路

绝对式编码器接口模块

绝对式编码器接口模块是指绝对式编码器内部的电源及信号输入输出接口电路,其电路与上述的ADM485及其外围电路是一致的,同样是采用ADM485芯片及一些上拉、下拉及限流电阻。如图3所示,虚线的左半部就是绝对式编码器内部接口电路,它负责与外部ADM485(虚线的右半部)衔接,ADM485受编码器内部的控制芯片所控制,当编码器收到CPLD发来的命令之后,控制芯片做出判断后发送出相应的数据,同时控制ADM485的DE为高电平,即使ADM485处于发送状态,当发送完数据之后,控制芯片又使ADM485的DE处于低电平状态,便于随时接收CPLD发来的命令。

软件设计

软件是指CPLD的VHDL程序,其主要由分频器、接收DSP控制命令、CPLD逻辑控制、波特率发生器、接收及发送数据和串并转换及发送数据六个软件子模块组成(图4)。

图4 软件整体结构框图

分频器模块

分频器模块主要是把20MHz的输入时钟频率分频为10MHz和2.5MHz的时钟频率,其中10MHz时钟主要是供给CPLD逻辑控制模块工作,2.5MHz时钟主要是供给波特率发生器模块工作。

接收DSP控制命令模块

接收DSP控制命令模块实际上是实时的采集DSP发来的控制信号并及时的将控制信号进行译码,译码完成后立即转送给CPLD逻辑控制模块。

CPLD逻辑控制模块

CPLD逻辑控制模块是整个CPLD软件的核心,其接收到译码数据后,立即做出逻辑控制运算,并快速地控制接收及发送数据模块和控制串并转换及发送数据模块。

波特率发生器模块

波特率发生器模块主要是为接收及发送数据模块提供2.5Mb/s波特率。

接收及发送数据模块

接收及发送数据模块是整个CPLD软件的重要组成部分,其主要负责与绝对式编码器高速通信,由于其通信方式是异步串行通信方式,因此其波特率、通信的数据格式及RS-485通信协议都要与绝对式编码器相同。

串并转换及发送数据模块

串并转换及发送数据模块主要是将接收到的编码器串行数据转换成并行数据,并将数据锁存在CPLD锁存器内,当CPLD逻辑控制模块控制其发送数据时,就将锁存在CPLD锁存器内的数据以并行的方式放送给DSP,供DSP进行运算控制用。

结语

本设计已经完成了硬件及软件的全部设计,读取带有绝对式编码器的电动机转子的任何一个位置数据只需31mS,通信速率可达2.5Mb/s。将本设计集成在伺服驱动单元中,驱动和控制电动机转数可达6000转/分,控制电动机转子的位置精度可达mM级。

责任编辑:gt

-

cpld

+关注

关注

32文章

1248浏览量

169344 -

编码器

+关注

关注

45文章

3641浏览量

134457 -

电机

+关注

关注

142文章

9010浏览量

145419

发布评论请先 登录

相关推荐

基于EPM570的可逆直流调速模块设计

可替代EPM570T144C5型号是什么型号的? 需要PIN2PIN兼容 EPM570T144C5近期会停产或者有停产计划吗?

请问STM32与CPLD通信有EPM570T144I5N芯片的datasheet吗?

基于 CPLD EPM570T100C5的通用直流调速模块设

基于EPM570T144C5和绝对式编码器实现电机串行通信的应用设计

基于EPM570T144C5和绝对式编码器实现电机串行通信的应用设计

评论